**Delft University of Technology**

## A Variable-Gain Low-Noise Transimpedance Amplifier for Miniature Ultrasound Probes

Kang, Eunchul; Tan, Mingliang; An, Jae-Sung; Chang, Zu-Yao; Vince, Philippe; Sénégond, Nicolas; Mateo, Tony; Meynier, Cyril; Pertijs, Michiel A.P.

DOI 10.1109/JSSC.2020.3023618

**Publication date** 2020

**Document Version** Accepted author manuscript

Published in IEEE Journal of Solid-State Circuits

**Citation (APA)** Kang, E., Tan, M., An, J.-S., Chang, Z.-Y., Vince, P., Sénégond, N., Mateo, T., Meynier, C., & Pertijs, M. A. P. (2020). A Variable-Gain Low-Noise Transimpedance Amplifier for Miniature Ultrasound Probes. *IEEE Journal of Solid-State Circuits*, *55*(12), 3157-3168. Article 9204362. https://doi.org/10.1109/JSSC.2020.3023618

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

**Copyright** Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A Variable-Gain Low-Noise Transimpedance Amplifier for Miniature Ultrasound Probes

Eunchul Kang<sup>10</sup>, *Member, IEEE*, Mingliang Tan<sup>10</sup>, *Student Member, IEEE*,

Jae-Sung An<sup>®</sup>, *Member, IEEE*, Zu-Yao Chang, Philippe Vince<sup>®</sup>, Nicolas Sénégond, Tony Mateo, Cyril Meynier, *Member, IEEE*, and Michiel A. P. Pertijs, *Senior Member, IEEE*

Abstract—This article presents a low-noise transimpedance amplifier (TIA) designed for miniature ultrasound probes. It provides continuously variable gain to compensate for the time-dependent attenuation of the received echo signal. This time-gain compensation (TGC) compresses the echo-signal dynamic range (DR) while avoiding imaging artifacts associated with discrete gain steps. Embedding the TGC function in the TIA reduces the output DR, saving power compared to prior solutions that apply TGC after the low-noise amplifier. The TIA employs a capacitive ladder feedback network and a current-steering circuit to obtain a linear-in-dB gain range of 37 dB. A variable-gain loop amplifier based on current-reuse stages maintains constant bandwidth in a power-efficient manner. The TIA has been integrated in a 64-channel ultrasound transceiver applicationspecific integrated circuit (ASIC) in a 180-nm BCDMOS process and occupies a die area of 0.12 mm<sup>2</sup>. It achieves a gain error below ±1 dB and a 1.7 pA/\_/Hz noise floor and consumes 5.2 mW from a  $\pm 0.9$  V supply. B-mode images of a tissue-mimicking phantom are presented that show the benefits of the TGC scheme.

*Index Terms*—Continuous gain control, time-gaincompensation (TGC), transimpedance amplifier (TIA), ultrasound application-specific integrated circuit (ASIC), ultrasound imaging.

#### I. INTRODUCTION

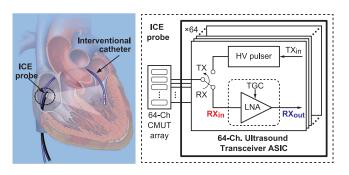

ULTRASOUND imaging is a safe and cost-effective tool for the diagnosis of medical conditions and the guidance of treatment. Size reduction of imaging devices has enabled ultrasound imaging from the tip of an mm-size catheter, for instance, for intracardiac echocardiography (ICE), as illustrated in Fig. 1(a) [1], [2]. Applications of ICE probes include guidance and monitoring of catheter ablation for the treatment of atrial fibrillation, guidance of closure of atrial septal defects, and guidance of transcatheter valve implantation [3], [4].

Manuscript received April 29, 2020; revised July 28, 2020; accepted September 1, 2020. This article was approved by Guest Editor David Blaauw. (*Corresponding author: Eunchul Kang.*)

Eunchul Kang was with the Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands. He is now with Sony Semiconductor Solutions, 1366 Lysaker, Norway (e-mail: e.kang@tudelft.nl).

Mingliang Tan, Jae-Sung An, Zu-Yao Chang, and Michiel A. P. Pertijs are with the Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands.

Philippe Vince, Nicolas Sénégond, Tony Mateo, and Cyril Meynier are with Advanced Research Group, 37038 Tours, France.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2020.3023618

Fig. 1. (a) Application scenario of an ICE probe. (b) Block diagram of the transceiver ASIC with the proposed TIA.

ICE probes, and other miniature ultrasound probes alike, employ an array of ultrasound transducer elements to transmit ultrasonic pulses and record the resulting echo signals, from which an image is reconstructed using beamforming techniques [5]. In many probes, each transducer element is electrically connected via a cable to the external imaging system [5]–[7]. However, this approach limits the number of transducer elements due to the limited number of cables that can be accommodated and results in signal attenuation due to the fact that the cables load the elements. Increasingly, application-specific integrated circuits (ASICs) are integrated in the probe close to the transducer array to address these issues [8]–[13].

Fig. 1(b) shows a block diagram of the front end of such an in-probe ASIC. For each transducer element, it contains transmit (TX) and receive (RX) circuitry. The former tends to include a high-voltage (HV) pulser that drives the element to generate a pressure wave [8]–[11]. At the start of the RX signal path, a low-noise amplifier (LNA) amplifies the echo signal so that it can be further processed by the following circuitry, which may involve beamforming, multiplexing, and digitization [12], [13].

An important function in the RX signal path is time-gain compensation (TGC), which reduces the echo-signal dynamic range (DR) by compensating for the propagation attenuation experienced by the acoustic waves as they travel through the body [14]. Due to this attenuation, echo signals from deep tissue, which need to travel longer than echoes from nearby structures and, therefore, arrive later, are more attenuated.

0018-9200 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

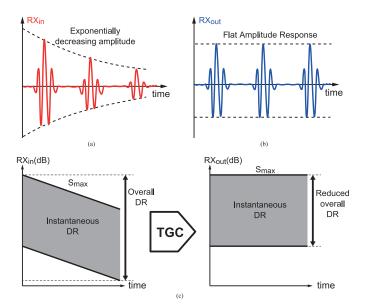

Fig. 2. (a) RX signal before TGC. (b) RX signal after TGC. (c) RX input and output signal range as a function of time with ideal TGC.

Fig. 3. (a) Block diagram of the conventional solution of an LNA followed by a TGC amplifier. (b) Block diagram of the proposed LNA with embedded TGC function.

This leads to an exponential decrease in echo amplitude with time, as illustrated in Fig. 2(a). Since propagation attenuation increases with frequency [14], this is particularly significant at the relatively high frequencies (>5 MHz) typically used in miniature probes. The attenuation may amount to 40 dB at the largest imaging depth. It can be compensated for by providing a gain that increases linearly in decibels as a function of time, thus providing a uniform echo amplitude across depth, as illustrated in Fig. 2(b).

The impact of the TGC on the signal DR is further illustrated in Fig. 2(c), which shows how the range of echo-signal levels (the instantaneous DR) varies as a function of time (or, equivalently, depth) before and after the TGC, demonstrating that the time-dependent attenuation is corrected for, thus reducing the overall DR to a level similar to the instantaneous DR. In conventional ultrasound systems, the TGC is typically performed after the LNA [15], as shown in Fig. 3(a), implying that a power-hungry LNA is required that is capable of handling the full DR of the echo signal at its output.

In this article, we present an LNA with a built-in continuous TGC function that mitigates this problem, as shown in Fig. 3(b) [16]. The LNA is a transimpedance amplifier (TIA) optimized to amplify the signal current of a capacitive micro-machined ultrasound transducer (CMUT). We demonstrate its integration into a 64-channel ASIC for a CMUT-based ICE probe, as shown in Fig. 1(b). While the

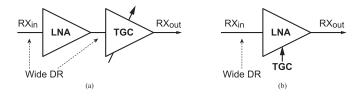

Fig. 4. Circuits to realize the TGC. (a) Amplifier with discrete gain steps [17]–[21]. (b) Amplifier with time-varying biasing [24]. (c) Amplifier that interpolates between the outputs of a resistive ladder attenuator [29]. (d) Amplifier using a feedback network with MOS variable resistors [23].

LNA has been designed for application in an ICE probe, the presented amplifier architecture is applicable to ultrasound front ends for miniature ultrasound probes in general.

This article is organized as follows. Section II reviews the existing approaches for the TGC. Section III describes the proposed TIA architecture. The circuit implementation details of the TIA are presented in Section IV. Electrical measurements and imaging experiments are presented in Section V. This article ends with a comparison with the state-of-the-art and conclusions.

### II. COMPARISON OF TGC CIRCUITS

Various approaches have been taken to realize the amplifiers suitable for the TGC. They can globally be divided into two groups: amplifiers with discrete gain steps and amplifiers with continuous gain control.

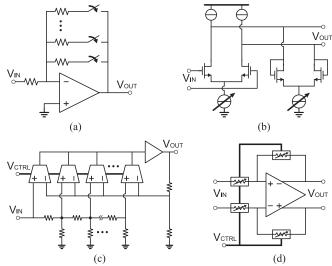

Amplifiers with discrete gain steps approximate the ideal exponentially varying gain by a number of discrete gain steps that are sequentially applied. An important advantage of this approach is that the gain steps can be accurately defined by means of a digitally programmable resistive feedback network, as illustrated in Fig. 4(a) [17]–[21], a digitally programmable capacitive feedback network [12], [13], [22], or a digitally programmable current-steering feedback network [23]. Moreover, the gain steps can be divided among multiple amplifier stages, with course gain steps realized in the LNA at the input of the receive signal path, which enables the realization of highly power-efficient amplifiers [12], [19]. Switching from one discrete gain step to the next, however, is typically associated with a switching transient that can lead to artifacts in the ultrasound image at a depth that corresponds to the gain-switching moment. Such artifacts can be made negligible by making the gain steps small [20], but this requires a large number of gain steps to cover the gain range, leading to a complex circuit that requires substantial die area.

Amplifiers with continuous gain control are also referred to as variable-gain amplifiers (VGAs) and typically have a gain that can be set by an analog control input, typically a control voltage. The gain tends to depend (approximately) exponentially on the control voltage, giving a linear-in-dB gain control. By ramping the control voltage linearly as a function of time, the gain can be swept across a desired range to realize the TGC without the disadvantages associated with discrete gain steps. The many ways in which this can be realized can be roughly divided into two categories: amplifiers with an approximately exponential transfer function and amplifiers with interpolation between discrete gain steps.

Amplifiers with an approximately exponential transfer function typically exploit the non-linear characteristics of MOS or bipolar transistors to realize the variable gain. This can be done, for instance, by changing the operating point of a differential pair as a function of a gain-control voltage, leading to a variable transconductance. Combined with a load with an impedance that is also dependent on the control voltage, for instance, by changing the operating point of diodeconnected transistors as a function of the same control voltage, an amplifier with a non-linear transfer function is obtained, as shown in Fig. 4(b) [24], [25]. However, this non-linear transfer function only approximates an exponential across a limited gain range and tends to be sensitive to process, supply voltage, and temperature (PVT) variations. Multiple stages can be cascaded to extend the range [26], [27].

Another approach to approximate an exponential transfer function is to use the exponentially increasing output voltage of a positive-feedback amplifier during a well-defined time window [28]. This approach, however, requires that the signal is sampled at the amplifier's input, allowing each successive sample to be amplified using the positive-feedback amplifier, and the gain to be varied from sample to sample by changing the positive-feedback time window.

A TGC amplifier topology with interpolation between discrete gain steps has been reported in [29] and [30]. As illustrated in Fig. 4(c), the input signal is attenuated by a resistive ladder network, each section of which provides a fixed attenuation step in decibels. These attenuated signals are fed to an amplifier with multiple input stages, the bias currents of which are controlled in order to gradually change from one step to the next. Another topology that employs multiple inputs stages with controlled biasing has been reported in [31], where the attenuating network is part of the feedback of the amplifier, and the input stages directly connect to the input in order to provide not only the variable gain but also simultaneously varying the input noise and signal swing.

Interpolation between discrete gain steps can also be achieved by smoothly changing the components values in a passive attenuator network by including MOS transistors that act as variable resistors, as illustrated in Fig. 4(d) [23], [32]. Special biasing circuits are needed in order to mitigate the PVT dependence.

The third approach to achieve interpolation between discrete gain steps is to use a differential pair as a current-steering device. In [33], a differential pair at the output of an amplifier directs a fraction of the output current back to the input and

Fig. 5. Simplified circuit diagram of the proposed TIA with a fixed-gain capacitive feedback network.

a fraction toward the output. Thus, the current gain of this amplifier can be continuously controlled through the voltage applied to the differential pair. In an amplifier with two parallel input stages, Onet *et al.* [34] used current steering to control how much of the output current of the current produced by these input stages is added to the output.

Compared to the prior art, the amplifier proposed in this work has three appealing features. First, it provides continuous TGC, avoiding the switching artifacts associated with discrete gain steps. Second, as the TGC function is realized in the LNA, it does not rely on a preceding (fixed-gain) LNA to obtain a good noise figure and/or to obtain a suitable input impedance, like in, e.g., [23], [29], [30], and [35]. Such a fixed-gain LNA has an output DR that equals the large input DR, which tends to be associated with additional power consumption in the output stage to achieve acceptable distortion at the largest signal levels, or with additional power consumption to reduce the noise in the stage after the LNA if the LNA's gain is kept limited to avoid distortion. Third, as it relies on capacitor ratios to define the gain, it avoids the additional noise associated with a resistive feedback network and the PVT dependence of approaches that rely on non-linear device characteristics.

#### III. ARCHITECTURE OF THE TIA WITH THE TGC

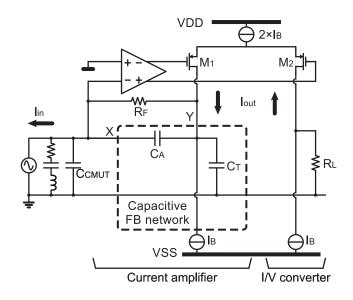

#### A. Current Amplifier-Based TIA

As mentioned, the proposed TIA has been designed to interface with a CMUT transducer. Such a transducer consists of a flexible micro-machined membrane that forms one of the electrodes of a parallel-plate capacitor. In response to an incoming pressure wave, the membrane is moving, leading to a small change in the capacitance. When the CMUT is DC biased, this change can be detected as a signal current [36]. The CMUT can then be modeled as a signal-current source  $I_{in}$  shunted by a capacitance  $C_{CMUT}$  modeling the transducer's electrical capacitance and a resonator representing its mechanical resonance, as shown in Fig. 5. The transducer

used in this work is operated at 5 MHz and has a capacitance of 15 pF.

To detect the signal current, an LNA with low input impedance is needed, making a TIA is a suitable choice [37]. In this work, an input-referred noise level of 2 pA/ $\sqrt{Hz}$ and a maximum signal current of 100  $\mu$ A are targeted. A TIA with resistive feedback is commonly used [38] but does not readily support the widely variable gain needed for the TGC. Moreover, resistive feedback contributes additional noise.

Therefore, instead, we use a TIA based on a current amplifier with capacitive feedback as a starting point, based on [39]. As shown in Fig. 5, this TIA consists of a current amplifier with a gain defined by capacitors  $C_A$  and  $C_T$ , followed by a resistive load  $R_L$  that turns the amplified current into an output voltage. A high-ohmic feedback resistor  $R_F$  serves to set the dc operating point and plays a negligible role at the signal frequencies of interest. A loop amplifier senses the input voltage  $V_X$  so as to maintain a virtual ground at the input. As a result, the input current  $I_{in}$  is integrated on capacitor  $C_A$ , leading to a voltage  $V_Y$  across capacitor  $C_T$ , and an amplified output current

$$I_{\rm OUT} = \left(1 + \frac{C_{\rm T}}{C_{\rm A}}\right) I_{\rm IN} = \alpha I_{\rm IN}.$$

(1)

Thus, the circuit provides a current gain of  $\alpha = 1 + C_T/C_A$ . We use this current gain mechanism to implement the required 40 dB gain range, as will be discussed shortly.

Contrary to [39], in which a single-ended loop amplifier and a source follower with a resistive load are used, we employ a fully differential loop amplifier and a differential pair ( $M_1$ and  $M_2$ ) that provides equal currents of opposite polarity to the feedback network and to  $R_L$  to convert the amplified current to an output voltage. To avoid clipping, the bias current  $I_B$  should be larger than the maximum amplified current. The resulting overall transimpedance is  $(1 + C_T/C_A)R_L$ . This differential topology helps to reduce the power-supply sensitivity and increases the output voltage headroom.

#### B. Capacitive Ladder Feedback Network

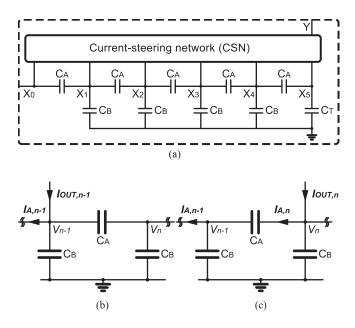

Although variable gain could be realized by adjusting  $C_T/C_A$ , this would require a large capacitor ratio to achieve a 40 dB range and dense gain steps to minimize the switching artifacts between the gain steps. This would be unattractive in terms of die size and complexity. Therefore, as shown in Fig. 6(a), we realize gain steps covering a wide range by means of a ladder structure and then interpolate between these steps by means of a current-steering network (CSN).

Ignoring the interpolation for now, let us assume that the feedback node *Y* is connected to one of the nodes of the ladder network  $X_n$  ( $0 \le n \le 5$  in our design). The ladder capacitors  $C_A$ ,  $C_B$ , and  $C_T$  are dimensioned such that the capacitance to ground at each node  $X_n$  equals  $C_T$ , which implies

$$C_{\rm B} + \frac{C_{\rm A}C_{\rm T}}{C_{\rm A} + C_{\rm T}} = C_{\rm T} \Rightarrow C_{\rm B} = \frac{C_{\rm T}^2}{C_{\rm A} + C_{\rm T}}.$$

(2)

We will now show that this choice causes every ladder section to contribute an additional gain factor  $\alpha = 1 + C_T/C_A$ .

Fig. 6. (a) Capacitive ladder feedback network with CSN to realize the variable gain. Arbitrary section of the ladder network, with a feedback connection to (b) node n - 1 and (c) node n.

If the feedback is connected to node  $X_0$ , the output current  $I_{OUT,0}$  equals  $I_{IN}$ , corresponding to a gain of 1 ( $\alpha = \alpha^0$ ). The ladder network then merely forms an additional capacitive load at the input. If the feedback is connected to  $X_1$ , the topology is the same as in Fig. 5, and the output current equals  $\alpha I_{OUT,1} = I_{IN}$ .

Now consider a feedback connection to an arbitrary node  $X_{n-1}$ , associated with an output current  $I_{OUT,n-1}$ , as shown in Fig. 6(b), and a feedback connection to the next node  $X_n$ , with the output current  $I_{OUT,n}$ , as shown in Fig. 6(c). Given that the feedback network is a linear passive network, the current  $I_{A,n-1}$  flowing back toward the input and the voltage  $V_{n-1}$  at node  $X_{n-1}$  must be equal, implying

$$I_{A,n-1} = I_{\text{OUT},n-1} - sC_{\text{T}}V_{n-1} = I_{A,n} - sC_{\text{B}}V_{n-1}$$

(3)

where  $I_{A,n}$  is the current flowing in Fig. 6(c) through the capacitor  $C_A$  connecting node  $X_{n-1}$  to node  $X_n$ . This current can also be expressed in terms of  $I_{OUT,n}$ :

$$I_{A,n} = \frac{C_{\rm A}}{C_{\rm A} + C_{\rm T}} I_{\rm OUT,n} - s \frac{C_{\rm A} C_{\rm T}}{C_{\rm A} + C_{\rm T}} V_{n-1}$$

(4)

where the first term represents the fraction of  $I_{\text{OUT},n}$  that would flow to node  $X_{n-1}$  if  $V_{n-1}$  would be zero, and the second term represents the current flowing from node  $X_{n-1}$  to node  $X_n$  if  $I_{\text{OUT},n}$  would be zero. Substituting (2) and (4) into (3) gives

$$I_{\text{OUT},n} = \left(1 + \frac{C_{\text{T}}}{C_{\text{A}}}\right) I_{\text{OUT},n-1} = \alpha I_{\text{OUT},n-1}$$

(5)

which proves by induction that  $I_{OUT,n} = \alpha^n I_{IN}$ .

Thus, by an appropriate choice of the capacitor values, exponential gain steps can be realized without requiring large capacitor ratios. In our implementation, we adopted a five-section ladder network with  $\alpha = 2.5$  (i.e., gain steps of 8 dB covering 40 dB) realized using integer multiples of a unit capacitor  $C_{\rm U}$ :  $C_{\rm A} = 10C_{\rm U}$ ,  $C_{\rm B} = 9C_{\rm U}$ , and  $C_{\rm T} = 15C_{\rm U}$ .

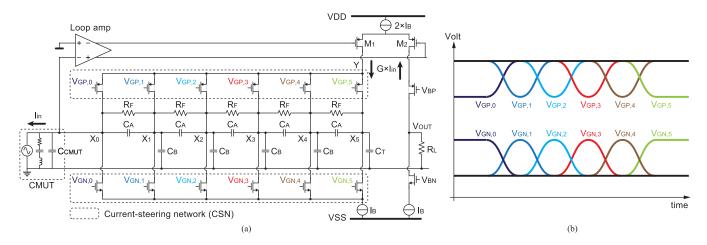

Fig. 7. (a) Circuit diagram of the proposed TIA. (b) Gate-control voltages for the CSNs for continuous gain control.

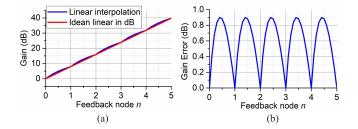

Fig. 8. (a) Gain as a function of the selected feedback node  $X_n$  for linear interpolation and for an ideal linear-in-dB curve. (b) Corresponding gain error relative to the linear-in-dB curve.

This allows for a compact and well-matched layout. The value of  $C_{\rm U}$  should be sufficient to keep the voltage swing in the network limited and to make the impact of parasitic capacitance on the gain negligible. We use 0.3 pF to limit the swing to 360 mV at a maximum  $I_{\rm IN}$  of 100  $\mu$ A at 5 MHz.

#### C. Interpolation by means of Current Steering

To interpolate between the gain steps of the ladder network, we propose a CSN as shown in Fig. 7(a). A set of PMOS transistors directs the feedback current at node Y to the ladder nodes  $X_n$ . The feedback current is initially steered completely to the input node  $X_0$ , by providing a lower gate voltage  $V_{GP,0}$ to the corresponding PMOS transistor, as shown in Fig. 7(b). The feedback current then gradually shifts from node to node, by alternately pulling down the gate voltages  $V_{GP,n}$ , effectively linearly interpolating between the exponential gain steps of the ladder network. Finally, the feedback current is steered entirely to the last tap, providing maximum gain. To bias the circuit, a complementary NMOS CSN, with similar complementary gate-drive voltages  $V_{GN,n}$ , steers a bias current  $I_B$  to the nodes of the feedback network. High-ohmic resistors  $R_{\rm F}$  in the feedback network prevent charge accumulation due to small current differences between the CSNs, without affecting the in-band AC current gain.

The CSN provides an approximately linear interpolation between exponential gain steps. The resulting error with respect to an ideal linear-in-dB (exponential) gain curve is shown in Fig. 8. A ladder network consisting of five sections with a gain step of 8 dB each has been chosen to achieve a gain error less than 1 dB, in line with the requirements of the imaging application. This can be reduced by increasing the number of ladder sections. Note that the sharp dips in the gain-error curve in Fig. 8(b) are due to the ideal linear interpolation applied. The actual implementation using PMOS transistors and smoothly varying gate voltages as illustrated in Fig. 7(b) will lead to less sharp transitions in the gain-error curve.

### D. Noise Analysis

To be able to detect the smallest echo signals at the highest gain, the TIA's noise contribution should not exceed that of the transducer. At the high end of the gain range, the noise contribution of the load resistor, the output differential pair, and the bias-current sources are negligible, because they are attenuated by the 40 dB current gain when referred to the input. The feedback network, due to its capacitive nature, does not contribute in-band noise. This leaves the loop amplifier as the dominant noise source. Its input-referred voltage noise appears at the virtual ground and leads to an equivalent input current noise due to the total impedance to ground at the input. This impedance is dominated in our design by the CMUT capacitance of about 15 pF and amounts to about 2 k $\Omega$  at 5 MHz. To achieve an equivalent input current noise below 1.5 pA/ $\sqrt{Hz}$ , the loop amplifier's input voltage noise should be below 3 nV/ $\sqrt{Hz}$ . Note that this noise level only needs to be achieved at the highest gain level. At lower gain levels, the input signal is bigger, and so proportionally larger noise can be accepted without loss of signal-to-noise ratio (SNR). Achieving this noise level in a power-efficient manner is one of the key design objectives for the loop amplifier implementation, as will be elaborated in Section IV.

#### **IV. CIRCUIT IMPLEMENTATION**

#### A. Gain-Control Circuit

To generate the gate-control voltages  $V_{\text{GP},n}$  and  $V_{\text{GN},n}$  for the CSNs in Fig. 7(b), an external gain-control voltage  $V_{\text{TGC}}$

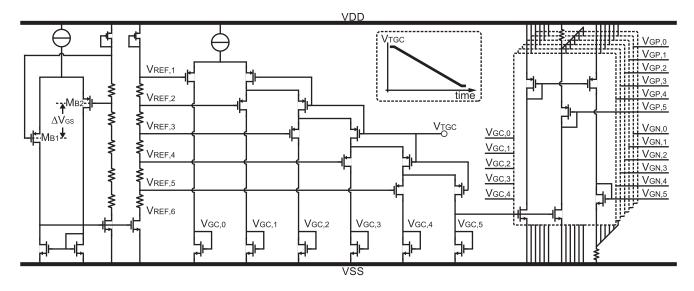

Fig. 9. Circuit diagram of the gain control circuit.

is compared to a set of reference voltages generated using a stack of cascaded PMOS differential pairs, as shown in Fig. 9. The reference voltages  $V_{\text{REF},i}$  are generated using a resistive divider. Thus, as  $V_{\text{TGC}}$  is swept, the tail current is steered from drain to drain. The drain currents are mirrored to diode-connected PMOS and NMOS transistors at appropriate common-mode levels to generate  $V_{\text{GP},n}$  and  $V_{\text{GN},n}$ , respectively, resulting in the voltages shown in Fig. 7(b) when  $V_{\text{TGC}}$  is linearly ramped down.

In this circuit, all PMOS differential pairs have identical sizes and have bulk connections to the source to mitigate the body effect. The bias current of the gain-control circuit is chosen such that the bandwidth of the circuit is sufficient to track the required  $V_{\text{TGC}}$  transient, while avoiding excess bandwidth, as this would add undesired in-band noise to the signal path. The bias current for the resistive ladder is generated using the bias circuit shown in the left-hand side of Fig. 9. This bias circuit employs a feedback loop to generate a current proportional to the difference in gate–source voltage  $\Delta V_{\text{GS}}$  of ratioed PMOS transistors  $M_{\text{B1}}$  and  $M_{\text{B2}}$ . The bias circuit employs a replica of the resistive ladder, so that the voltage steps between the reference voltages equal  $\Delta V_{\text{GS}}$ , making the current division in the PMOS differential pairs as a function of  $V_{\text{TGC}}$  insensitive to process and supply variations.

### B. Loop Amplifier Design

A key challenge in the design of the loop amplifier is to maintain sufficient loop gain in the presence of the widely varying current gain. We analyze the loop gain by breaking the feedback loop at the input of the loop amplifier. The resulting loop-gain  $A_{LP}(\omega)$  consists of the product of the loop amplifier's voltage gain  $A_{amp}(\omega)$  and the transfer function from the output of the loop amplifier back to the input

$$A_{\rm LP}(\omega) = A_{\rm amp}(\omega) \cdot \frac{g_{m,\rm out}\beta}{j\omega C_{\rm IN}} \tag{6}$$

where  $g_{m,out}$  is the transconductance of the differential pair  $M_{1,2}$  (see Fig. 5),  $\beta$  is the fraction of that differential pair's

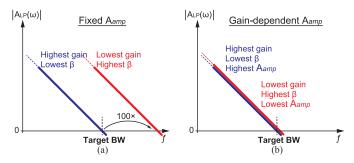

Fig. 10. Magnitude of the loop gain as a function of frequency, showing (a) strongly gain-dependent unity-gain frequency for a fixed-gain loop amplifier and (b) constant unity-gain frequency for a loop amplifier with variable gain.

output current that makes it back to the input, and  $C_{\rm IN}$  is the total capacitance at the input, which is dominated by the CMUT capacitance  $C_{\text{CMUT}}$ . The fraction  $\beta$  is related to the closed-loop current gain, which in Section III-B has been shown to be  $\alpha^n$ . Although the closed-loop current gain is independent of  $C_{IN}$ , because  $C_{IN}$  is at the virtual ground in the closed-loop configuration,  $C_{\rm IN}$  does influence the fraction  $\beta$ . However, if  $C_{\rm IN} \gg C_{\rm T}$ , we can approximate the input as being shorted to ground by  $C_{IN}$ , and the factor  $\beta$  is then by good approximation, the inverse of the current gain  $\alpha^n$ . If we assume that the loop amplifier has a constant gain and a wide bandwidth, i.e., that  $A_{amp}(\omega)$  is constant across the frequency range of interest, this implies that for a 40 dB variation in current gain, the unity-gain frequency of  $A_{LP}(\omega)$ , which sets the closed-loop 3-dB bandwidth, would vary by a factor 100, as illustrated in Fig. 10(a). In order to achieve enough bandwidth at the highest current gain, which corresponds to the lowest  $\beta$ , we would obtain a bandwidth that is 100 times larger than needed at the lowest current gain, which corresponds to the highest  $\beta$ . To realize this, the loop amplifier would need to have an unrealistically wide bandwidth.

Therefore, instead, we employ a loop amplifier whose gain  $A_{amp}(\omega)$  is adjusted to compensate for the varying  $\beta$ .

KANG et al.: VARIABLE-GAIN LOW-NOISE TIA FOR MINIATURE ULTRASOUND PROBES

Fig. 11. Circuit diagram of the loop amplifier.

For the highest current gain (i.e., the lowest  $\beta$ ), we make the dc gain of the loop amplifier roughly 100 times higher than for the lowest current gain (i.e., the highest  $\beta$ ). This gives the loop an approximately constant unity-gain frequency, corresponding to an approximately constant closed-loop 3-dB bandwidth, as illustrated in Fig. 10(b). Any poles in the loop amplifier should be sufficiently above this frequency to maintain stability.

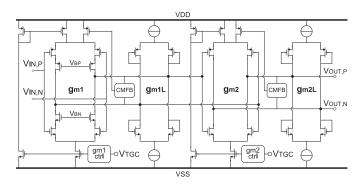

Since the required gain-bandwidth product of the loop amplifier is hard to realize with a single-stage amplifier, we use a cascade of two stages, as shown in Fig. 11. A fully differential amplifier structure is adopted. The first stage consists of a current-reuse input stage with diode-connected load transistors, resulting in a gain set by the transconductance ratio  $g_{m1}/g_{m1L}$ . The transconductance of the input stage  $g_{m1}$ is defined by the tail current, which is shared by the NMOS and PMOS pair to improve the power efficiency [40]. This tail current is varied as a function of the gain-control voltage  $V_{\text{TGC}}$  (details provided in Section IV-C) to obtain the required variable gain. Besides maintaining constant bandwidth, this scheme also saves power, by ensuring that the input stage is biased at the highest current level only at the high end of the gain range, where the lowest input noise is required, in line with the noise requirement discussed in Section III-D. For lower gain levels, at which a higher input noise is acceptable, the bias currents are reduced.

At the chosen bias point, the input transistors suffer from relatively low output impedance and large gate–drain capacitance, which degrades the gain and increases the input-referred noise. To mitigate these effects, cascade transistors are employed.

A similar second stage provides additional gain  $g_{m2}/g_{m2L}$ . In this case, the input is a current-reuse stage without cascoding for simplicity. Again, a tail current dependent on  $V_{\text{TGC}}$  is used to obtain the overall desired variable gain. Each stage has its own common-mode feedback circuit (CMFB) to maintain a proper dc biasing point.

#### C. Transconductance-Control Circuit

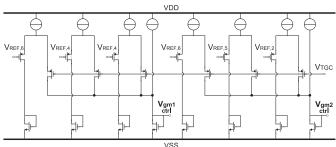

The circuit that generates the bias currents for the loop amplifier as a function of  $V_{\text{TGC}}$  is shown in Fig. 12. A current steering mechanism similar to that used in the gain-control circuit (Fig. 9) is employed, in which  $V_{\text{TGC}}$  is compared to

Fig. 12. Circuit diagram of the transconductance-control circuit.

Fig. 13. Chip micrograph of the 64-channel transceiver ASIC, with inset showing the element-level TIA.

reference voltages by means of differential pairs. For each stage of the loop amplifier, three PMOS differential pairs are used of which the tail currents add to the bias current when  $V_{\text{TGC}}$  drops below the respective reference voltage. The tail current levels and reference voltage levels (derived from the resistive divider shown in Fig. 9) have been chosen based on the simulation to obtain a near-constant closed-loop bandwidth and sufficient phase margin.

#### V. EXPERIMENTAL RESULTS

### A. Experimental Prototype

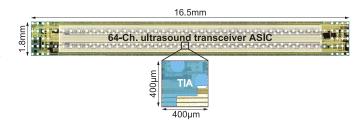

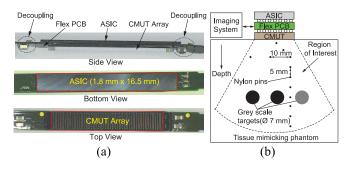

The ASIC has been fabricated in 0.18- $\mu$ m HV BCDMOS process. The ASIC consists of 64 RX and TX channels, each of which interfaces with one element of a 64-element CMUT transducer array. Each RX channel consists of the proposed TIA and a cable driver [41] and is powered by a  $\pm 0.9$  V analog supply and a 1.8 V logic supply. Each TX channel has a programmable HV pulser to generate pulses with a maximum amplitude of  $\pm 30$  V and an HV transmit/receive (T/R) switch to protect the low-voltage RX circuits during pulse transmission. Details of the TX-channel circuitry have been reported in [42]. The channels are arranged in two rows with 32 blocks in each row. This arrangement enables direct pitch-matched connection to the 64-element CMUT transducer array. Fig. 13 shows a photograph of the chip. The proposed TIA occupies an area of 0.12 mm<sup>2</sup>.

#### **B.** Electrical Characterization Results

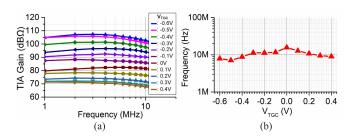

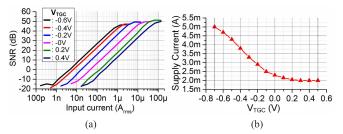

To measure the TIA's transfer function, an input current was generated by applying a voltage signal to a 15-pF off-chip capacitor, which mimics the CMUT capacitance, connected to the TIA's input. Fig. 14(a) shows the measured transfer 8

Fig. 14. (a) Measured transfer function and (b) corresponding -3-dB bandwidth as a function of  $V_{\text{TGC}}$ .

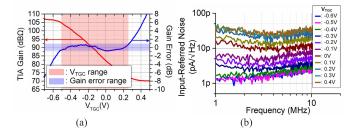

Fig. 15. (a) Measured gain at 5 MHz as a function of  $V_{\text{TGC}}$ , with the associated error compared to a linear-in-dB curve. (b) Input-referred noise spectrum.

function over the whole gain range. As shown in Fig. 14(b), the -3-dB bandwidth varies between 7.1 and 15.7 MHz across the gain range. Compared to the gain variation of almost 40 dB, the bandwidth is kept relatively constant, in good agreement with the designed adaptive gain operation of the loop amplifier.

Fig. 15(a) shows the TIA gain at 5 MHz as a function of the TGC control voltage ( $V_{TGC}$ ). Note that, as expected, the gain decreases with increasing values of  $V_{TGC}$ , which in combination with a  $V_{TGC}$  that decreases with time leads to the desired gain that increases with time. The TIA gain can be varied continuously across a 37 dB range. The corresponding gain error with respect to an ideal linear-in-dB curve is less than  $\pm 1$  dB across the middle 33 dB of the gain range.

The input-referred noise of the TIA was determined by connecting the same off-chip capacitor at the input of the TIA, measuring the output noise, and dividing it by the measured transfer function. The resulting input-referred noise spectra for different values of  $V_{TGC}$  are shown in Fig. 15(b). The noise floor is 1.7 pA/ $\sqrt{Hz}$  at 5 MHz at the highest gain, which is comparable to the CMUT noise floor. The measured spectra also demonstrate that the noise floor increases for lower TIA gains, as expected due to the adaptive biasing of the loop amplifier. At the lowest gain, the noise floor is about 30 pA/ $\sqrt{Hz}$  at 5 MHz. This increase of about 25 dB is less than the expected increase in the signal level of about 40 dB. Therefore, the SNR is not degraded by this gain-dependent noise floor.

This is confirmed by the DR measurement shown in Fig. 16(a), which shows the measured output SNR as a function of the input signal current for different values of  $V_{TGC}$ . The overall input DR, defined as the ratio between the input level at which 1-dB compression occurs at the lowest

Fig. 16. (a) Measured SNR as a function of the signal amplitude for different values of  $V_{\text{TGC}}$ . (b) Measured supply current as a function of  $V_{\text{TGC}}$ .

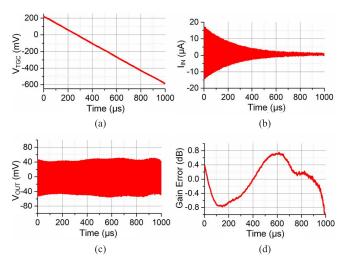

Fig. 17. Measured transient TGC operation. (a) Applied TGC control voltage.(b) Applied exponentially decreasing input signal. (c) Measured output signal.(d) Corresponding error with respect to a linear-in-dB gain curve.

Fig. 18. (a) Implemented prototype. (b) Overview of the measurement setup used for acoustic characterization.

gain and the input level at which the SNR reaches zero at the highest gain, amounts to 82 dB. The variable gain reduces this to 46 dB at the output.

As expected due to the adaptive biasing, the TIA supply current also changes in a gain-dependent manner, as shown in Fig. 16(b). Assuming a linear variation of  $V_{TGC}$  as a function of time to cover the gain range, the variable supply current leads to an average power consumption of 5.2 mW.

Fig. 17 shows the measured transient behavior of the continuous TGC operation. A continuous sinusoidal input current with a frequency of 7 MHz and an exponentially decreasing amplitude, and a corresponding ramp signal are applied to

KANG et al.: VARIABLE-GAIN LOW-NOISE TIA FOR MINIATURE ULTRASOUND PROBES

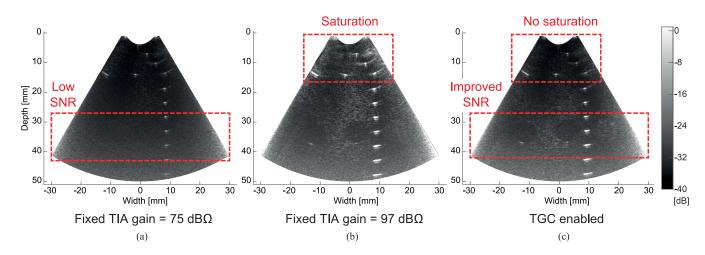

Fig. 19. Phased-array B-mode images with a  $\pm 45^{\circ}$  opening angle, obtained with (a) fixed low gain, (b) fixed high gain, and (c) proposed continuous TGC operation.

|                                           | This work            | [42]                           | [44]                           | [45]                   | [46]                | AD8332 [47]          | VCA2617 [48]       |

|-------------------------------------------|----------------------|--------------------------------|--------------------------------|------------------------|---------------------|----------------------|--------------------|

| Process                                   | 0.18 μm HV<br>BCDMOS | 0.18 µm HV<br>BCDMOS           | 0.18 µm HV<br>CMOS             | 0.35 um<br>CMOS        | BCD-SOI             | -                    | -                  |

| BW                                        | 7MHz                 | 16MHz                          | 10MHz                          | 40MHz                  | 11MHz               | 100MHz               | 50MHz              |

| LNA type                                  | TIA                  | TIA                            | TIA                            | TIA                    | TIA                 | Voltage amp          | Voltage amp        |

| Max gain                                  | 107dBΩ               | 119dBΩ                         | 116dBΩ                         | 106dBΩ                 | 78.4dBΩ             | 68.5dB               | 38dB               |

| Full gain range                           | 37dB                 | 12dB                           | 12dB                           | 0dB                    | 0dB                 | 48dB                 | 48dB               |

| Gain error <sup>(1)</sup><br>(gain range) | ± 1dB<br>(33dB)      | ± 3dB <sup>(2)</sup><br>(12dB) | ± 3dB <sup>(2)</sup><br>(12dB) | -                      | -                   | ± 0.3dB<br>(42dB)    | ± 0.9dB<br>(37dB)  |

| Gain control                              | Continuous           | Discrete                       | Discrete                       | Fixed gain             | Fixed gain          | Continuous           | Continuous         |

| Transducer capacitance                    | 15pF                 | 0.7pF                          | 2 pF                           | 0.09pF                 | 9.2pF               | -                    | -                  |

| Input referred noise                      | 1.7pA/√Hz<br>@5MHz   | 2.0pA/√Hz<br>@13MHz            | 0.41pA/√Hz<br>@ 5MHz           | 0.31 pA/√Hz<br>@ 20MHz | 5.1pA/√Hz<br>@10MHz | 0.74 nV/√Hz<br>@5MHz | 4.1nV/√Hz<br>@5MHz |

| Power consumption                         | 5.2mW                | 0.42mW                         | 1.4mW                          | 0.8mW                  | 1mW                 | 138mW                | 52mW               |

| NEF' <sup>(3)</sup> [mP·√(mW/Hz)]         | 0.78(4)              | 1.23(4)                        | 2.7                            | -                      | 0.55                | -                    | -                  |

TABLE I Performance Summary and Comparison

(1) Maximum deviation from the ideal linear-in-dB curve across the mentioned gain range

(2) Estimated from the discrete gain step

(3) NEF' =  $p_{n,in} \sqrt{Power_{tot}}$  [44] where  $p_{n,in}$  is the input-referred acoustic pressure noise spectral density averaged inside the passband

(4) Calculated by referring the measured noise to an equivalent pressure noise using the estimated transducer sensitivity

the TIA's input and the gain-control port, respectively. The measured output has an approximately constant and smoothly compensated output swing. The gain error extracted from the output amplitude variation is less than  $\pm 1$  dB, demonstrating the intended continuous linear-in-dB TGC operation.

#### C. Acoustical Experiments

Fig. 18(a) shows a fabricated prototype in which the ASIC and CMUT have been flip-chip bonded on a flexible printed circuit board (flex PBC). Each TX/RX channel on the ASIC directly interfaces with a CMUT element. The TIA outputs, buffered by the cable drivers, go to a Verasonics imaging system (Verasonics Inc., Redmond, WA, USA) [43] to record the received echo signals. The flex PBC also connects the power supplies, with local decoupling capacitors, to the ASIC, as well as digital control signals, which are provided by a field-programmable gate array (FPGA).

The test bench for imaging experiments is shown in Fig. 18(b). The implemented prototype is placed at the surface of a tissue-mimicking phantom (GAMMEX SONO404) with an attenuation coefficient of 0.5 dB/cm/MHz. The phantom contains nylon wires acting as point reflectors and gray-scale targets to evaluate the SNR in the image.

Fig. 19 shows  $\pm 45^{\circ}$  phased-array B-mode images of the phantom with 64-channel TX and RX operation. Fig. 19(a) is obtained using a fixed TIA gain of 75 dB· $\Omega$ . As this gain is optimized for the near field, the circular gray-scale targets at larger depth are hardly distinguishable. When the gain is fixed at a higher value of 97 dB· $\Omega$  to improve the SNR at larger depth [Fig. 19(b)], the RX signal at the shallow depths suffers from saturation, leading to a too bright image. With continuous TGC, these issues are mitigated, leading to a higher quality image in which no saturation occurs and the gray-scale targets can be clearly distinguished from the surrounding speckle pattern [Fig. 19(c)]. This imaging experiment successfully

demonstrates the continuous TGC capability of the prototype.

Table I compares the proposed TIA with the prior art. Compared to commercial LNAs with continuous TGC function [46], [47],  $>10 \times$  lower power consumption is achieved. While some of this difference may be attributed to the proposed circuit architecture, it should be noted that these parts have quite different noise and bandwidth specifications and are not intended for in-probe integration. Compared to prior in-probe TIAs, which employ discrete steps or fixed gain [42]–[45], comparable performance is obtained, but with much wider gain range and without the imaging artifacts associated with gain switching.

#### VI. CONCLUSION

This article has presented a low-noise TIA with continuous TGC for ultrasound imaging applications. The TIA employs a capacitive ladder feedback network and interpolation by means of current steering to provide linear-in-dB gain control. The proposed architecture combines LNA and TGC functionality in a single feedback loop, leading to better power efficiency than solutions that employ a fixed-gain LNA followed by a TGC stage, in which the LNA needs to be able to handle the full input DR at its output. In order to accommodate the large variation in the feedback factor, a current-reuse loop amplifier with adaptive biasing has been introduced, which provides approximately constant closed-loop bandwidth and saves power by allowing higher input noise at the lower part of the gain range.

Compared to prior in-probe TIAs, which employ discrete steps or fixed gain, competitive noise efficiency and a wider gain range are obtained without gain-switching transients. The presented electrical measurements demonstrate continuous gain control that is linear-in-dB to within  $\pm 1$  dB. The imaging results obtained in combination with a 64-element CMUT transducer show reduced imaging artifacts and highlight that the presented topology is a promising solution for future in-probe ultrasound ASICs.

#### REFERENCES

- D. N. Stephens *et al.*, "Clinical application and technical challenges for intracardiac ultrasound imaging," in *Proc. IEEE Ultrason. Symp.*, vol. 1, Dec. 2004, pp. 772–777.

- [2] A. Enriquez et al., "Use of intracardiac echocardiography in interventional cardiology," Circulation, vol. 137, no. 21, pp. 2278–2294, 1997.

- [3] W. Saliba *et al.*, "Intracardiac echocardiography during catheter ablation of atrial fibrillation," *Europace*, vol. 10, no. 3, pp. 42–47, 2008.

- [4] S. S. Kim, Z. M. Hijazi, R. M. Lang, and B. P. Knight, "The use of intracardiac echocardiography and other intracardiac imaging tools to guide noncoronary cardiac interventions," *J. Amer. College Cardiol.*, vol. 53, no. 23, pp. 2117–2128, Jun. 2009.

- [5] T. L. Proulx, D. Tasker, and J. Bartlett-Roberto, "Advances in catheterbased ultrasound imaging - Intracardiac echocardiography and the ACU-SON AcuNav (TM) ultrasound catheter," in *Proc. IEEE Ultrason. Symp.*, vol. 1, Oct. 2005, pp. 669–678.

- [6] W. Lee, S. F. Idriss, P. D. Wolf, and S. W. Smith, "A miniaturized catheter 2-D array for real-time, 3-D intracardiac echocardiography," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 51, no. 10, pp. 1334–1346, Oct. 2004.

- [7] W. Lee et al., "A 10-Fr ultrasound catheter with integrated micromotor for 4-D intracardiac echocardiography," in *IEEE Trans. Ultrason.*, *Ferroelectr., Freq. Control*, vol. 58, no. 7, pp. 1478–1491, Jul. 2011.

- [8] D. Wildes et al., "4-D ICE: A 2-D array transducer with integrated ASIC in a 10-fr catheter for real-time 3-D intracardiac echocardiography," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 63, no. 12, pp. 2159–2173, Dec. 2016.

- [9] G. Jung et al., "A reduced-wire ICE catheter ASIC with Tx beamforming and Rx time-division multiplexing," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 6, pp. 1246–1255, Dec. 2018.

- [10] J. Lee et al., "11.1 a 5.37 mW/Channel pitch-matched ultrasound ASIC with Dynamic-Bit-Shared SAR ADC and 13.2 V charge-recycling TX in standard CMOS for intracardiac echocardiography," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 190–192.

- [11] Y. Igarashi *et al.*, "Single-chip 3072-Element-Channel Transceiver/128-Subarray-Channel 2-D array IC with analog RX and all-digital TX beamformer for echocardiography," *IEEE J. Solid-State Circuits*, vol. 54, no. 9, pp. 2555–2567, Sep. 2019.

- [12] C. Chen *et al.*, "A pitch-matched front-end ASIC with integrated subarray beamforming ADC for miniature 3-D ultrasound probes," *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3050–3064, Nov. 2018.

- [13] M. C. Chen *et al.*, "A Pixel-Pitch-Matched Ultrasound Receiver for 3D Photoacoustic Imaging with Integrated Delta-Sigma Beamformer in 28nm UTBB FDSOI," in *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2843–2856, Nov. 2017.

- [14] T. L. Szabo, *Diagnostic Ultrasound Imaging: Inside Out*, 2nd ed. Boston, MA, USA: Academic, 2014.

- [15] R. Wodnicki *et al.*, "Electronics for diagnostic ultrasound," in *Medical Imaging, Principles, Detectors, and Electronics*, K. Iniewski, Ed. New York, NY, USA, Wiley, 2009, pp. 165–220.

- [16] E. Kang et al., "23.6 a 2pA/–Hz transimpedance amplifier for miniature ultrasound probes with 36dB continuous-time gain compensation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 354–356.

- [17] Z. Yu et al., "Front-end receiver electronics for a matrix transducer for 3-D transesophageal echocardiography," *IEEE Trans. Ultrason.*, *Ferroelectr., Freq. Control*, vol. 59, no. 7, pp. 1500–1512, Jul. 2012.

- [18] C. Chen *et al.*, "A prototype PZT matrix transducer with low-power integrated receive ASIC for 3-D transesophageal echocardiography," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 63, no. 1, pp. 47–59, Jan. 2016.

- [19] C. Chen *et al.*, "A front-end ASIC with receive sub-array beamforming integrated with a 32×32 PZT matrix transducer for 3-D transesophageal echocardiography," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 994–1006, Apr. 2017.

- [20] S. Oswal *et al.*, "Time dependant gain control for an amplifier used in receiving echoes," U.S. Patent 7885144 B2, Feb. 8, 2011.

- [21] Y. Wang, M. Koen, and D. Ma, "Low-noise CMOS TGC amplifier with adaptive gain control for ultrasound imaging receivers," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 58, no. 1, pp. 26–30, Jan. 2011.

- [22] M. Tan *et al.*, "A front-end ASIC with high-voltage transmit switching and receive digitization for 3-D forward-looking intravascular ultrasound imaging," *IEEE J. Solid-State Circuits*, vol. 53, no. 8, pp. 2284–2297, Aug. 2018.

- [23] H. Elwan, A. Tekin, and K. Pedrotti, "A differential-ramp based 65 dBlinear VGA technique in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 9, pp. 2503–2514, Sep. 2009.

- [24] Q. H. Duong et al., "A 95 dB linear low power variable gain amplifier," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 53, no. 8, pp. 1648–1657, Aug. 2006.

- [25] H.-H. Nguyen, H.-N. Nguyen, J.-S. Lee, and S.-G. Lee, "A binaryweighted switching and reconfiguration-based programmable gain amplifier," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 9, pp. 699–703, Sep. 2009.

- [26] I. Choi, H. Seo, and B. Kim, "Accurate dB-linear variable gain amplifier with gain error compensation," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 456–464, Feb. 2013.

- [27] H. Liu, X. Zhu, C. C. Boon, and X. He, "Cell-based variable-gain amplifiers with accurate dB-linear characteristic in 0.18 μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 586–596, Feb. 2015.

- [28] M. Sautto, F. Quaglia, G. Ricotti, and A. Mazzanti, "5.6 a 420 μm 100GHz-GBW CMOS programmable-gain amplifier leveraging the cross-coupled pair regeneration," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Jan. 2016, pp. 98–99.

- [29] B. Gilbert, "A low-noise wideband variable-gain amplifier using an interpolated ladder attenuator," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, 1998, pp. 280–281.

- [30] E. Brunner, "An ultra-low noise linear-in-dB variable gain amplifier for medical ultrasound applications," in *Proc. WESCON*, 1995, pp. 650–655.

- [31] B. Gilbert, "Low noise amplifier having sequentially interpolated gain stages," U.S. Patent 6445248 B1, Sep. 3, 2002.

- [32] M. J. Koen, "Process and temperature-independent voltage controlled attenuator and method," U.S. Patent 7 521 980, Apr. 21, 2009.

- [33] B. R. Veillette, "Variable gain current amplifier with a feedback loop including a differential pair," U.S. Patent 6798291, Sep. 28, 2004.

- [34] R. Onet, M. Neag, I. Kovacs, M. D. Topa, S. Rodriguez, and A. Rusu, "Compact variable gain amplifier for a multistandard WLAN/WiMAX/LTE receiver," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 1, pp. 247–257, Jan. 2014.

- [35] B. Gilbert, "Variable-gain amplifier controlled by an analog signal and having a large dynamic range," European Patent 0543927 B1, Aug. 31, 1991.

- [36] O. Oralkan et al., "Capacitive micromachined ultrasonic transducers: Next-generation arrays for acoustic imaging?" *IEEE Trans. Ultrason.*, *Ferroelectr., Freq. Control*, vol. 49, no. 11, pp. 1596–1610, Nov. 2002.

- [37] G. Gurun, P. Hasler, and F. L. Degertekin, "Front-end receiver electronics for high-frequency monolithic CMUT-on-CMOS imaging arrays," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 58, no. 8, pp. 1658–1668, Aug. 2011.

- [38] K. Chen, H.-S. Lee, A. P. Chandrakasan, and C. G. Sodini, "Ultrasonic imaging transceiver design for CMUT: A three-level 30-vpp pulseshaping pulser with improved efficiency and a noise-optimized receiver," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2734–2745, Nov. 2013.

- [39] B. Razavi, "A 622 Mb/s 4.5 pA/ Hz CMOS transimpedance amplifier," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2000, pp. 162–163.

- [40] M. Bazes, "Two novel fully complementary self-biased CMOS differential amplifiers," *IEEE J. Solid-State Circuits*, vol. 26, no. 2, pp. 165–168, Feb. 1991.

- [41] E. Kang *et al.*, "A reconfigurable ultrasound transceiver ASIC with 24 × 40 elements for 3-D carotid artery imaging," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 2065–2075, Jul. 2018.

- [42] M. Tan *et al.*, "A 64-channel transmit beamformer with ±30-V bipolar high-voltage pulsers for catheter-based ultrasound probes," *IEEE J. Solid-State Circuits*, vol. 55, no. 7, pp. 1796–1806, Jul. 2020.

- [43] Vantage Systems. Accessed: Sep. 15, 2020. [Online]. Available: https://verasonics.com/vantage-systems/

- [44] K. Chen, H.-S. Lee, and C. G. Sodini, "A column-row-parallel ASIC architecture for 3-D portable medical ultrasonic imaging," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 738–751, Mar. 2016.

- [45] G. Gurun *et al.*, "Single-chip CMUT-on-CMOS front-end system for real-time, volumetric IVUS and ICE imaging," *IEEE Transactions on Ultrason., Ferroelectr., Frequency Control*, vol. 61, no. 2, pp. 239–250, Oct. 2014.

- [46] M. Sautto, A. S. Savoia, F. Quaglia, G. Caliano, and A. Mazzanti, "A comparative analysis of CMUT receiving architectures for the design optimization of integrated transceiver front ends," *IEEE Trans. Ultrason.*, *Ferroelectr., Freq. Control*, vol. 64, no. 5, pp. 826–838, May 2017.

- [47] Ultralow Noise VGAs with Preamplifier and Programmable RIN Analog Devices, document AD8332, 2016.

- [48] Dual, Variable Gain Amplifier, Texas Instruments, Dallas TX, USA, 2005.

Mingliang Tan (Student Member, IEEE) received the B.S. degree in electronic science and technology from Northeastern University, Shenyang, China, in 2014 and the M.S. degree in microelectronics from the Delft University of Technology, Delft, The Netherlands, in 2016. He is currently pursuing the Ph.D. degree in electrical engineering with the Electronic Instrumentation Laboratory, Delft University of Technology, with a focus on application-specific integrated circuit (ASIC) design for medical ultrasound imaging.

His research interests include analog and mixed-signal electronics, especially for biomedical applications.

**Jae-Sung An** (Member, IEEE) received the B.S. degree in media communications engineering from Hanyang University, Seoul, South Korea, in 2010 and the Ph.D. degree from the Integrated Electronics Laboratory, Hanyang University, in 2018.

In 2018, he was with Leading UI Company, Ltd., Anyang, South Korea, where he developed the analog front-end integrated circuits (ICs) for the capacitive touch system and fingerprint sensing system. Since he joined the Electronic Instrumentation Labo-

ratory, Delft University of Technology, Delft, The Netherlands, in 2018, he has been investigating the ultrasound imaging system. His work has focused on the high-precision analog integrated circuit design, driving and sensing schemes for capacitive touch systems with passive and active styli, fingerprint sensing systems, and ultrasound imaging systems. He has authored or coauthored three patents and over 17 technical papers, including the four International Solid-State Circuits Conference (ISSCC) papers with demonstrations.

Dr. An was on the Korea Evaluation Institute of Industrial Technology (KEIT) Working Group for automotive SoC and biomedical/biohealth electronics.

**Zu-Yao Chang** received the M.Sc. degree in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 2003.

Since 2003, he has been a Staff Member with Electronic Instrumentation Laboratory, Delft University of Technology, working on impedance measurement systems and smart sensor systems.

**Eunchul Kang** (Member, IEEE) received the B.S. and M.S. degrees in electronic engineering from Sogang University, Seoul, South Korea, in 2005 and 2007, respectively. He is currently pursuing the Ph.D. degree with the Electronic Instrumentation Laboratory, Delft University of Technology, Delft, The Netherlands.

From 2007 to 2010, he was with Fairchild Semiconductor, Bucheon, South Korea, as an Analog Design Engineer. From 2010 to 2011, he was a Research Assistant with Inter-University Semicon-

ductor Research Center, Seoul. From 2011 to 2015, he was a Design Engineer with Silicon Mitus, Seongnam, South Korea, on the design of power management integrated circuits (ICs). Since 2020, he has been with Sony Semiconductor Solutions, Oslo, Norway, as a Senior Analog Design Engineer.

**Philippe Vince** received the M.Sc. degree in electronic engineering from ENSEIRB, Bordeaux, France, in 1990 and the Ph.D. degree in life sciences applied in medical imaging from the Université François Rabelais, Tours, France, in 1995.

He worked as an RF IC Designer with Philips Semiconductors, Caen, France, from 1995 to 1998. From 1998 to 2005, he was with Ultrasons Technologies, Tours, as a Research and Development Engineer, where he developed ultrasound scanner prototypes dedicated for research activities. From

2006 to 2016, he continued the same activities for Althaïs Technologies, an engineering department from the Université François Rabelais. In 2016, he joined Vermon S.A., Tours, as a Research and Development Engineer. His research interests relate to electronic integration in ultrasound probes for medical imaging.

Nicolas Sénégond received the Engineering degree in instrumentation and sensors from EIVL, Blois, France, in 2005, the master's degree in biomedical engineering from the University of Tours, Tours, France, in 2006, and the Ph.D. degree from the Imaging and Brain Inserm unit (U930), Tours, in 2010, with a focus on the development and the modeling of CMUT technology.

Since 2012, he has been with Vermon S.A., Tours, as the Project Manager, where he mainly works on the design, characterization, and integration of

micro-machined ultrasound transducer (MUT) probes dedicated for therapy and imaging application. He currently leads the team dedicated on MUT technologies development at Vermon.

**Cyril Meynier** (Member, IEEE) was born in Roubaix, France, in 1982. He received the Ph.D. degree with a specialty in microsystems work from the Imaging and Brain Inserm unit (U930), Université François Rabelais, Tours, France, in 2009, with a focus on capacitive micromachined ultrasonic transducers. He studied at the Insistut supérieur d'électronique du Nord (ISEN), Lille, France, from 2000 to 2005.

He is currently a Research and Development Researcher with Vermon S.A., Tours, working on

both capacitive micro-machined ultrasound transducers (CMUTs) and piezo-electric transducers.

Michiel A. P. Pertijs (Senior Member, IEEE) received the M.Sc. and Ph.D. degrees (*cum laude*) in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 2000 and 2005, respectively.

From 2005 to 2008, he was with National Semiconductor, Delft, where he designed precision operational amplifiers and instrumentation amplifiers. From 2008 to 2009, he was a Senior Researcher with imec/Holst Centre, Eindhoven, The Netherlands. In 2009, he joined the Electronic Instrumentation

Laboratory, Delft University of Technology, where he is currently an Associate Professor. He heads a research group focusing on integrated circuits for medical ultrasound and energy-efficient smart sensors. He has authored or coauthored two books, four book chapters, 15 patents, and over 120 technical articles.

Dr. Pertijs is a member of the Technical Program Committee of the European Solid-State Circuits Conference (ESSCIRC). He served on the Program Committee of the International Solid-State Circuits Conference (ISSCC) and the IEEE Sensors Conference. He received the ISSCC 2005 Jack Kilby Award for Outstanding Student Paper and the JSSC 2005 Best Paper Award. For his Ph.D. research on high-accuracy CMOS smart temperature sensors, he received the 2006 Simon Stevin Gezel Award from the Dutch Technology Foundation STW. In 2014, he was elected as the Best Teacher of the EE program at the Delft University of Technology. He serves as an Associate Editor (AE) for the IEEE OPEN JOURNAL OF SOLID-STATE CIRCUITS (O-JSSC) and IEEE's open-access version of the Journal of Solid-State Circuits (JSSC), for which he previously served as an Associate Editor.

**Tony Mateo** received the M.Sc. degree in biomedical engineering from the University of Technology of Compiègne, Compiègne, France, in 2009 and the Ph.D. degree in life and health sciences applied in ultrasound imaging from the Imaging and Brain Inserm unit (U930), Université François Rabelais, Tours, France, in 2014, with a focus on ultrasound imaging solutions for ocular ultrasonography, within, Tours, France.

Since 2016, he has been with Vermon S.A., Tours, as a Research and Development Engineer, where he

is mainly involved in ultrasound probe implementation on research systems for various kinds of characterizations and evaluations on many transducer design and technologies.