# A Survey of Test and Reliability Solutions for Magnetic Random Access Memories

Girard, Patrick; Cheng, Yuanging; Virazel, Arnaud; Zhao, Weisheng; Bishnoi, Rajendra; Tahoori, Mehdi B.

10.1109/JPROC.2020.3029600

**Publication date** 2020

**Document Version** Accepted author manuscript Published in Proceedings of the IEEE

Citation (APA)

Girard, P., Cheng, Y., Virazel, A., Zhao, W., Bishnoi, R., & Tahoori, M. B. (2020). A Survey of Test and Reliability Solutions for Magnetic Random Access Memories. Proceedings of the IEEE, 109 (2021)(2), 149-169. Article 9240959. https://doi.org/10.1109/JPROC.2020.3029600

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A Survey of Test and **Reliability Solutions for Magnetic Random Access Memories**

By PATRICK GIRARD<sup>®</sup>, Fellow IEEE, YUANQING CHENG<sup>®</sup>, Senior Member IEEE, ARNAUD VIRAZEL<sup>®</sup>, Member IEEE, WEISHENG ZHAO<sup>®</sup>, Fellow IEEE, RAJENDRA BISHNOI, AND MEHDI B. TAHOORI, Senior Member IEEE

ABSTRACT | Memories occupy most of the silicon area in nowadays' system-on-chips and contribute to a significant part of system power consumption. Though widely used, nonvolatile Flash memories still suffer from several drawbacks. Magnetic random access memories (MRAMs) have the potential to mitigate most of the Flash shortcomings. Moreover, it is predicted that they could be used for DRAM and SRAM replacement. However, they are prone to manufacturing defects and runtime failures as any other type of memory. This article provides an up-to-date and practical coverage of MRAM test and reliability solutions existing in the literature. After some background on existing MRAM technologies, defectiveness and reliability issues are discussed, as well as functional fault models used for MRAM. This article is dedicated to a summarized description of existing test and reliability improvement methods developed

I. INTRODUCTION

Spin electronics (Spintronics) is one of the most interesting and challenging topics in today's nanotechnology. It has pushed scientific research and microelectronic industry to build innovative electronic devices that rely on magnetic properties. Similar to other emerging resistive memory technologies, such as resistive random access memory (RRAM) [1] and phase-change memory (PCM) [2], magnetic or magneto-RRAM (MRAM) is a form of resistive memory technology where data are stored in terms of resistive states. Moreover, MRAM uses the spin of electrons for storage instead of their charge. Comparisons of different kinds of memory technologies are shown in Table 1. As illustrated in this table, MRAM technology has demonstrated the promise of universal memory. MRAM has several characteristics that make it is useful for many applications. Nonvolatility (ability to maintain memory contents without requiring power), performance (SRAM and DRAM-like speed with low latency), endurance (durability to support memory workloads without complex management), and reliability (robustness designed for extreme conditions) are these main characteristics. Moreover, an important feature of MRAM technology is that its fabrication process is CMOS-compatible [3].

so far for various MRAM technologies. The last part of this

**KEYWORDS** | Magnetic random access memory (MRAM);

article gives some perspectives on this hot topic.

nonvolatile memories; reliability; spintronics; test.

Manuscript received January 21, 2020; revised July 9, 2020 and September 24, 2020; accepted October 1, 2020. The work of Yuanqing Cheng was supported in part by Science, Technology and Innovation Commission of Shenzhen Municipality under Grant JCYJ20180307123657364. (Corresponding author: Patrick Girard.)

Patrick Girard and Arnaud Virazel are with the Laboratory of Computer Science, Robotics and Microelectronics of Montpellier (LIRMM), University of Montpellier/CNRS, 34095 Montpellier, France (e-mail: girard@lirmm.fr;

Yuanqing Cheng is with the School of Microelectronics, Beihang University, Beijing 100191, China (e-mail: yuanging@ieee.org).

Weisheng Zhao is with the Fert Beijing Institute, Beihang University, Beijing 100191, China, and also with the School of Microelectronics, Beihang University, Beijing 100191, China (e-mail: weisheng.zhao@buaa.edu.cn).

Rajendra Bishnoi is with the Computer Engineering Lab, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: r.k.bishnoi@tudelft.nl). Mehdi B. Tahoori is with the Department of Computer Science, Karlsruhe Institute of Technology, 76131 Karlsruhe, Germany (e-mail: mehdi.tahoori@kit.edu).

Digital Object Identifier 10.1109/JPROC.2020.3029600

0018-9219 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Table 1 Comparisons of Different Memory Technologies [5]-[7]

|                   | SRAM        | DRAM         | NAND            | PCRAM         | RRAM                | STT-MRAM      |  |

|-------------------|-------------|--------------|-----------------|---------------|---------------------|---------------|--|

| Cell size $(F^2)$ | $\sim 150$  | ~ 8          | $\leq 1$        | $\sim 5$      | $\sim 4$            | $6 \sim 8$    |  |

| Non-Volatility    | No          | No           | Yes             | Yes           | Yes                 | Yes           |  |

| Read Time         | $\sim ns$   | $\sim 30 ns$ | $\sim 50 \mu s$ | $\sim 30 ns$  | 20ns                | $10\sim 20ns$ |  |

| Write Time        | $\sim ns$   | $\sim 30 ns$ | $\sim ms$       | $\sim 500 ns$ | $0.3 \sim 30 ns$    | $10\sim 20ns$ |  |

| Endurance         | $> 10^{15}$ | $> 10^{15}$  | $10^{5}$        | $\sim 10^7$   | $10^6 \sim 10^{12}$ | $> 10^{15}$   |  |

| Byte Operation    | Yes         | Yes          | No              | Yes           | Yes                 | Yes           |  |

High-density MRAM can be seen as a replacement for SRAM applications, such as cache memories. In addition to providing fast (low latency) caches, MRAM is nonvolatile and, thus, allows instant power on as it does not require capacitances to save data when power is removed. Because it can reduce latency for various devices, MRAM can help in data centers, at the edge of networks and network endpoints. This is especially important as high-speed wireless networks (e.g., 5G) become more common. The vast majority of these applications use limited energy sources (e.g., batteries), and hence, MRAM nonvolatility can be helpful [4]. MRAM can also be used as embedded memory, where macros are embedded or integrated with microcontroller units (MCUs). Finally, MRAM can be used for DRAM replacement in mission-critical enterprise applications, where power loss and lost memory can severely impact a client.

Automotive, the Internet of Things (IoT), and many other applications drive the market growth for MRAM. The global MRAM market is expected to reach \$4.8 billion by 2025 [8]. This growth is primarily attributed to the rising demand for power-efficient, cost-effective, and nonvolatile memory in many end-user industries, surging demand for flexible and wearable electronics, and increasing research and development activities. In addition, advancement in technology is further projected to augment market growth during the forecast period, as well as the huge demand for embedded applications.

MRAM performance, low power, and persistence are the major reasons for its use for many applications. For example, MRAM can be used in extreme-low-power designs, such as wearables, RFID-based applications, such as trackers, and performance-constrained domains, such as cloud applications. As mentioned earlier, an example is data centers, where power is the highest part of their operational costs.

Due to its nonvolatility, MRAM technology is also definitively recognized as the best alternative to the Flash memory technology that reaches its limits due to intrinsic variability issues or challenging cointegration with the CMOS process. It offers a number of advantages compared with the Flash technology, such as higher read/write speed, lower power consumption, longer endurance, better reliability (mainly due to its immunity to radiations), higher integration density and scalability, and new functionalities, such as computing-in-memory [9]–[11], neuromorphic

computing [12]–[14], true random number generation (TRNG), and physically unclonable function (PUF) for security [15], [16]. Magnetic devices can be used not only for standalone or embedded memories but also in the logic itself (e.g., nonvolatile decoders) [8].

Though MRAMs have the potential to mitigate almost all shortcomings of Flash and compete with other types of memory technology, however, they are as prone to defectivity and reliability issues as any other kind of memory. For this reason, a number of test and reliability improvement solutions targeting various MRAM technology generations have been developed in the last decade. These solutions were presented very often with interesting case studies and convincing experimental results.

This article surveys the existing MRAM test and reliability improvement solutions published so far. These solutions deal with the development of test algorithms (March-type, retention, thermal stability, and so on) and their implementation [e.g., memory built-in self-test (MBIST)]. Defect analysis and fault modeling are a prerequisite to the development of these solutions and, hence, are discussed in this article. Similarly, reliability concerns have been addressed in the literature through the development of Design-for-Reliability (DfR) solutions that target process variability, endurance degradation, and data disturbance. These solutions are summarized and discussed in this article. Note that some test and reliability solutions may also apply to other resistive emerging memory devices, such as RRAM and PCM. We will discuss the relevance and generalities of these solutions in appropriate places to provide the reader with an overall perspective of test and reliable design for emerging nonvolatile memory technologies.

The rest of this article is organized as follows. Section II presents an overview of the various MRAM technologies existing today. Section III discusses the defectiveness and reliability issues that may occur in MRAMs. Section IV surveys all existing test solutions for this type of memory. Similarly, Section V gives an overview of all existing reliability improvement solutions. Section VI concludes this article.

#### II. MRAM TECHNOLOGIES

The magnetic tunnel junction (MTJ) is the basic block of an MRAM and uses the magnetoresistance property of a material to change the value of its electrical resistance. Based on this principle, several MRAM technologies have

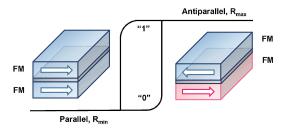

Fig. 1. MTJ in parallel and antiparallel states.

been proposed in the last years. They are presented in the following.

#### A. Magnetic Tunnel Junction

MTJs are spintronic devices that can be used in numerous applications, such as sensors and oscillators, and the basic building block of nonvolatile memories [17]. An MTJ usually consists of two ferromagnetic (FM) layers separated by an ultrathin insulating layer in which electrons can tunnel. One of the FM layers is pinned and acts as a reference layer. The other one is free and can be switched between at least two stable states. Hence, this device presents a magnetoresistive effect, which depends on the relative magnetization state of the FM layers. Fig. 1 shows a basic MTJ device. These states are parallel or antiparallel with respect to the reference layer. MTJ offers maximum resistance to electric current  $(R_{\text{max}})$  when the magnetizations of the FM layers are in an antiparallel configuration. Conversely, this device offers minimum resistance ( $R_{\min}$ ) in a parallel configuration. The tunnel magnetoresistance (TMR), which is the resistive effect that occurs in these magnetic devices, quantifies the difference between  $R_{\min}$ and  $R_{\text{max}}$  and can be defined as follows [18]:

$$TMR = \frac{R_{\text{max}} - R_{\text{min}}}{R_{\text{min}}} \times 100\%. \tag{1}$$

A read operation consists in determining the magnetization state of the MTJ and can be done by voltage or current sensing across the MTJ stack. A CMOS-based sense amplifier is employed to retrieve the stored bit information. High TMR allows simple and stable sense amplifiers, improving the reading accuracy. A write operation is usually performed by using magnetic fields or spin-polarized current depending on the MRAM technology. This is discussed in Section II-B.

#### **B. Existing MRAM Technologies**

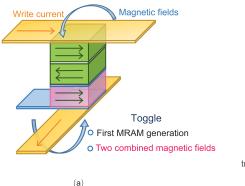

MRAM technologies can be classified by considering the switching method used to write data [19]. The first-generation MRAM refers to methods using magnetic fields to program (write-in) the array. As shown in Fig. 2(a), field-induced magnetic switching (FIMS) and FIMS-Toggle can be written by applying magnetic fields generated by two current lines [20], [21]. The energy required to reverse the magnetization state in these MRAMs is minimized by concurrently applying these two perpendicular magnetic fields. A major advantage of field switching is the unlimited write endurance since reversing the magnetization of the free layer with a magnetic field does not induce any wear-out effects. On the other side, the FIMS drawback is the selectivity issue, which is the ability to write the selected MTJs without disturbing the other MTJs (this is called write margin). Another drawback is the scalability issue, which is mainly due to the magnitude of the required switching currents and the complexity of the memory cell geometry.

Another technology based on the same writing principle is the thermally assisted switching (TAS) MRAM technology [22]. Here, the MTJ is modified by inserting an anti-FM (AFM) layer that pins the storage layer while below its blocking temperature  $T_{\rm B}$ . As shown in Fig. 2(b), when the temperature of the MTJ rises above  $T_{\rm B}$ , the storage layer is freed. Hence, it can be reversed under the application of a small magnetic field provided by a single field line. This field is maintained beyond the heating voltage pulse to ensure the correct pinning of the storage layer. Though it has several advantages compared with Toggle-MRAM, such as reduced selectivity issues and improved integration density due to: 1) thermal stability and 2) the need for only one field line, TAS-MRAM still suffers from structure complexity and area cost issues.

An evolution of the TAS-MTJ is the magnetic logic unit (MLU) MTJ in which the AFM layer is replaced by a nonmagnetic (NM) layer. The formerly fixed reference layer, now called the sense layer, may change its magnetization state by the application of an external magnetic field. The writing process does not change with respect to TAS-MTJ, but the read procedure now relies on a sample and hold approach. The main advantages are an increasing density with less neighboring cell disturbances and an enhanced read margin [23].

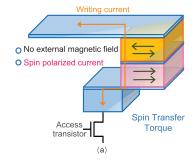

The second-generation MRAM uses a spin-polarized current through the MTJ to write data. Spin transfer torque (STT) switching was the first proposed principle for this type of MRAM. As shown in Fig. 3(a), the magnetic moment in the fixed layer is fixed in one direction, while the direction of the magnetic moment in the free layer can be changed according to the difference and polarity of potential across the MTJ. Indeed, when a potential difference is applied across the MTJ, a spin-polarized current passes through the MTJ and polarizes the current in its preferred direction of the magnetic moment. The angular momentum of the electrons in the free layer creates a torque, which causes a change in the direction of the magnetization inside the free layer. Depending on the magnetization direction in the free layer, the resistance of the MTJ is modified. STT switching can be achieved with acceptable efficiency by using MTJ devices having either planar or perpendicular magnetization. The main advantages of STT-MRAM are fast read/write speed, high density, high

Thermally Assisted

Switching

O Free layer blocked at room temperature

O Heat current + magnetic fields

(b)

Fig. 2. MTJ structures of (a) Toggle-MRAM and (b) TAS-MRAM.

endurance, and high reliability. Especially, the TMR ratio in the common stacks involved with MgO/CoFeB interfaces has recently been demonstrated to be higher than 200% [24], which can reach the technological requirements [25]. Despite several remaining challenges, such as patterning process, read and write error rates, or long-term data retention, STT-MRAM technology is now entering into high-volume mass production serving markets from 2018. A number of IoT products embedded with STT-MRAM have been commercialized to provide long standby duration, such as the smartwatch. However, applications are limited to some niche markets as its lifetime is not yet fully satisfactory [26]. This reliability issue is due to the intrinsic mechanism of STT where the switching current should pass through the tunneling barrier. Many studies are focusing on the circuit- and system-level controls to reduce the number of switching operations for STT-MRAMbased computing systems, but it is difficult to achieve both fast speed and high reliability.

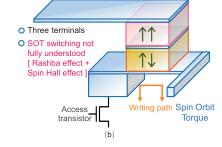

To mitigate some of the remaining issues of STT-MRAM, spin-orbit torque (SOT) MRAM has been proposed. As shown in Fig. 3(b), SOT-MRAM uses a three-terminal MTJ-based concept to isolate read and write paths, significantly improving device endurance and read stability. Unlike STT, magnetization reversal by spin-orbit torque is performed using in-plane currents. Due to the nature

Table 2 Comparisons of Different MRAM Technologies [30], [31]

|               | FIMS      | TAS-MRAM  | STT-MRAM   | SOT-MRAM   |

|---------------|-----------|-----------|------------|------------|

| Read Latency  | 35ns      | ~30ns     | <10ns      | <10ns      |

| Write Latency | 35ns      | ~30ns     | <10ns      | <1ns       |

| Retention     | >10y      | >10y      | >10y       | >10y       |

| Endurance     | $10^{15}$ | $10^{15}$ | $>10^{15}$ | $>10^{15}$ |

| Write Energy  | High      | Medium    | Low        | Low        |

| Density       | Medium    | Medium    | High       | Medium     |

| TMR           | >100%     | >100%     | >100%      | ~90%       |

| Scalability   | Medium    | Medium    | High       | High       |

of the spin torque injection geometry (perpendicular to the easy axis), the incubation time is negligible and allows reliable switching operation in the sub-nanosecond timescale. However, in an MTJ with perpendicular magnetic anisotropy, an external magnetic field is necessary for SOT to realize deterministic switching. Similar to FIMS, this external magnetic field in MRAM will severely limit its scalability and reliability. To solve this problem, several switching solutions were proposed [27]–[29]. Among them, the magnetic switching realized by the interplay of STT and SOT could not only solve the external field problem of SOT but also reduce the amplitude and duration of STT current [27]. Therefore, it can have a longer endurance since the current-induced barrier breakdown is mitigated. The comparison of FIMS, TAS-MRAM, STT-MRAM, and SOT-MRAM is summarized in Table 2.

Fig. 3. MTJ structures of (a) STT-MRAM and (b) SOT-MRAM.

#### 4 PROCEEDINGS OF THE IEEE

The third-generation MRAM refers to the potential use of other physical phenomena, including voltage-controlled magnetic anisotropy (VCMA), voltage-controlled magnetism (VCM), and spin Hall effect (SHE) [32]. The idea behind the use of these phenomena is that switching could be performed with little or no electrical current passing through the MTJ device, hence improving MRAM scaling and performance. However, each physical phenomenon has challenges to overcome for use in practical MRAM circuits [19]. For example, VCMA alone would not lead to deterministic switching between two stable states. Instead, it is more likely to be applied together with another innovation for use in an MRAM array. A better understanding of reliability issues, such as wear-out and parameter drift, is needed for practical VCM devices. Similarly, SHE is not compatible with efficient switching in devices having perpendicular magnetization. In many cases, a threeterminal cell configuration would be needed for these third-generation devices, which is not compatible with high-density memory arrays. However, the possibility of switching with little or no charge current passing through the tunnel barrier is highly motivating due to the further possible use in low-power circuits and high-endurance applications.

Besides these existing MRAM technologies, and in a wider perspective that intends to provide a complete logic/memory family with better energy and delay performances, a new concept has emerged recently. It consists of a scalable, CMOS-compatible, nonvolatile spintronic logic device that operates via spin-orbit transaction combined with magnetoelectric switching. No TMR or STT is used. The proposed magnetoelectric spin-orbit (MESO) logic enables a new paradigm to continue the scaling of logic device performance. More details can be found in [33]. It is important to note that racetrack/skyrmion and multilevel cells are interesting research directions beyond MRAM development. However, these technologies are still under the first step of R&D to demonstrate a working device [34], and there are no racetrack/skyrmion and multilevel devices showing electrical read-out switching without magnetic field up until now [35]. There are no test and reliability methods for the chip level on racetrack/skyrmion and multilevel cells.

### III. DEFECTIVENESS AND RELIABILITY ISSUES OF MRAMS

Defects and failures in MRAM may occur during the manufacturing process or during the lifetime of the memory. In the first case, we refer to defectiveness issues. In the second case, we refer to reliability issues. Note that these reliability issues may be the consequence of wear-out or aging mechanisms or inherent MTJ device parameter instability but can also be provoked by parameter deviations coming from an improper but acceptable manufacturing process and that will evolve over time. All these aspects are discussed in the following. Of course, there are differences in manufacturing steps and processes of different flavors of MRAM, which can lead to unique manufacturing defects and runtime failures for each of these specific technologies. Nevertheless, although most of the defectiveness and reliability issues discussed in this section have been reported in studies dealing with STT-MRAM, they can be considered as general issues that may occur in all types of MRAM, regardless of the specific technology. Besides, some kinds of defects, such as resistive-open and resistive-short, can also be observed in RRAM and PCM due to immature fabrication process or process variations [36].

#### A. Defectiveness Issues

Defectiveness issues of MRAM can be attributed to imperfect manufacturing process during which strong or weak defects may occur or process variability is too severe and drastically impacts device parameters. These issues can be fundamentally different from those observed on other memory technologies since both working principles and development processes for this technology are completely dissimilar. Zhao et al. [37], [38] classified MRAM errors into "hard errors" (similar to strong or weak defects) and "soft errors" (similar to parametric failures).

1) Strong or Weak Defects: These defects are the consequence of issues that occur during the fabrication steps. They can be caused by the deposition of dust particles, voids occurring during the electrode polishing, oxide barrier breakdown, or improper etching followed by sideways material redeposition [39]. These defects can be strong or weak defects depending on their influence on the system. The strong defects prevent the device to operate correctly and lead to permanent failures (hard faults). Examples are open, bridge, or parasitic coupling defects. Weak defects prevent the device to operate correctly depending on the size of the defect and also lead to permanent failures. Examples are resistive open, resistive bridge, capacitive defects, and so on. These defects can be caused by the same phenomena (voids, improper etching, and so on) except that, in this case, the MTJ device can still work but only for a given range of defect sizes.

Other strong or weak defects may occur because of manufacturing issues in the magnetic layers or due to loss of margin in the CMOS circuitry. In this case, the magnetic orientation of the MTJ cells is fixed to a specific configuration so that their magnetic orientation (i.e., resistances) cannot be changed [40]. Note that these defects are sometimes classified in the literature as intracell (within a cell) or intercell (cell-to-cell) defects [41], [42]. Intracell defects refer to resistive opens and shorts on lines inside a cell. Intercell defects refer to resistive shorts between the nodes of the victim cell and those of an aggressor cell.

2) Parametric Failures: Manufacturing process variation is another source of defectiveness issues. As the manufacturing of MRAM requires two different fabrication process technologies, namely a magnetic process for the MTJs and a CMOS process for the access transistors and peripheries, the characteristics of this memory technology can be

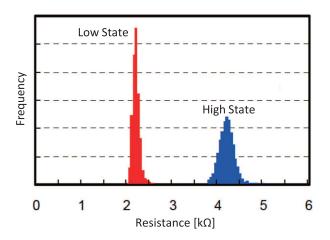

Fig. 4. Low- and high-resistance distributions of MTJs [48].

affected by variations due to the combined effect of these two processes. Permanent faults in MRAM can be caused by extreme parametric variations, as described in [43] and [44]. These variations come from changes in both material and lithographic properties, transistor electrical properties, and noise generated by thermal effects [41], [42]. MTJ material parameters that may suffer from variations are magnetic anisotropy, saturation magnetization, TMR ratio, and oxide thickness of the ultrathin insulating layer. Lithographic parameters that may suffer from variations are the planar dimensions of the MTJ and the length and width of the access transistor. The main transistor electrical parameter that may suffer from variations is the threshold voltage of the access transistor. These variations not only significantly affect the memory operations, such as read/write delays [45]-[47] and retention capabilities, but also lead to hard faults making the cell permanently damaged.

# **B.** Reliability Issues

Reliability is a key issue for the commercial success of MRAM technology. Various reliability issues associated with MRAM are discussed subsequently.

1) Impact of Process Variations: The access behavior of MRAM highly depends on the properties of the MTJ device, which can be affected by variations in its geometrical dimensions, such as its cross-sectional area, the tunneling oxide thickness, and the volume of the FM layer. As described previously, variations in these parameters result in significant deviations in MTJ conductance and switching threshold current. For instance, as per the resistance distributions shown in Fig. 4, the resistance values can be deviated up to 4% [48] from its nominal values. Due to the influence of process variation, the MTJ properties, such as resistance, TMR ratio, and switching delay, can be affected [45]–[47]. At the manufacturing level, the reliability of an MRAM cell can be degraded

by: 1) device parameter deviations due to errors of lithography or etching process; 2) thermal disturbance [38]; and 3) dielectric breakdown. These phenomena may lead to TMR fluctuation, endurance degradation, data disturbance, retention failure, and so on [49], [50], which, in turn, may lead to access errors during the MRAM operations.

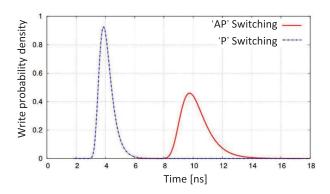

2) Stochastic Switching: The switching of an MTJ is stochastic in nature [51]–[53], and the switching time is randomly distributed. Nevertheless, the write time, which is primarily dependent on the clock period, has a fixed value for a synchronous design. Hence, due to the stochastic switching nature, some memory cells may not complete state transitions in a given write period, which can result in write errors [54], [55]. The write error rate can be expressed as follows [52]:

WER<sub>bit</sub>

$$(t_{\rm w}) = 1 - \exp\left[\frac{-\pi^2 \cdot (I-1) \cdot \Delta}{4(I \cdot e^{C(I-1)t_{\rm w}} - 1)}\right]$$

(2)

$$I = \frac{I_{\rm w}}{I_{\rm c}} \tag{3}$$

where  $t_{\rm w}$  is the write latency, C is a technology-dependent parameter, I is the ratio of the write current ( $I_{\rm w}$ ) to the critical current ( $I_{\rm c}$ ), and  $\Delta$  is the thermal stability factor. The switching success probability is a function of switching current, write period, thermal stability factor, and other material parameters. The write latency distribution for a single STT-MRAM cell used as a case study is shown in Fig. 5. As shown in the figure, these distributions have very long tails [51], and hence, a large write period is required to achieve the specified write reliability. Note that increasing the write current and/or write pulse duration are the most effective methods to reduce write failure.

3) Retention Failure: Retention failure is most likely due to the inherent thermal instability of MRAM, which can lead to MTJ resistance state switching without memory access. The retention failure mechanism can be formally

Fig. 5. Write latency distribution due to stochastic behavior for both antiparallel and parallel switching of a single-bit cell [51].

Table 3 Typical FFMs in an STT-MRAM [41], [42]

| Fault Model                | Affects                                                                               | Key Cause                                                              |

|----------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Transition Fault (TF)      | Write                                                                                 | Relative weak write current due to stray resistive paths               |

| Coupling Fault (CF)        | Write                                                                                 | Neighboring cells switching                                            |

| Stuck-at Fault (SF)        | Write                                                                                 | Intermediate note, word-line stuck-at VDD or GND                       |

| Incorrect Read Fault (IRF) | Read                                                                                  | Current miscorrelation due to defects affecting word-line and bit-line |

| Read Disturb Fault (RDF)   | Read Electrical disturbance at intermediate node due to larger than normal read curre |                                                                        |

expressed as follows:

$$P_{\rm rf} = 1 - \exp\left(-\frac{t_{\rm rf}}{\tau \cdot e^{\Delta}}\right) \tag{4}$$

where  $P_{\rm rf}$  is the failure probability for a specific retention time, that is,  $t_{\rm rf}$ ,  $\tau$  is the attempt period (about 1 ns),  $\Delta$  is thermal stability factor, and  $\tau \cdot e^{\Delta}$  is the average retention time. As shown in the formula, a higher thermal stability  $\Delta$  can result in a longer retention time.

4) Read Disturbance: A read disturbance occurs when an MTJ cell is accidentally switched during a read operation [56], [57]. Note that an incorrect read value may also occur due to a read decision failure. The read disturbance can be described as

$$P_{\rm rd} = 1 - \exp \frac{-t_{\rm read}}{\tau} \times \exp \left[ \frac{\Delta (I_{\rm read} - I_{\rm c})}{I_{\rm c}} \right]$$

(5)

where  $I_{\rm read}$  is the read current,  $I_{\rm c}$  is the critical switching current,  $t_{\rm read}$  is the read pulse duration, and  $\Delta$  is the thermal stability factor.

5) Other Transient Failures: Some other issues may occur during the manufacturing process that may lead to the above-mentioned transient failures. Unlike permanent failures, these failures can be recovered after their occurrences. They are called transient faults, and the correct state of the cell can be eventually recovered in the following memory accesses [39]. These faults can be caused by defects introduced during the polishing process or the magnetic stack deposition and annealing process [58].

To summarize, uncertainties in reliability can lead to performance degradation, higher production cost, and time-to-market penalties. Therefore, it is necessary to pinpoint and address these reliability issues for MRAM chip design to guarantee the final product yield.

# C. MRAM Fault Models

In general, faults in memories are modeled as functional faults in which functional tests can be used to detect those faults. These functional tests for a given set of functional fault models (FFMs) can be performed using a systematic approach that is essential to increase the yield and reliability of memories. Functional faults refer to the deviation of the observed memory behavior from the functionally

specified one under a set of operations. There are a list of operations that are also known as operation sequence and a list of corresponding deviations that are termed faulty behavior for each FFM [51].

FFMs in MRAMs can be classified as static or dynamic and single or double cells impacting, depending on their behavior. Static single-cell FFMs describe faults sensitized using a single operation on a faulty cell. Conversely, dynamic FFMs are faults sensitized by performing more than one operation in sequence. On the other hand, double-cell FFMs are faults consisting of two-cell fault primitives in which the victim cell is the one that shows the faulty behavior, whereas the aggressor cell is the one that produces this behavior. A comprehensive description of all these FFMs for SRAM that also applies to MRAM can be found in [59].

The most common types of MRAM FFMs are the following: Stuck At "0" (SAF0), Stuck At "1" (SAF1), and transition fault (TF), which leads to permanent faults. Undefined write fault (UWF), write disturb fault (WDF), read disturb fault (RDF), incorrect read fault (IRF), and retention fault (RF) are those leading to disturb faults [39], [41], [60]. A detailed description of the nonfunctional behavior associated with each of these FFMs can be found in [39]. As an example, Chintaluri et al. [41], [42] have identified FFMs that may occur during read and write operations in an STT-MRAM and how resistive and capacitive defects induce faults. Table 3 summarizes the FFMs and how they contribute to read/write failures. Moreover, in [61], based on the defect injection scheme, defect characterization and fault modeling considering layouts for STT-MRAM are presented. In this analysis, a dynamic read fault behavior is demonstrated in which multiple vectors for excitation and detection are required. This read fault behavior happens in the case of intercell coupling faults (CFs).

Note that several other FFMs can be found in the literature for different types of MRAM technologies. In [62], two new FFMs related to the magnetic junction behavior of Toggle-MRAM were identified. They were proposed to model multivictim fault (MVF) and kink fault (KF). In MVF, a cluster of cells can change their magnetization state due to the impact of process variations, whereas, in KF, the MTJ resistivity changes due to the shrinkage of the hysteresis loop because of its relation with the cell shape. In [63], transition CFs and incorrect read CFs were found and modeled for TAS-MRAM. Inversion CF (ICF) in two

cells occurs when the logic value of the victim cell is inverted after a transition due to a write operation that is performed on the aggressor cell, which was identified in STT-MRAM [41].

# IV. EXISTING TEST SOLUTIONS FOR MRAMS

Due to their regular structures, there exists a typical test development methodology for SRAMs [59]. The three main steps of this methodology are defect analysis, fault modeling, and development of test (e.g., March) algorithms. Defect analysis is usually done by using information collected after physical failure analysis (PFA) of defective memories. Note that this analysis can also be done by using a physical model of the memory and by subsequently performing defect injection campaigns. Fault modeling consists in finding an appropriate FFM for each type of defect encountered during defect analysis. Finally, the March test algorithms are developed to cover all possible FFMs that can be found in a given memory technology. The main goal here is to have the lowest complexity for the March algorithms with the highest FFM coverage. Note that this approach has also been used for other types of memories, such as DRAM, Flash, RRAM, or PCM [64]-[66].

In the context of MRAM, the same methodology can apply. This has been done for Toggle-MRAMs that are already in mass production, and the embedded STT-MRAM will soon enter into mass production [67]-[69]. Details will be given in Sections IV-A-IV-C. Concerning TAS-MRAM, the same methodology has been used to develop test solutions, despite the fact that TAS-MRAM has never (and will never) been into mass production. To this purpose, fault injection campaigns instead of PFA information have been used during defect analysis. Details will be given in Section IV-B. However, an interesting feature in the development of test solutions for these memories is that, very often, the same FFMs have been identified, even if defects or misbehaviors at the origin of the observed errors may differ depending on the MRAM technology. Consequently, the March test algorithms developed for a given technology, including TAS-MRAM, are likely to be utilized to test other memory technologies.

#### A. Test Solutions for Toggle-MRAM

The only study about Toggle-MRAM fault modeling and testing was presented in [62], [70], and [71]. In these articles, the authors first performed a classification and analysis of defects and their behavior and proposed corresponding fault models [62]. Defect injections were done by considering.

- 1) Resistive shorts, such as wordlines and bitlines, are shorted to either  $V_{dd}$  or  $V_{ss}$ .

- Stuck-on and stuck-off on the read access transistor of the MTJ cell.

- 3) Line break (open) on the write wordlines, read wordlines, or bitlines of the memory array.

- 4) Coupling on the same layer, that is, between the write wordlines, between the read wordlines, and between the bitlines.

- 5) MTJ device defects, such as MTJ opens, MTJ tunneling defects, and rough junction defects.

Defect injections were done on a real layout considering the physical model of a toggle MTJ cell, with parameters gathered from an experimental process. Simulation results in terms of the correlation between defects and fault models showed that most of the defects can be modeled by stuck-at faults, except MVF and KF for which two new FFMs were proposed, as mentioned in Section III-C. The proposed test solution for these FFMs consisted of a March C- algorithm applied with a 100% write current to detect stuck-at and MVF faults and the same algorithm applied with a 90% write current for KF detection.

In their subsequent study, the authors presented chip measurement results to prove the existence of write disturbance faults [70], [71]. They proposed the WDF model for toggle MRAM to represent the behavior of faults that affect data stored in MRAM cells when an excessive magnetic field is applied during the write operation on the neighboring cells. Then, they proposed a SPICE macromodel for the MTJ cell of the toggle MRAM to carry out circuit simulations. Finally, they developed an MRAM fault simulator, called RAMSES-M, able to derive a March 17N test algorithm (N being the number of cells in the memory array), which is described in the following:

$$\updownarrow (w0); \uparrow (r0, w1, r1); \updownarrow (r1); \uparrow (r1, w0, r0); \updownarrow (r0);$$

$$\downarrow (r0, w1, r1); \uparrow (r1); \downarrow (r1, w0, r0); \uparrow (r0)$$

where  $\uparrow$  (resp.  $\Downarrow$ ) denotes an increasing (resp. decreasing) addressing order of the various cells in the memory array for the corresponding march element composed of one or more read/write operations,  $\updownarrow$  denotes an irrelevant address order, w0 (w1) denotes a write 0 (write 1) in a cell, and v0 (v1) denotes reading a cell with expected value 0 (value 1). A March element (nine in the above algorithm) is a sequence of operations applied to each cell in the memory before proceeding to the next cell.

The algorithm was proposed not only to test WDF in addition to SAF, TF, coupling, and address decoder faults but also to distinguish WDF from other faults, especially SAF0. The test was shown to be more efficient compared with the conventional March C algorithm. Since other emerging nonvolatile memory technologies, such as RRAM and PCM, may suffer from SAF or WDF as well, similar testing solutions can also be applied effectively [36], [72].

#### **B.** Test Solutions for TAS-MRAM

The only study about TAS-MRAM fault modeling and testing was presented in [23], [63], [73]–[77]. A preliminary step in this study was to develop a TAS-MTJ model in order to, subsequently, be able to perform electrical simulations [78]. Magnetization dynamics, as well

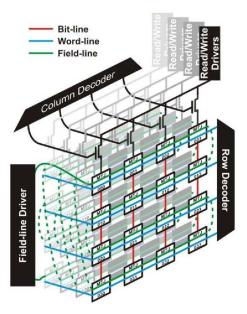

Fig. 6. TAS-MRAM architecture [73]-[77].

as dependencies of tunneling conductance, were considered during the development of this model, which was validated and calibrated with silicon data provided by Crocus Technologies. During this step, heat diffusion in such devices was also studied as TAS-MTJ relies on the blocking temperature concept.

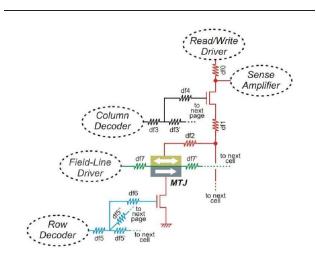

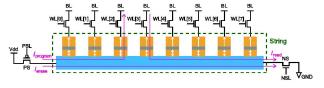

The next step was to analyze the failure mechanisms of TAS-MRAMs through defect injections (resistiveopen, resistive-bridge, and coupling-based resistive-open defects) in a representative TAS-MRAM architecture. Fig. 6 depicts a typical TAS-MRAM architecture, organized in a square matrix with  $2^{MR}$  rows and  $2^{NC}$  columns, for a total storage capacity of  $2^{MR+NC}$  bits per page, where MR and NC are the number of bits used to specify the row and column address, respectively. Each cell in the array is connected to one of the row-lines (namely, wordlines) and connected to one of the column-lines (namely, bitlines). A particular set of MTJs can be accessed for a read or write operation by selecting its wordline and bitline. There is only one field line that connects all MTJs serially: 1) row by row and 2) passing through all pages in the architecture. Defect injections were made taking into account both magnetic and CMOS fabrication processes, as well as architecture properties, such as wires and cell neighboring. Not surprisingly, the analysis of failure mechanisms showed that both read and write operations may be affected by the injected defects.

Fig. 7 illustrates how and where resistive-open defects on various interconnects of the memory array were injected. The defects are those that directly impact MTJ's heat current (from df0 to df2), those that indirectly impact the MTJ's heat current (from df3 to df6), and those that impact field-line current (df7 and df7'). The TAS-MRAM operation may be affected by these resistive-open defects in several ways, and all details can be found in [75]. Similar injection campaigns were carried out for resistive-bridge and coupling defects [63], [76].

From the results of the fault injection campaigns, the following step consisted in performing fault modeling. Standard static fault models, such as SAF and TF models, were identified. Moreover, a WDF model related to the write procedure that requires heating the device above its blocking temperature was also identified. In addition, a less restrictive static CF was also observed in which, irrespective of the stored data in the aggressor cell, the victim cell fails to perform a "write 0" operation. Moreover, both dynamic transition coupling and dynamic incorrect read CFs were observed. In those cases, the aggressor cell should be accessed immediately before the victim cell. Finally, a dynamic write disturb CF was also observed. However, in this case, the aggressor cell should be accessed immediately after the victim cell.

Based on the observed failure mechanisms, a full set of FFMs specific to TAS-MRAM was identified, and a March 14N test algorithm targeting these specific FFMs was proposed. It is reported in the following:

$$\underbrace{ \underbrace{ (w0); \underbrace{\uparrow}_{M1} (r0, w1); \underbrace{\uparrow}_{M2} (w1, r1, w0, r0, w1); \underbrace{\uparrow}_{M3} (w0, r0);}_{M5} \underbrace{ \underbrace{\uparrow}_{M6} (w1, r1); \underbrace{\downarrow}_{M6} (r1, w1)}_{M6}$$

where M1 is the initialization march element used to reset all cells to 0, and M2-M6 are the various march elements of the proposed algorithm used to test all the target FFMs. In this algorithm, each static FFM is covered as follows.

- 1) SAF1: If r0 in M2 returns "data 1."

- 2) WDF1: w1, w1, and r1 sequence (M3 with the help of w1 in M2) when the second w1 toggles the cell to "data 0," which is observed by the read operation.

Fig. 7. Resistive-open defects injection [75].

Fig. 8. Test algorithm generation flow [61], [79].

- 3) SAFO: If r1 in M3 returns "data 0."

- 4) *TFO and CFtr0*: w0 and r0 sequence in M3 when the read operation returns "data 1."

Regarding dynamic FFMs, they can be covered in a similar manner (details can be found in [77]). Finally, faults in the address decoder are covered by M1, M2, and M6.

#### C. Test Solutions for STT-MRAM

Compared with Toggle-MRAM and TAS-MRAM, a higher number of test solutions for STT-MRAM can be found in the literature. These solutions can be classified as: 1) test generation methods; 2) BIST techniques; and 3) Design-for-Testability (DfT) techniques. They are briefly described in the following.

1) Test Generation Methods: A test generation method has been proposed in [61] and [79] to cover all faults that are specific to STT-MRAM. As a preliminary step, the impact of process variations and test conditions, namely the temperature and voltage, on the defect manifestation were fully quantified. The spot defects in the layout and their manifestation as resistive opens and shorts in the netlist, as well as the impact of MTJ defects on the functionality of memory arrays, have been analyzed. This analysis showed the existence of dynamic read fault behavior requiring multiple test vectors for fault excitation and detection. This type of fault happens in the case of intercell CFs. In addition, write faults have been shown to be very sensitive to the test voltage and temperature, and a low-voltage and low-temperature condition is representing the worst case scenario in their framework.

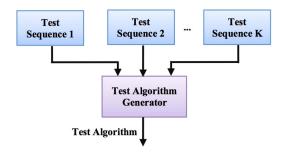

Based on the results of this analysis, and after appropriate fault modeling, the authors constructed an efficient test algorithm that provides full coverage of the observed faults. They built this algorithm based on the set of test sequences identified during the fault modeling process. To this end, several March test sequences were constructed to detect different classes of STT-MRAM specific faults. Finally, a combined test algorithm for testing all the modeled faults was developed (see Fig. 8).

2) BIST Techniques: BIST techniques presented in [80]–[82] were developed to perform *in situ*, statistical, retention failure testing of large STT-MRAM arrays.

A retention failure is the consequence of a bit-flip in a cell, a stochastic phenomenon, caused by thermal noise. Since the retention time is exponentially proportional to the thermal stability, testing of retention failures consists in measuring the thermal stability of a cell by applying a weak write current to that cell. Naeimi *et al.* [40] have proposed a retention test method with weak write current based on the thermal activation model proposed in [83]. Since the thermal activation is a stochastic phenomenon, a lot of successive tests are required to acquire statistically significant data. Thus, retention test time for cells with high thermal stability increases exponentially. Although performing a parallel test at a subarray level can reduce retention test time, the test time is still a major bottleneck for this method.

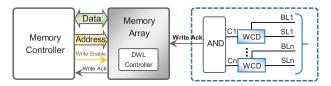

In order to alleviate the retention test time problem, Yoon *et al.* [80], Yoon and Raychowdhury [81], and Hamdioui *et al.* [82] proposed a new MBIST architecture that performs retention testing of large STT-MRAM arrays in a time-efficient manner. The proposed MBIST scheme reduces retention time considerably by: 1) applying weak write current to multiple rows in an array and 2) conducting a read operation only when a fault is detected within the rows under test.

The retention test is divided into two phases: error detection (ED) and error search (ES). In the MBIST architecture, the corresponding logic for ED and ES is included in the control logic. Based on the outputs of the MBIST circuit, an ED (err det) signal is asserted by ED logic, and while this signal is asserted, the ES phase is performed. ES logic controls which rows to assert to localize the error and it outputs error location to the output of control logic once it identifies error locations. A search done signal is asserted if ES is finished and it resets err det signal. An IWWR (weak write current) bus controls the voltage of bitline and wordline, leading to different magnitudes of IWWR current. Columns with different resistors serve as references to find errors in blocks of rows, and temperature sensors are placed inside a subarray to monitor the temperature. Each characterization test, which determines the thermal stability, is qualified by temperature. The proposed scheme enables parallelism in the test process and allows a fine tradeoff between the localization of weak cells and test time. More explanations about the ED and ES processes can be found in [80] and [81]. The proposed MBIST shows a 93.75% improvement in retention test time compared with the brute-force approach in [40] with less than 5% estimation error.

3) DfT Techniques: The DfT technique presented in [84] targets RDF detection. Read disturb is a major reliability issue in which a read operation on a given cell can lead to a bit-flip because read and write currents share the same path. As read disturb has a dependence on various important design parameters, such as write current, read current, retention, and readability, a reduction in the read disturb rate always leads to design compromises. Moreover, with

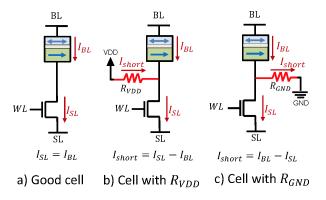

Fig. 9. STT-MRAM cell with different short defects [85], [86]. (a) Good cell. (b) Cell with  $R_{VDD}$ . (c) Cell with  $R_{GND}$ .

a reduction technique, it is not possible to eliminate read disturb entirely. Hence, it must be detected to attain a reliable memory. Therefore, the authors proposed a dynamic circuit-level approach that tracks the read current and, thus, is able to detect read disturb. This is possible as an RDF changes the resistance of the affected bit-cell, which, in turn, affects the read current. As a consequence, the ratio of the actual read current to the reference current of the sense amplifier will flip. This observation is exploited by the proposed detection circuitry to create an error signal, which indicates the occurrence of a read disturb. Since the read current is unidirectional, read disturb can only affect one logic value. Therefore, the read disturb detection (RDD) circuit is only activated for that particular logic value, which results in a very low power penalty. Moreover, there is no timing penalty as the read detection circuit is isolated from the actual read process by using a current mirror.

The whole RDD circuit consists of five parts: a basic equalizer circuit, a sense amplifier used to read the bit-cell content, the detection circuit itself, a control logic used to enable the detection circuit only for read operations that can be affected by a read disturb, and a self-test mechanism to test the functionality of the RDD circuit. More details about the implementation and operational modes of this RDD circuit can be found in [84].

Experimental results show that the proposed RDD technique can detect up to 95% of the total RDFs and imposes negligible area and power overhead.

Another DfT technique has been proposed in [85] and [86] to test bridging defects in STT-MRAMs. The authors have modeled resistive-short defects between the internal node of an STT-MRAM cell and an external node. These types of defects are modeled by a resistive connection between the internal node of the cell and either  $V_{dd}$  ( $R_{V_{dd}}$ ) or Gnd ( $R_{Gnd}$ ). This test method is based on the fact that a resistive-short defect between an external node and the internal node of the memory cell changes the amount of the current flowing into the cell (through the bitline terminal) and outside of the cell (through the source-line terminal). Fig. 9 shows the behavior of a cell

with different short defects. A fault-free cell behaves as a single current path, in which the current from the read circuitry at the bitline terminal flows through the MTJ and the access transistor until the source-line terminal. In the case of  $R_{V_{dd}}$  short, the current is injected to the cell so that ISL becomes greater than  $I_{BL}$ . Similarly, in the case of  $R_{\mathrm{Gnd}}$  short, its current is removed from the cell, and IBL becomes greater than ISL. A faulty read operation happens when the voltage generated for reading an antiparallel state ("1") becomes lower than the reference voltage or when the voltage generated for reading a parallel state ("0") becomes larger than the reference voltage.

Based on this observation, the authors proposed to change the basic columnwise readout circuitry so that it can measure the difference between the current flowing into and out of any cell in the respective column. A large current difference signals the presence of a defect.

The modified read circuitry exploits differential current amplifiers that are placed between the reference part and the memory cell part of the read circuitry. The modified circuit has three modes of operation: normal mode, Test mode 1 to detect an  $R_{V_{dd}}$  short, and Test mode 2 to detect an  $R_{\rm Gnd}$  short. This method is robust to process variations and can detect resistive open and short defects. More details can be found in [85] and [86].

4) Test Solutions for SOT-MRAM: To the best of our knowledge, there is no solution published so far for testing SOT-MRAM.

# V. EXISTING RELIABILITY IMPROVEMENT SOLUTIONS FOR MRAMS

To enhance the reliability of MRAM, many innovative and effective solutions have been proposed from the device level, circuit level, and architectural level. In the following, we first summarize the related work that has been done in terms of reliability modeling and evaluation. The second part of this section describes existing reliability solutions for STT-MRAM, which is the mainstream MRAM technology, and the final part will be dedicated to reliability solutions for more advanced technology, for example, SOT-MRAM, racetrack memory, and skyrmion. Note that although the following reliability enhancement solutions were proposed for MRAMs, similar solutions can be applied or extended to other emerging nonvolatile memories (e.g., RRAM and PCM) as well.

## A. Reliability Modeling and Evaluation Methodologies of MRAM

1) PVT Modeling and Evaluation Techniques: An accurate and efficient reliability modeling and evaluation method is essential to pinpoint the bottleneck and the most fatigue part in the system. Especially, the characteristics of FM materials, such as TMR, are very sensitive to environmental temperature, which has already been observed in many experiments, such as in [87]. Wu et al. [88] proposed a thermal model of MTJ validated by published experimental measurements and found a significant read disturbance in the deep submicrometer regime. A bodybiased feedback sensing amplifier was also proposed to improve read reliability at high temperatures. Similarly, Zhang et al. [89] quantitatively investigated read/write errors of a single STT-MRAM cell caused by process variations and temperature with commercial EDA tools on a 45-nm technology node. Based on this work, a thermalaware sensing circuit was proposed to reduce the read errors due to PVT variations [90]. Considering the heating mechanism of PCM, the thermal disturbance should also be mitigated [2]. Indeed, with technology scaling and shrinking of the distance between cells, the thermal disturbance will become more severe for PCM. Some reliability solutions mentioned in this article may be extended to PCM to alleviate this problem.

Xie et al. [91] claimed that the stochastic switching of the MTJ under the STT effect is severely affected by the thermal noise under the room temperature. They proposed the numerical Fokker-Planck-based simulation framework to study the thermal effect in MTJ switching of STT-MRAM. A comparison with other simulation methods was also given in this article. In addition, thermal variation and Joule heating on the reliability of STT-MRAM were explored [92]. Extensive simulations revealed the close relationship of STT-MRAM read/write failures and thermal fluctuations. Kong et al. [93] investigated the impact of process variations on the MTJ with the Object-Oriented MicroMagnetic Framework (OOMMF) and SpinFlow3D and showed that geometrical modifications can greatly improve the MTJ performance. An STT-MRAM cache reliability evaluation framework was built in [94] not only considering the correlation of retention failure, read disturbance, and write failure but also taking into account the diversity of running benchmarks and process variations among different memory cells. Their experimental results indicated that the error rate may vary up to 32× among different benchmarks and process variations of memory cells contribute another 6.5× difference in cache vulnerability.

Moreover, reliability is especially challenging in some applications, such as automotive, military, and aerospace, which may suffer from extreme temperature conditions. The self-heating effect of MTJ stack has been observed in [95] and investigated through 1-D numerical thermal simulations. Unlike the TAS approach in which the MTJ is heated by an external element, here, the MTJ can be heated by itself due to the Joule heating. Despite the efforts dedicated to technology optimization in the past years, a high current density flowing through the MTJ is always demanded by most of the switching mechanisms. This leads to a significant self-heating effect that may cause functional errors in hybrid MTJ/CMOS circuits [96].

2) Dielectric Breakdown of STT-MRAM: Dielectric breakdown is another critical reliability issue that determines the lifetime of devices (transistors or MTJs). As MTJ

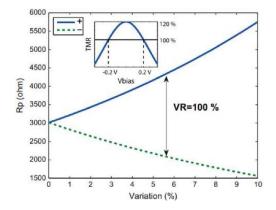

Fig. 10. Relationship of: 1) resistance of MTJ and oxide barrier thickness variation and 2) TMR and bias voltage for reading (the embedded subplot) [37].

is a memristive device and its resistance mainly comes from the oxide barrier, the voltage applied on MTJ is almost imposed on the insulator (MgO). A dielectric breakdown has attracted significant attention for other resistive memories, such as RRAM and PCM [97]–[99]. With the shrinking of technology nodes and oxide dielectric thickness (~1 nm), the breakdown voltage also scales down, and it is necessary to mitigate time-dependent dielectric breakdown (TDDB) of the MTJ caused by write operations [100].

Several experiments have analyzed the TDDB effect in STT-MRAM [101], [102], and other experiments have been performed to explore the physical mechanism behind the TDDB phenomenon in STT-MRAM [103]. It has been found that TDDB depends on a variety of factors, such as annealing temperature, oxide material purity, tunnel barrier thickness, stress voltage, temperature, and stress duration. Variability of oxide barrier thickness also leads to reliability degradation, as the resistance has an exponential dependence on the thickness. Furthermore, a bias voltage for reading can greatly reduce the TMR [37], as shown in Fig. 10. Ho et al. [104] investigated the reliability issue caused by dielectric breakdown or TDDB effect and built an accurate TDDB model to analyze the time to breakdown and the postbreakdown currents. Simulation results revealed that new design constraints need to be imposed for better reliability of STT-MRAM. Munira et al. [52] analyzed the factors affecting the reliability of the writing process in STT-MRAM array, including process variations, thermally activated initial angle, thermal fluctuations, and the voltage across the MTJ. A quasi-analytical model was built to calculate the current and energy during the write operation for TDDB evaluations.

3) Radiation Effect on STT-MRAM: With the emergence of MRAM products, some new reliability issues have been observed, such as radiation effect. Hirose *et al.* [105] estimated the risk of irradiative particle bombardments, that is, alpha particles and neutrons, which are the well-known

soft error sources on the ground, with respect to both frequencies and the hazardous effects of bombardments. The effect of proton and Cr ion radiation on MTJs was investigated in [106], which concluded that an in-plane MTJ is robust to proton irradiation but the properties of an MTJ can be degraded by Cr ion irradiation.

4) Reliability Measurements on Prototypes: Some reliability modeling studies with prototype measurements were also reported. An error behavior model used to characterize read/write errors of STT-MRAM was proposed in [107]. The proposed model, which was validated by measurements on Everspin MRAM chips, revealed that, in a normal environment, the error rate is very low and dominated by read error, but the write error rate dramatically increases with the magnetic disturbance. Their research highlighted the necessity of protecting STT-MRAM from magnetic disturbance or attack. An 8-Mb embedded STT-MRAM prototype was tested under package-level reliability stress, magnetic stress, and radiation stress [108]. The measurements showed that their prototype had a negligible fail bit count (FBC) even without ECC protection and was suitable for mass production. These studies indicate that the STT-MRAM fabrication process is approaching commercial maturity.

# B. Reliability Solutions From the Device and **Fabrication Process Perspectives**

There are many works trying to improve the MRAM reliability from device fabrication optimization and material engineering perspectives. Mahawar et al. [109] observed that the conventional fabrication process of MRAM is based on bulk or SOI technology, which may not be suitable for MRAM that requires a large switching current. They improved the fabrication process by introducing the fully depleted (FD) silicon carbide (4H-SiC) substrate NMOS technology to increase the driving current effectively. The experimental results showed that the new process has a very low probability of thermal fatigue and device failure and can reduce the write error rate by 45%. Plasma oxidation was proved to be an effective method to produce Al-metal-based MTJ with ultrauniform resistance [110]. Interface engineering is another efficient way to improve the write and read reliability [111]. The performance of MTJs can be significantly enhanced through proper modulation of heavy metal/FM metal interface, such as perpendicular magnetic anisotropy, TMR, and magnetic damping.

Gonçalves et al. [110] established a simulation framework based on the Landau-Lifshitz-Gilbert (LLG) equations that can solve the magnetic dynamics selfconsistently. With this framework, the authors explored different magnetic materials to construct the MTJ stack and illustrated the requirement for the coupled free-layer MTJ stacks in scaled technology nodes. In addition, Augustine et al. [112] presented a design space exploration framework for STT-MRAM, in which they performed

Table 4 Comparison Results for BCH and Hamming Coding Schemes With an Encoded Number of Bits of 128 [113]

|                    | Hamming<br>(Correction-bit = 1) | BCH (Correction-bit = 2) |

|--------------------|---------------------------------|--------------------------|

| Latency (ns)       | 1.3                             | 3.6                      |

| Area $(um^2)$      | 4907                            | 106700                   |

| Dynamic power (mW) | 0.11                            | 1.10                     |

| Leakage (mW)       | 0.12                            | 2.24                     |

a numerical study on four types of MTJ stacks and evaluated their advantages, as well as the limitations from the perspective of memory applications.

# C. Reliability Solutions From the Coding Theory **Perspective**

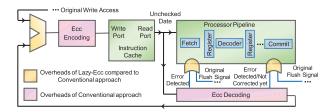

Error correction code (ECC) is widely used in SRAM and DRAM to enhance the access reliability, and among many, Hamming and Bose-Chaudhuri-Hocquenghem (BCH) are the most popular coding theories. Hamming codes are to detect two bits (with the help of an additional parity bit) and correct only a single bit in the code-word, whereas BCH is typically employed when multiple bit correction capabilities are required. These coding schemes require an additional encoding/decoding mechanism, and their synthesized results for the same are shown in Table 4. Moreover, the impact on read and write latencies of L1 and L2 MRAM-based caches due to various coding schemes is illustrated in Table 5. The unidirectional read disturbance switching and asymmetrical  $0 \rightarrow 1$  and  $1 \rightarrow$ 0 switching in the write operation provide opportunities for ECC code optimization in STT-MRAM. Mei et al. [115] proposed a polar code to reduce the error rate caused by process variation and thermal fluctuation. Compared with Hamming, BCH, and LDPC codes, the proposed polar code can induce lower decoding complexity and approach flexible code rates to be adaptive to different raw error rates of STT-MRAM chips. Sayed et al. [116] also took advantage of unidirectional read disturbance switching and asymmetrical  $0 \rightarrow 1$  and  $1 \rightarrow 0$  switching and devised a unidirectional ED code instead of conventional ECC code to reduce the latency and storage overhead. With the proposed technique, both reliability and access performance of STT-MRAM can be improved dramatically.

Table 5 Read and Write Latencies of 64-Bit STT-MRAM L1 and L2 Caches With 16- and 512-KB Capacities [114]

|                   |                                 |                                                                               | ECC1         | ECC2         | ECC3                                                                                                                                                                                                                                                                                                                                                                                                               | ECC4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|---------------------------------|-------------------------------------------------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |                                 |                                                                               |              | BCH          | BCH                                                                                                                                                                                                                                                                                                                                                                                                                | BCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Storage overheads |                                 | 0%                                                                            | 11%          | 18.9%        | 25.5%                                                                                                                                                                                                                                                                                                                                                                                                              | 31%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Write [ns]        | ECC Encoding                    | _                                                                             | 0.400        | 0.525        | 0.530                                                                                                                                                                                                                                                                                                                                                                                                              | 0.545                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | Memory Write                    | 11.610                                                                        | 6.456        | 4.909        | 4.100                                                                                                                                                                                                                                                                                                                                                                                                              | 3.628                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | Overall                         | 11.610                                                                        | 6.856        | 5.434        | 4.630                                                                                                                                                                                                                                                                                                                                                                                                              | 4.173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |