## On-chip integration of Si/SiGe-based quantum dots and electronic circuits for scaling

Xu, Y.

**Publication date**

**Document Version** Final published version

Citation (APA)

Xu, Y. (2021). On-chip integration of Si/SiGe-based quantum dots and electronic circuits for scaling. [Dissertation (TU Delft), Delft University of Technology].

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## ON-CHIP INTEGRATION OF SI/SIGE-BASED QUANTUM DOTS AND ELECTRONIC CIRCUITS FOR SCALING

## ON-CHIP INTEGRATION OF SI/SIGE-BASED QUANTUM DOTS AND ELECTRONIC CIRCUITS FOR SCALING

## Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus, Prof.dr.ir.T.H.J.J. van der Hagen, chair of the Board for Doctorates to be defended publicly on Monday 22 November 2021 at 10:00 o'clock

by

## Yuanxing XU

Master of Science in Electrical Engineering, Delft University of Technology, the Netherlands, born in Nanjing, China. This dissertation has been approved by the promotors.

### Composition of the doctoral committee:

Rector Magnificus, chairperson

Prof.dr.ir. L. M. K. Vandersypen,

Dr. R. Ishihara,

Delft University of Technology, promotor

Delft University of Technology, copromotor

Independent members:

Prof.dr. P. French, Delft University of Technology Prof.dr. R. B. Staszewski, Delft University of Technology

Prof.dr.ir. F. A. Zwanenburg, University of Twente

Dr. F. Sebastiano, Delft University of Technology Dr.ir. M. Veldhorst, Delft University of Technology

Keywords: floating gate, quantum dots, integration, scalability

Printed by: Gildeprint

Cover designed by: Fan Zheng

Copyright © 2021 by Yuanxing Xu

ISBN 978-94-6419-370-1

An electronic version of this dissertation is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## **CONTENTS**

| Su | ımma                     | ary                                                                                                                                                                                                                                            | vii                                                |

|----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Sa | men                      | vatting                                                                                                                                                                                                                                        | ix                                                 |

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | Interfacing spin qubits in quantum dots Cross-bar addressing and charge-locking Main device in this study Thesis outline erences                                                                                                               | 1<br>1<br>2<br>4<br>4<br>5                         |

| 2  | 2.1                      | kground  Electron spin qubits in quantum dots                                                                                                                                                                                                  | 11<br>11<br>12<br>14<br>16<br>17<br>18<br>20<br>22 |

| 3  | <b>Proc</b> 3.1          | rences                                                                                                                                                                                                                                         | 25<br>25<br>26<br>28<br>31<br>33<br>36<br>36<br>39 |

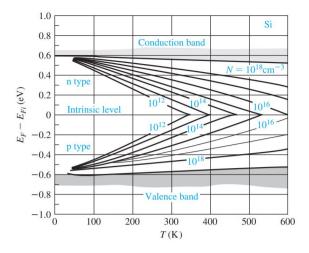

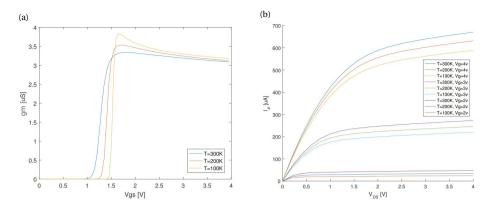

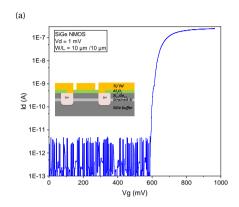

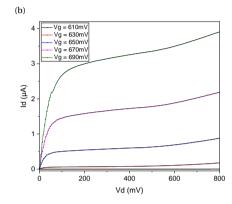

| 4  | 4.1<br>4.2<br>4.3<br>4.4 | ice characterization  Expected transistor temperature dependence.  Characterization of single transistors.  4.2.1 Transfer and output curves  4.2.2 Hysteresis issue  Characterization of single quantum dots.  Transistor on-off voltage set. | 41<br>41<br>44<br>48<br>48<br>49                   |

vi Contents

| 5   |       | antum dot with a floating plunger gate                               | 51  |

|-----|-------|----------------------------------------------------------------------|-----|

|     | 5.1   | Voltage accuracy                                                     | 51  |

|     |       | 5.1.1 Channel charge injection                                       | 53  |

|     |       | 5.1.2 Gate-source parasitic capacitance                              | 54  |

|     |       | 5.1.3 Noise analysis                                                 | 55  |

|     | 5.2   | Discharging rate and leakage path                                    | 57  |

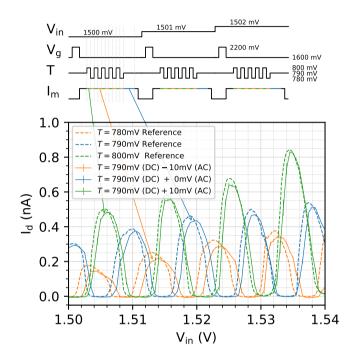

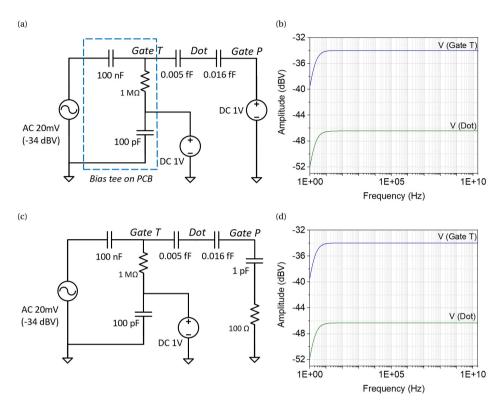

|     |       | Fast line operation in the floating period                           | 60  |

|     |       | 5.3.1 Calibration                                                    | 61  |

|     |       | 5.3.2 Experiment                                                     | 62  |

|     |       | 5.3.3 AC simulation                                                  | 64  |

|     | Refe  | erences                                                              | 65  |

| 6   | Den   | nultiplexer and interconnect for a scalable interface                | 67  |

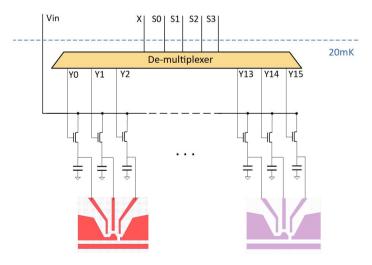

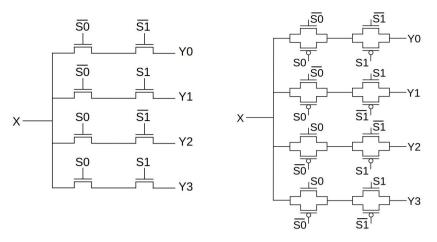

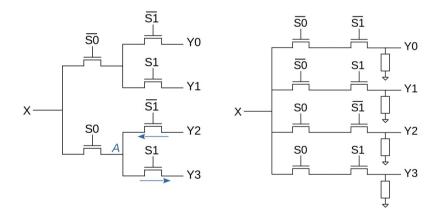

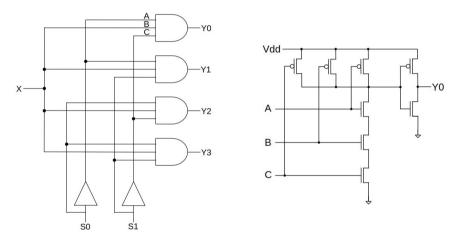

|     | 6.1   | Demultiplexer Structures and Requirements                            | 68  |

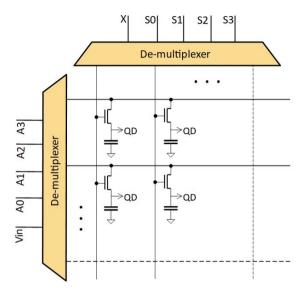

|     | 6.2   | Sparse Dot Array                                                     | 70  |

|     |       | 6.2.1 Array operation and line scaling                               | 71  |

|     |       | 6.2.2 Heat dissipation of a unit cell                                | 73  |

|     | Refe  | erences                                                              | 75  |

| 7   | Con   | nclusion and Outlook                                                 | 77  |

|     |       | Conclusion                                                           | 77  |

|     | 7.2   | On-going work and Outlook                                            | 78  |

|     |       | 7.2.1 Off-chip integration                                           | 78  |

|     |       | 7.2.2 Single-shot readout of a partially floating qubit              | 80  |

|     |       | 7.2.3 A fully floating single quantum dot with gate addressing       | 82  |

|     |       | 7.2.4 summary                                                        | 83  |

|     | Refe  | erences                                                              | 83  |

| Ac  | knov  | wledgements                                                          | 85  |

| A   | Flov  | wchart of Quantum dots with floating gates, processed in VLL         | 89  |

| В   | Flov  | wchart of Quantum dots with floating gates, processed in EKL and VLL | 95  |

| Cı  | ırric | ulum Vitæ                                                            | 99  |

| Lie | st of | Publications                                                         | 101 |

## **SUMMARY**

With continuous breakthroughs in quantum science and technology in recent years, the development of quantum computers is moving from pure scientific research to engineering realization. Meanwhile, the underlying physical structures also develop from the initial single qubit to multiple qubits or medium-scale qubit registers. Since qubits are operated by many sophisticated instruments under strict environmental conditions, people need a scalable solution to support many qubits working at the same time, so as to achieve high computing speed for a practical quantum computer.

The physical qubits we discuss in this study are realized by spin states of electrons confined in Si/SiGe based quantum dots, which has good compatibility with the semiconductor fabrication technology. We focus on the wiring bottleneck for scaling the qubits. Specifically, in a normal operation mode, every qubit requires at least one wire connected to the control electronics at higher temperature stages. When scaling towards a fault-tolerant quantum computer, which needs hundreds of thousands of quantum dots, simply adding more wires and electronics would face space constraints in the connection from the sample to the sample carrier and dilution refrigerator. To reduce the number of wires needed, we explore a DRAM-like circuit to bias the quantum dot gates. A single voltage supply line connected at the input of a demultiplexer can provide different voltages to several DRAM-like cells sequentially, while the switched-capacitor circuits are used to float the gate of the dots, isolate them from the voltage supply, and store the voltage locally on the capacitors. We aim for all the elements to be integrated on Si/SiGe based substrate and functional at the same cryogenic temperature as the dots.

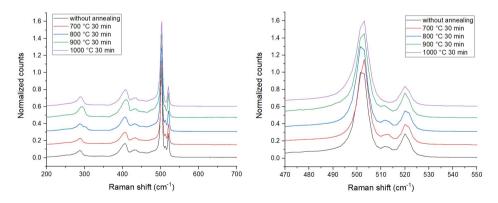

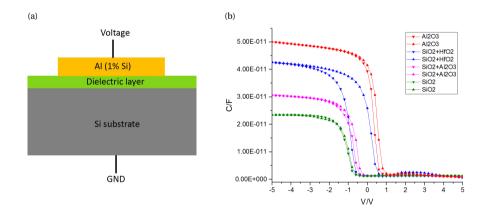

As a proof of concept, we make devices with a floating plunger gate of a single quantum dot. We develop processes to monolithically fabricate parallel plate capacitors, transistors and quantum dot devices on a Si/SiGe heterostructure. The processes combine electron-beam and photolithography to define tens of nanometer and micrometer scale structures, respectively. We discuss temperature limitations to prevent strain relaxation in the substrate while having a functional doping area. Furthermore, we compare several dielectric materials to make gate oxide with fewer defects and lower leakage current.

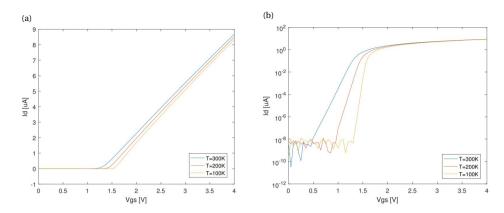

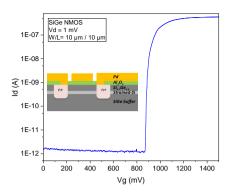

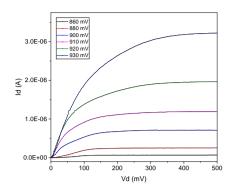

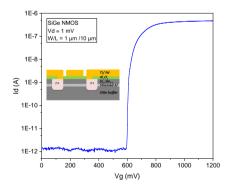

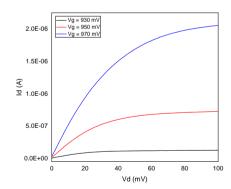

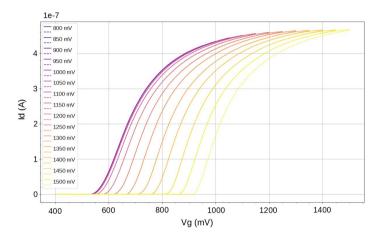

Then we characterize discrete transistors and quantum dots before the measurement of combined devices. We first simulate the temperature dependency of transistor threshold voltage and field-effect mobility. Then we measure the transfer and output curves from several batches of devices along with the process development. We observe a higher turn-on voltage and higher field-effect mobility for transistors working at cryogenic temperatures as expected. We also notice a hysteresis when scanning to higher voltages. Thus, defining a stable operation range is necessary. Besides, We measure single quantum dots without floating gates to obtain their bias voltage range and charging energy.

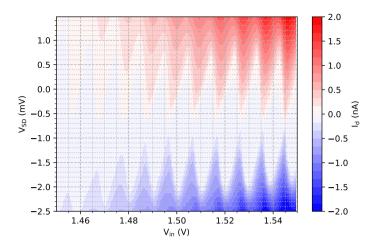

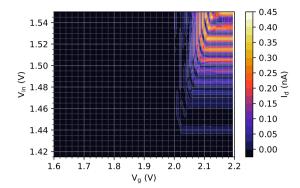

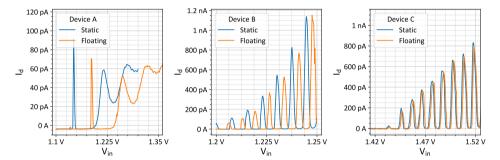

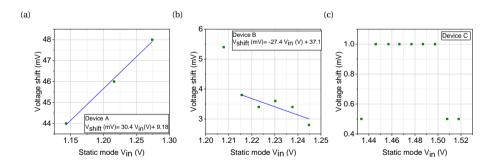

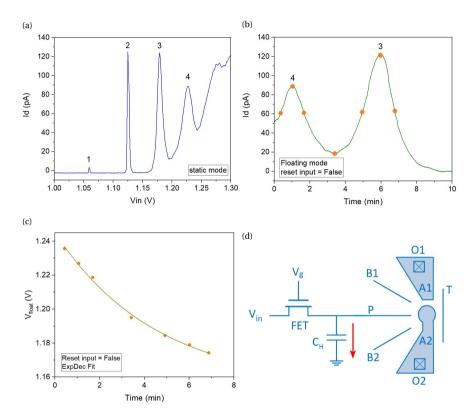

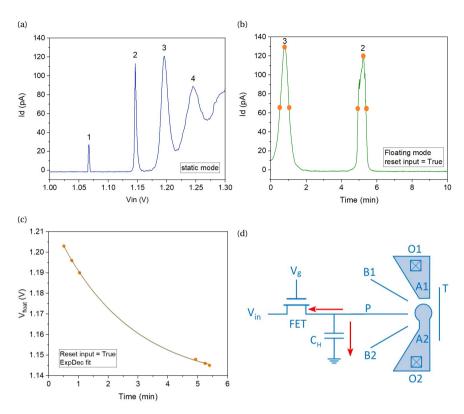

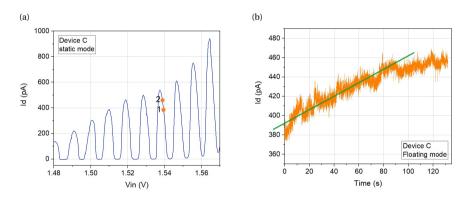

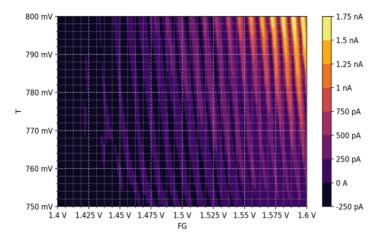

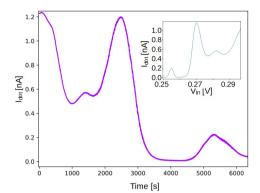

After that, we measure the devices that combine a switched-capacitor circuit and a single quantum dot. We observe Coulomb peak shifts in voltage between the static viii Summary

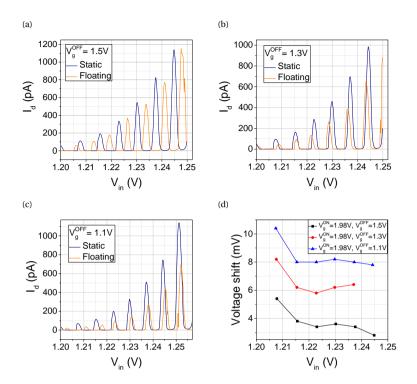

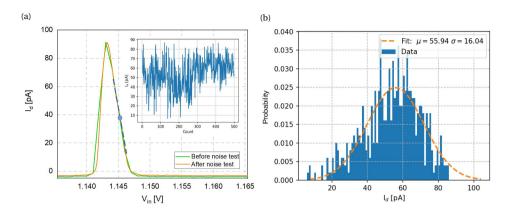

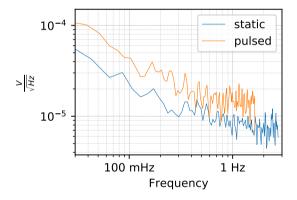

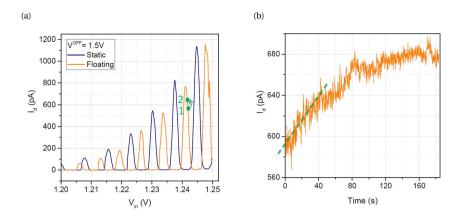

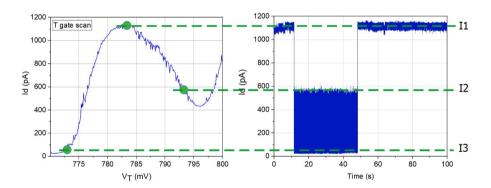

and floating test mode. We analyze the parameters that affect the offsets by comparing devices with different transistor and capacitor sizes. The device with the largest capacitance and smallest transistor channel provides the least systematic offsets. The random components in the offsets are mainly introduced by the 1/f noise. In addition, we apply a pulsed voltage to one of the quantum dot gates while floating another gate. We extract Coulomb peaks corresponding to the high and low voltage levels of the pulses and find that the electrochemical potential of the quantum dot can follow the voltage pulses, which is essential for applying the floating gate strategy in qubit experiments.

We move on to discuss designs for demultiplexers connected to a quantum dot array. The structure of an on-chip integrated demultiplexer depends on the demultiplexing signal and the available technology given the constraints of integration with quantum dots. Furthermore, a sparse dot array is proposed to provide more space for the electronic circuits on-chip. Taking a specific unit cell design for concreteness, we calculated the required number of signal lines and power dissipation under general assumptions.

This work shows that integrating a DRAM-like floating gate structure with quantum dots on-chip has the potential to overcome the wiring bottleneck in scaling. In the end, we discuss some alternative approaches for biasing a large number of quantum dot gates with a reduced number of wires.

## **SAMENVATTING**

Met voortdurende doorbraken in kwantumwetenschap en -technologie in de afgelopen jaren, gaat de ontwikkeling van kwantumcomputers van puur wetenschappelijk onderzoek naar technische realisatie. Ondertussen ontwikkelen de onderliggende fysieke structuren zich ook van de eerste enkele qubit tot meerdere qubits of middelgrote qubitregisters. Omdat qubits worden bediend door veel geavanceerde instrumenten onder strikte omgevingsomstandigheden, hebben mensen een schaalbare oplossing nodig om veel qubits tegelijkertijd te ondersteunen, om een hoge rekensnelheid te bereiken voor een praktische kwantumcomputer.

De fysieke qubits die we in deze studie bespreken, worden gerealiseerd door spintoestanden van elektronen die zijn opgesloten in op Si/SiGe gebaseerde kwantumdots, die goed compatibel zijn met de halfgeleiderfabricagetechnologie. We richten ons op de bedradingsbottleneck voor het schalen van de qubits. In een normale bedrijfsmodus vereist elke qubit met name ten minste één draad die is aangesloten op de besturingselektronica bij hogere temperatuurtrappen. Bij het opschalen naar een fouttolerante kwantumcomputer, die honderdduizenden kwantumdots nodig heeft, zou het eenvoudigweg toevoegen van meer draden en elektronica te maken krijgen met ruimtebeperkingen in de verbinding van het monster naar de monsterdrager en verdunningskoelkast. Om het aantal benodigde draden te verminderen, onderzoeken we een DRAM-achtig circuit om de quantum dot-poorten te beïnvloeden. Een enkele voedingslijn aangesloten op de ingang van een demultiplexer kan achtereenvolgens verschillende spanningen leveren aan verschillende DRAM-achtige cellen, terwijl de circuits met geschakelde condensatoren worden gebruikt om de poort van de stippen te laten zweven, ze te isoleren van de voedingsspanning en op te slaan de spanning plaatselijk op de condensatoren. We streven ernaar dat alle elementen worden geïntegreerd op Si/SiGe-gebaseerd substraat en functioneel zijn bij dezelfde cryogene temperatuur als de stippen.

Als proof of concept maken we apparaten met een zwevende plunjerpoort van een enkele kwantumdot. We ontwikkelen processen om monolithisch parallelle plaatcondensatoren, transistors en quantum dot-apparaten te fabriceren op een Si/SiGe-heterostructuur. De processen combineren elektronenstraal en fotolithografie om respectievelijk tientallen nanometer- en micrometerschaalstructuren te definiëren. We bespreken temperatuurbeperkingen om spanningsrelaxatie in het substraat te voorkomen terwijl we een functioneel dopinggebied hebben. Verder vergelijken we verschillende diëlektrische materialen om poortoxide te maken met een lagere lekstroom en minder defecten.

Vervolgens karakteriseren we discrete transistoren en kwantumdots vóór de meting van gecombineerde apparaten. We simuleren eerst de temperatuurafhankelijkheid van transistordrempelspanning en veldeffectmobiliteit. Vervolgens meten we de overdrachtsen uitvoercurves van verschillende batches apparaten samen met de procesontwikkeling. We zien een hogere inschakelspanning en een hogere veldeffectmobiliteit voor transistors die werken bij cryogene temperaturen zoals verwacht. Ook merken we een

x Samenvatting

hysterese bij het scannen naar hogere spanningen. Het definiëren van een stabiel werkbereik is dus noodzakelijk. Bovendien meten we enkele kwantumdots zonder zwevende poorten om hun voorspanningsbereik en laadenergie te verkrijgen.

Daarna meten we de apparaten die een geschakeld condensatorcircuit en een enkele kwantumdot combineren. We observeren Coulomb-piekverschuivingen in spanning tussen de statische en zwevende testmodus. We analyseren de parameters die de offsets beïnvloeden door apparaten met verschillende transistor- en condensatorformaten te vergelijken. Het apparaat met de grootste capaciteit en het kleinste transistorkanaal zorgt voor de minste systematische offsets. De willekeurige componenten in de offsets worden voornamelijk geïntroduceerd door de 1/f-ruis. Bovendien passen we een gepulseerde spanning toe op een van de quantum dot-poorten terwijl we een andere poort laten zweven. We extraheren Coulomb-pieken die overeenkomen met de hoge en lage spanningsniveaus van de pulsen en ontdekken dat de elektrochemische potentiaal van de kwantumdot de spanningspulsen kan volgen, wat essentieel is voor het toepassen van de zwevende poortstrategie in qubit-experimenten.

We gaan verder met het bespreken van ontwerpen voor demultiplexers die zijn aangesloten op een kwantumdot-array. De structuur van een on-chip geïntegreerde demultiplexer hangt af van het demultiplexsignaal en de beschikbare technologie gezien de beperkingen van integratie met kwantumdots. Verder wordt een spaarzame dot-array voorgesteld om meer ruimte te bieden voor de elektronische schakelingen op de chip. Met een specifiek eenheidscelontwerp voor concreetheid, hebben we het vereiste aantal signaallijnen en vermogensdissipatie berekend onder algemene aannames.

Dit werk laat zien dat het integreren van een DRAM-achtige zwevende poortstructuur met kwantumdots op de chip het potentieel heeft om het bedradingsprobleem bij het schalen te overwinnen. Uiteindelijk bespreken we enkele alternatieve benaderingen voor het voorinstellen van een groot aantal quantum dot-poorten met een verminderd aantal draden.

1

## INTRODUCTION

A quantum computer is a machine that performs computation using the principles of quantum mechanics. The concept was first proposed by Richard Feynman in the 1980s. Prior to that, quantum physics had been developed for more than half a century. Feynman mentioned that nature is not classical, so it is better to use quantum mechanical systems to simulate quantum phenomena[1]. Although this idea became the quantum simulation branch later, quantum computers started to develop as an important application of quantum technology since then.

Quantum computers have received widespread attention in recent years because of their powerful computing capabilities in specific fields. Unlike classical computers that encode data with bits (either 0 or 1), quantum computers use quantum bits (qubits) based on the principle of superposition, allowing 0 and 1 to exist simultaneously. As a result, it requires  $2^n$  complex amplitudes to describe the state of n qubits. This offers quantum computers a significant advantage in data processing. They are able to solve problems that classical computers cannot solve efficiently, such as factoring very large numbers[2, 3]. In addition, since the 1970s, the density of transistors and computing power roughly doubled every two years following Moore's Law. However, with the device sizes further reduced to 5-7 nanometer scale, the influence of quantum effects, such as transistor gate leakage due to quantum tunnelling, became serious. The updating speed of new devices in the semiconductor industry is therefore slowing down[4–7]. People expect the development of quantum computers to be one of the solutions to the continuation of ever increasing computing power.

## 1.1. Interfacing spin qubits in quantum dots

A qubit is the basic unit of information in a quantum computer. At present, its physical implementation is inconclusive. There are several promising options including superconducting qubits[8, 9], spin qubits in quantum dots[10, 11], trapped ions[12, 13], position-based charge qubits [14, 15] and so on. People in general use the DiVincenzo

criteria to evaluate a physical qubit system, which describes that qubits need to have long coherence times, a universal gate set, be able to be initialized and read out. In addition, they are also required to have a good scalability [16]. That is, firstly, the properties of single qubits remain the same as the number of qubits grows. Secondly, a scalable interface between qubits and classical electronics to properly address and control each particular qubit [17].

The qubits we focus on in this study is implemented by the spin of single electrons in quantum dots (QDs). To form the quantum dots, voltages are applied to metal gates to define the potential landscape in the semiconductor substrate[18]. Such spin qubits hold the advantage of good compatibility with current semiconductor fabrication techniques and potential for easy integration with classical electronics[19–21]. Spin qubits based on Si/SiGe substrates have already been demonstrated to satisfy most of the Di-Vincenzo criteria [22–26]. Their promising results prompt people to investigate strategies to control a large number of qubits.

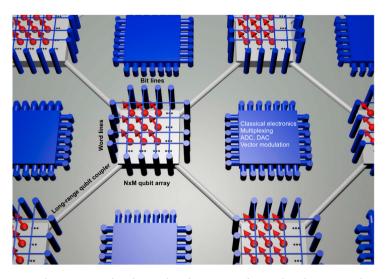

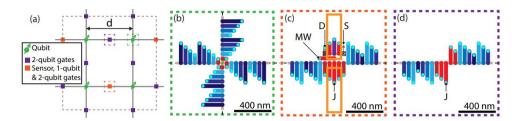

Since qubits are very sensitive to thermal noise, they generally work at temperatures around 10 mK in a dilution refrigerator. To further avoid errors during computation, quantum error correction algorithms are introduced, which needs thousands of physical qubits to encode one logical qubit. Therefore, it is estimated that millions of physical qubits are required to build a fault-tolerant quantum computer [27, 28]. Connecting signal lines of each qubit from the coldest plate in the refrigerator directly to electronic instruments at room temperature would lead to fan-out and routing issues. Besides, excessive heat would be introduced through signal lines to quantum devices. Many solutions are proposed to solve these problems in scaling, including making hot qubits that working at temperatures in the 1-4 K range[29, 30] or bringing down the front-end of control electronics to deep-cryogenic temperature stages [31, 32]. One possible strategy is depicted in Fig.1.1 [33]. Groups of spin qubits are arranged in dense two-dimensional arrays and controlled using a cross-bar addressing scheme (we will discuss it in detail in the next section). Then these arrays are sparsely placed and communicate via longrange qubit couplers [34-37]. Such a layout provides more space for electronics on-chip and routing. The functions of the integrated electronics depend on the actual space and thermal budget. Demultiplexers would be a priority since they can effectively reduce the number of wires going off the chip. Besides, analog to digital converters (ADC), digital to analog converters (DAC), and vector modulation are also expected in close proximity for a more compact quantum computing system [38, 39].

## 1.2. CROSS-BAR ADDRESSING AND CHARGE-LOCKING

For every dot in a typical quantum dot array, one gate controls the electrochemical potential and a second controls the tunnel barrier to the next dot in the array. Even if quantum dots are designed to be identical, the required gate bias voltage still differs among the dots due to non-uniformities in the substrate and variations during the fabrication process. With a small number of quantum dots, each gate is connected to a separate room temperature DAC through the bond wires from the chip to the sample carrier and the dilution refrigerator wiring. However, this linear approach poses a bottleneck in scaling. By comparison, today's classical processor has billions of transistors integrated and operated on a single chip, while only about 2000 contact pins are used for the in-

Figure 1.1: Dense qubit arrays are placed sparsely to leave spaces for on-chip electronics. The arrays are addressed locally by bit and word lines. Communication among the qubit blocks is via long-range qubit couplers. The operating temperature is considered to be four Kelvin given the heat generated by the electronic circuits and the current cooling power of a dilution refrigerator [33].

put/output signals. This large ratio between active components and pins is described by Rent's rule and is made possible by implementing shared control methods [40]. In order to operate the millions of qubits for practical quantum computation, similar methods will therefore have to be implemented in quantum integrated circuits.

Inspired by the matrix of dynamic random access memory (DRAM) that uses word lines and bit lines to address a large number of storage cells [42], proposals for controlling spin qubits using the cross-bar structure exist [41, 43, 44]. Another concept that can be borrowed from classical electronics is charge-locking. In DRAM, the stored voltage encodes a "0" or "1", according to a threshold. In contrast, the voltage maintained on a quantum dot gate needs to be a precise analog value. The required precision of such a stored voltage ranges from 1  $\mu$ V to 1 mV, depending on the gate function and coupling of the gate to the dot potential. Charge-locking is thus used in the form of a sample-and-hold circuit. When the input line is electrically detached, the gate of the quantum dot is floating and the voltage maintains there for a certain period. Figure 1.2 is an example that uses the cross-bar scheme and charge-locking circuit to address a spin qubit matrix from the third dimension[41].

Although the primary role for DC gates of quantum dots is to achieve electron confinement, additional voltage pulses must be applied to these gates for qubit experiments. For example, in a commonly used single-shot read-out method to determine the state of an electron spin, a few kHz signal is applied to the gate to load, read and empty a quantum dot [45, 46]. When an electronic circuit is integrated with these gates as an interface, the extra transistor or capacitor should not affect the voltage pulses arriving at the quantum dot gates. Prototypes have been made with on-chip or off-chip integrated floating gate circuits and GaAs quantum dots [47, 48]. For silicon-based quantum dots,

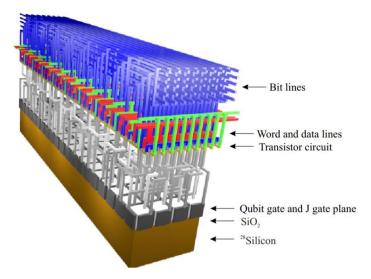

Figure 1.2: Architecture of a quantum-classical interface. The bottom purified silicon layer ( $^{28}$ Silicon) hosts qubits, which are controlled by metal gates isolated by the SiO<sub>2</sub> layer. Signals to the qubit gates are transferred through the cross-bar structure and switched-capacitor circuits in the higher layers [41].

switching circuits have been integrated with quantum devices on-chip [49, 50]. In addition, charge-storage devices and quantum devices have been fabricated using the same CMOS process and connected through wire bonds [51, 52]. However, a fully on-chip integrated solution, without the need for wire bonds, is still waiting to be achieved.

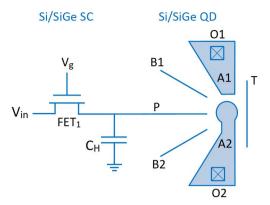

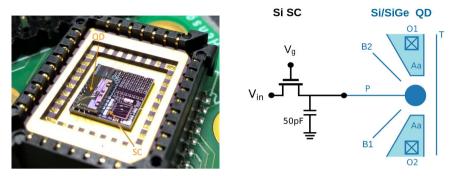

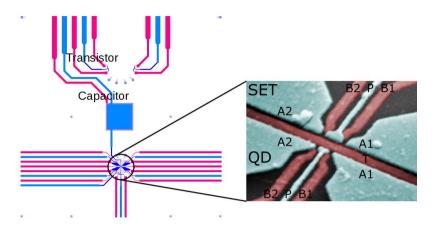

### **1.3.** Main device in this study

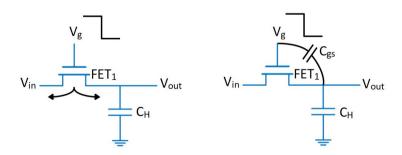

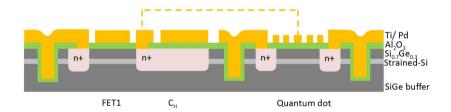

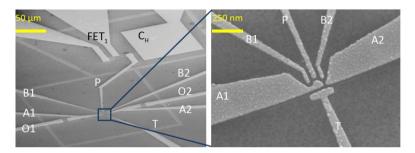

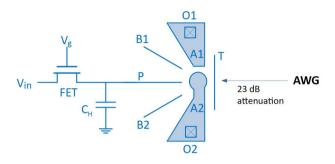

In this study, we implement a switched-capacitor (SC) circuit for charge-locking and use it to float the plunger gate of a single quantum dot. Here we integrate the circuit and the dot on a Si/SiGe-based substrate. The device schematic is shown in Fig.1.3. The SC circuit contains an n-type transistor  $FET_1$  and a parallel-plate holding capacitor  $C_H$ . The accumulation (A1 and A2), barrier (B1 and B2) and T gates of the QD are connected to voltage sources at room temperature in the later experiments. (We introduce the quantum dot structure in detail in Section 2.1.1. The layout and cross-section of the combined device are provided in Section 3.1.) Gate P is connected to the output of the SC circuit. It is regarded as a floating gate in the following contents. We analyze the parameters that affect the variability of the floating gate voltage and experimentally study the impact of the size of the capacitor and the transistor. In addition, we apply a pulsed voltage to one of the quantum dot gates while floating another gate, as a relevant test for qubit measurements.

## 1.4. THESIS OUTLINE

After the introduction in Chapter 1, background information is provided in Chapter 2. Here we review the working principle of spin qubits and switched-capacitor circuits, fol-

Figure 1.3: Schematic of a device fabricated in this study, a switched-capacitor circuit is connected to gate P of a single quantum dot.

lowed by considerations of voltage accuracy on the floating node and power consumption of the device.

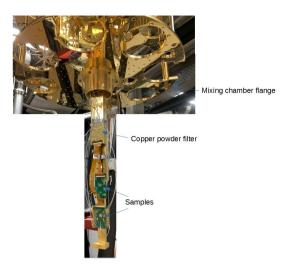

In Chapter 3, we firstly give an overview of the device fabrication process. Then a few parameters are discussed in detail including the temperature limitation during the process, conditions to activate the implantation areas and options for the dielectric layers. Setups for the device measurements are also introduced here.

Chapter 4 starts with a discussion about transistor temperature dependence. Then we present results of the characterization on separated quantum dots, transistors and capacitors from several batches.

Results of the combined devices are reported in Chapter 5. We analyze the parameters that affect the variability of the floating gate voltage. After that, we check the dot potential modulation in response to a voltage pulse while the dot is partially floating.

In Chapter 6, we discuss structures for the demultiplexer, followed by a proposal for a sparse quantum dot array, intended to allow for scaling up to one million qubits. Taking a unit cell from the array, we particularly discuss its line scaling and heat dissipation. Finally, we conclude in Chapter 7 and propose future works.

#### REFERENCES

- [1] R. P. Feynman, *Simulating physics with computers*, International Journal of Theoretical Physics **21**, 467 (1982).

- [2] C. H. Bennett and D. P. DiVincenzo, *Quantum information and computation*, Nature **404**, 247 (2000).

- [3] P. W. Shor, Algorithms for quantum computation: discrete logarithms and factoring, in Proceedings 35th Annual Symposium on Foundations of Computer Science (1994) pp. 124–134.

- [4] G. E. Moore, *Cramming more components onto integrated circuits*, Electronics **38**, 114 (1965).

6

- [5] C. A. Mack, *Fifty years of moore's law*, IEEE Transactions on Semiconductor Manufacturing **24**, 202 (2011).

- [6] J. R. Powell, *The quantum limit to moore's law,* Proceedings of the IEEE **96**, 1247 (2008).

- [7] J. Carballo, W. J. Chan, P. A. Gargini, A. B. Kahng, and S. Nath, *ITRS 2.0: Toward a reframing of the semiconductor technology roadmap*, in 2014 IEEE 32nd International Conference on Computer Design (ICCD) (2014) pp. 139–146.

- [8] M. H. Devoret and R. J. Schoelkopf, *Superconducting circuits for quantum information: An outlook*, Science **339**, 1169 (2013).

- [9] F. Arute et al., Quantum supremacy using a programmable superconducting processor, Nature **574**, 505 (2019).

- [10] D. Loss and D. P. DiVincenzo, *Quantum computation with quantum dots*, Phys. Rev. A **57**, 120 (1998).

- [11] L. M. K. Vandersypen and M. Eriksson, *Quantum computing with semiconductor spins*, Physics Today **72**, 38 (2019).

- [12] C. D. Bruzewicz, J. Chiaverini, R. McConnell, and J. M. Sage, *Trapped-ion quantum computing: Progress and challenges*, Applied Physics Reviews **6**, 021314 (2019).

- [13] N. Friis, O. Marty, C. Maier, C. Hempel, M. Holzäpfel, P. Jurcevic, M. B. Plenio, M. Huber, C. Roos, R. Blatt, and B. Lanyon, *Observation of entangled states of a fully controlled 20-qubit system*, Phys. Rev. X **8**, 021012 (2018).

- [14] I. Bashir, E. Blokhina, A. Esmailiyan, D. Leipold, M. Asker, E. Koskin, P. Giounanlis, H. Wang, D. Andrade-Miceli, A. Sokolov, A. Koziol, T. Siriburanon, and R. B. Staszewski, *A single-electron injection device for cmos charge qubits implemented in 22-nm fd-soi*, IEEE Solid-State Circuits Letters **3**, 206 (2020).

- [15] R. B. Staszewski, I. Bashir, E. Blokhina, and D. Leipold, *Cryo-cmos for quantum system on-chip integration: Quantum computing as the development driver*, IEEE Solid-State Circuits Magazine **13**, 46 (2021).

- [16] D. P. DiVincenzo, *The physical implementation of quantum computation*, Fortschritte der Physik **48**, 771 (2000).

- [17] D. J. Reilly, Challenges in scaling-up the control interface of a quantum computer, in 2019 IEEE International Electron Devices Meeting (IEDM) (2019) pp. 31.7.1–31.7.6.

- [18] F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. L. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, *Silicon quantum electronics*, Rev. Mod. Phys. **85**, 961 (2013).

REFERENCES 7

[19] R. Pillarisetty, N. Thomas, H. C. George, K. Singh, J. Roberts, L. Lampert, P. Amin, T. F. Watson, G. Zheng, J. Torres, M. Metz, R. Kotlyar, P. Keys, J. M. Boter, J. P. Dehollain, G. Droulers, G. Eenink, R. Li, L. Massa, D. Sabbagh, N. Samkharadze, C. Volk, B. P. Wuetz, A.-M. Zwerver, M. Veldhorst, G. Scappucci, L. M. K. Vandersypen, and J. S. Clarke, Qubit device integration using advanced semiconductor manufacturing process technology, in IEEE International Electron Devices Meeting (IEDM) (2018).

- [20] M. Eriksson, S. Coppersmith, and M. Lagally, *Semiconductor quantum dot qubits*, MRS Bulletin **38**, 794–801 (2013).

- [21] A. M. J. Zwerver, T. Krähenmann, T. F. Watson, L. Lampert, H. C. George, R. Pillarisetty, S. A. Bojarski, P. Amin, S. V. Amitonov, J. M. Boter, R. Caudillo, D. Corras-Serrano, J. P. Dehollain, G. Droulers, E. M. Henry, R. Kotlyar, M. Lodari, F. Luthi, D. J. Michalak, B. K. Mueller, S. Neyens, J. Roberts, N. Samkharadze, G. Zheng, O. K. Zietz, G. Scappucci, M. Veldhorst, L. M. K. Vandersypen, and J. S. Clarke, *Qubits made by advanced semiconductor manufacturing*, (2021), arXiv:2101.12650.

- [22] E. Kawakami, P. Scarlino, D. R. Ward, F. R. Braakman, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, *Electrical control of a long-lived spin qubit in a si/sige quantum dot*, Nature Nanotechnology **9**, 666 (2014).

- [23] T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, *A programmable two-qubit quantum processor in silicon*, Nature **555**, 633 (2018).

- [24] X. Xue, T. F. Watson, J. Helsen, D. R. Ward, D. E. Savage, M. G. Lagally, S. Coppersmith, M. A. Eriksson, S. Wehner, and L. M. K. Vandersypen, *Benchmarking gate fidelities in a Si/SiGe two-qubit device*, Physical Review X **9**, 201011 (2019).

- [25] D. M. Zajac, A. J. Sigillito, M. Russ, F. Borjans, J. M. Taylor, G. Burkard, and J. R. Petta, *Resonantly driven CNOT gate for electron spins*, Science **359**, 439 (2018).

- [26] J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, *A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than* 99.9%, Nature Nanotechnology 13, 102 (2018).

- [27] F. Jazaeri, A. Beckers, A. Tajalli, and J. Sallese, A review on quantum computing: From qubits to front-end electronics and cryogenic mosfet physics, in 2019 MIXDES 26th International Conference "Mixed Design of Integrated Circuits and Systems" (2019) pp. 15–25.

- [28] A. G. Fowler, M. Mariantoni, J. M. Martinis, and A. N. Cleland, *Surface codes: Towards practical large-scale quantum computation*, Phys. Rev. A **86**, 032324 (2012).

- [29] L. Petit, J. M. Boter, H. G. J. Eenink, G. Droulers, M. L. V. Tagliaferri, R. Li, D. P. Franke, K. J. Singh, J. S. Clarke, R. N. Schouten, V. V. Dobrovitski, L. M. K. Vandersypen, and

8

- 1

- M. Veldhorst, *Spin lifetime and charge noise in hot silicon quantum dot qubits*, Phys. Rev. Lett. **121**, 076801 (2018).

- [30] C. H. Yang, R. C. C. Leon, J. C. C. Hwang, A. Saraiva, T. Tanttu, W. Huang, J. Camirand Lemyre, K. W. Chan, K. Y. Tan, F. E. Hudson, K. M. Itoh, A. Morello, M. Pioro-Ladrière, A. Laucht, and A. S. Dzurak, *Operation of a silicon quantum processor unit cell above one Kelvin*, Nature **580**, 350 (2020).

- [31] E. Charbon, F. Sebastiano, A. Vladimirescu, H. Homulle, S. Visser, L. Song, and R. M. Incandela, *Cryo-CMOS for quantum computing*, in *2016 IEEE International Electron Devices Meeting (IEDM)* (2016) pp. 13.5.1–13.5.4.

- [32] J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and D. J. Reilly, *Cryogenic control architecture for large-scale quantum computing*, Phys. Rev. Applied 3, 024010 (2015).

- [33] L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, and M. Veldhorst, *Interfacing spin qubits in quantum dots and donors hot, dense, and coherent*, npj Quantum Information 3, 34 (2017).

- [34] G. Zheng, *Circuit Quantum Electrodynamics with Single Electron Spins in Silicon*, Ph.D. thesis, Delft University of Technology (2021).

- [35] N. Samkharadze, G. Zheng, N. Kalhor, D. Brousse, A. Sammak, U. C. Mendes, A. Blais, G. Scappucci, and L. M. K. Vandersypen, *Strong spin-photon coupling in silicon*, Science **359**, 1123 (2018).

- [36] X. Mi, M. Benito, S. Putz, D. M. Zajac, J. M. Taylor, G. Burkard, and J. R. Petta, *A coherent spin–photon interface in silicon*, Nature **555**, 599 (2018).

- [37] A. J. Landig, J. V. Koski, P. Scarlino, U. C. Mendes, A. Blais, C. Reichl, W. Wegscheider, A. Wallraff, K. Ensslin, and T. Ihn, *Coherent spin–photon coupling using a resonant exchange qubit*, Nature **560**, 179 (2018).

- [38] H. Homulle, *Cryogenic electronics for the read-out of quantum processors*, Ph.D. thesis, Delft University of Technology (2019).

- [39] J. P. G. Van Dijk, B. Patra, S. Subramanian, X. Xue, N. Samkharadze, A. Corna, C. Jeon, F. Sheikh, E. Juarez-Hernandez, B. P. Esparza, H. Rampurawala, B. R. Carlton, S. Ravikumar, C. Nieva, S. Kim, H. J. Lee, A. Sammak, G. Scappucci, M. Veldhorst, L. M. K. Vandersypen, E. Charbon, S. Pellerano, M. Babaie, and F. Sebastiano, *A scalable cryo-cmos controller for the wideband frequency-multiplexed control of spin qubits and transmons*, IEEE Journal of Solid-State Circuits **55**, 2930 (2020).

- [40] D. P. Franke, J. S. Clarke, L. M. K. Vandersypen, and M. Veldhorst, *Rent's rule and extensibility in quantum computing*, Microprocessors and Microsystems **67**, 1 (2019).

- [41] M. Veldhorst, H. Eenink, C. Yang, and A. Dzurak, *Silicon CMOS architecture for a spin-based quantum computer*, Nature Communications **8**, 1766 (2017).

- [42] B. Keeth, R. J. Baker, B. Johnson, and F. Lin, *DRAM Circuit Design. Fundamental and High-Speed Topics* (Wiley-IEEE Press, 2007).

- [43] R. Li, L. Petit, D. P. Franke, J. P. Dehollain, J. Helsen, M. Steudtner, N. K. Thomas, Z. R. Yoscovits, K. J. Singh, S. Wehner, L. M. K. Vandersypen, J. S. Clarke, and M. Veldhorst, *A crossbar network for silicon quantum dot qubits*, Science Advances **4**, EAAR 3960 (2018).

- [44] J. M. Boter, J. P. Dehollain, G. van Dijk, T. Hensgens, R. Versluis, J. S. Clarke, M. Veldhorst, F. Sebastiano, and L. M. K. Vandersypen, *A sparse spin qubit array with integrated control electronics*, in *IEEE International Electron Devices Meeting (IEDM)* (IEEE, New York, 2019) pp. 31.4.1–31.4.4.

- [45] J. M. Elzerman, R. Hanson, L. H. Willems van Beveren, B. Witkamp, L. M. K. Vandersypen, and L. P. Kouwenhoven, *Single-shot read-out of an individual electron spin in a quantum dot*, Nature **430**, 431 (2004).

- [46] A. Morello, J. J. Pla, F. A. Zwanenburg, K. W. Chan, K. Y. Tan, H. Huebl, M. Möttönen, C. D. Nugroho, C. Yang, J. A. van Donkelaar, A. D. C. Alves, D. N. Jamieson, C. C. Escott, L. C. L. Hollenberg, R. G. Clark, and A. S. Dzurak, *Single-shot readout of an electron spin in silicon*, Nature 467, 687 (2010).

- [47] R. K. Puddy, L. W. Smith, H. Al-Taie, C. H. Chong, I. Farrer, J. P. Griffiths, D. A. Ritchie, M. J. Kelly, M. Pepper, and C. G. Smith, *Multiplexed charge-locking device for large arrays of quantum devices*, Applied Physics Letters 107, 143501 (2015).

- [48] S. J. Pauka, K. Das, R. Kalra, A. Moini, Y. Yang, M. Trainer, A. Bousquet, C. Cantaloube, N. Dick, G. C. Gardner, M. J. Manfra, and D. J. Reilly, *A cryogenic interface for controlling many qubits*, (2019), arXiv:1912.01299v1.

- [49] H. Al-Taie, L. W. Smith, B. Xu, P. See, J. P. Griffiths, H. E. Beere, G. A. C. Jones, D. A. Ritchie, M. J. Kelly, and C. G. Smith, *Cryogenic on-chip multiplexer for the study of quantum transport in 256 split-gate devices*, Applied Physics Letters **102**, 243102 (2013).

- [50] D. R. Ward, D. E. Savage, M. G. Lagally, S. N. Coppersmith, and M. A. Eriksson, *Integration of on-chip field-effect transistor switches with dopantless Si/SiGe quantum dots for high-throughput testing*, Applied Physics Letters **102**, 213107 (2013).

- [51] S. Schaal, S. Barraud, J. J. L. Morton, and M. F. Gonzalez-Zalba, *Conditional dispersive readout of a cmos single-electron memory cell*, Phys. Rev. Applied **9**, 054016 (2018).

- [52] S. Schaal, A. Rossi, V. N. Ciriano-Tejel, T.-Y. Yang, S. Barraud, J. J. L. Morton, and M. F. Gonzalez-Zalba, *A CMOS dynamic random access architecture for radio-frequency readout of quantum devices*, Nature Electronics **2**, 236 (2019).

## **BACKGROUND**

To make an interface between quantum devices and classical electronics, we provide background information on both aspects. We start with a brief introduction to electron spin qubits. The quantum dot structure and readout scheme that are relevant to the following chapters are described in detail. Then we move on to the switched-capacitor circuits. We discuss the relationship between the floating voltage accuracy and device sizes. In the end, we mention a method to estimate the power dissipation of a switched-capacitor circuit.

## 2.1. ELECTRON SPIN QUBITS IN QUANTUM DOTS

A qubit is a two-level quantum system. In this study, it is implemented with the spin of an electron in a static magnetic field, which takes spin up and spin down as the two basis states, represented by  $|0\rangle$  and  $|1\rangle$  below. The superposition state of a qubit can be described as

$$|\psi\rangle = \alpha|0\rangle + \beta|1\rangle. \tag{2.1}$$

Since the coefficients  $\alpha$  and  $\beta$  are complex numbers that satisfy  $|\alpha|^2 + |\beta|^2 = 1$ , the state can be rewritten as<sup>1</sup>

$$|\psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{i\varphi}\sin\frac{\theta}{2}|1\rangle$$

(2.2)

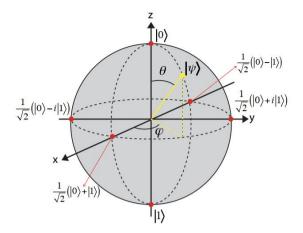

with  $\theta \in [0, \pi]$  and  $\varphi \in [0, 2\pi)$ . Hence, a single qubit can be visualized as a point on the surface of a sphere often called the Bloch sphere, as shown in Fig.2.1[1, 2].

The electrons are physically confined in 3 spatial dimensions in a quantum dot (see subsection 2.1.1). The energy levels for the spin-up and spin-down states are split due to the Zeeman effect. The energy difference is expressed as

$$E_z = g\mu_B B, (2.3)$$

<sup>&</sup>lt;sup>1</sup>A global phase  $e^{i\gamma}$  is ignored as it has no physical significance.

Figure 2.1: Bloch sphere representation of a single qubit state [3]. The north pole and the south pole are defined as the basis states  $|0\rangle$  and  $|1\rangle$ . A superposition state can be plotted in the angular coordinates of a point. A single qubit operation is equivalent to one or more rotations on the Bloch sphere.

where g is the electron g-factor, B the applied static magnetic field and  $\mu_B$  the Bohr magneton. For electrons in silicon, when B is 1 T, the energy splitting is about 100  $\mu eV$ . Similar to AND, OR and NOT gates for a classical computer, quantum circuits also require logical gates as building blocks. For spin qubits, applying logical gates means physically changing the direction of the electron spins using a rotating magnetic field or fast voltage pulses. A single-qubit gate operation can be viewed as a rotation of the state vector around the Bloch sphere. Full control of a qubit requires the ability to rotate about two axes of the Bloch sphere. Two-qubit gates are able to create entanglement between qubits. An example of a two-qubit gate is a rotation of one spin dependent on the state of the other [4, 5].

Measurement of a quantum state collapses the state to either  $|0\rangle$  or  $|1\rangle$  with probability  $|\alpha|^2$  or  $|\beta|^2$  (from equation 2.1), respectively. We describe readout schemes in subsection 2.1.3.

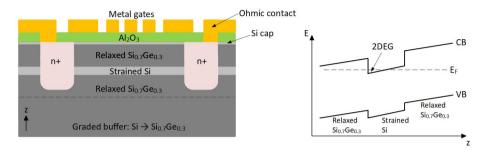

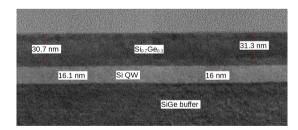

## 2.1.1. GATE-DEFINED QUANTUM DOTS FORMED IN SI/SIGE SUBSTRATE

Quantum dots confine electrons in all three dimensions. First, a heterostructure is used to restrict the movement of electrons to a two-dimensional plane. As shown in the left panel of Fig.2.2, a strained silicon layer is sandwiched between two relaxed  $Si_{0.7}Ge_{0.3}$  layers. The structure is grown epitaxially so silicon atoms in the quantum well will align with the relaxed  $Si_{0.7}Ge_{0.3}$  lattice and a tensile strain is formed. Such strain alters the bandgap of silicon. Thus, the band diagram of the heterostructure is aligned to make the conduction band minimum (CB) of the strained-silicon layer lower than that of  $Si_{0.7}Ge_{0.3}$  on both sides. When the dielectric layer ( $Al_2O_3$ ) and metal gates are deposited on top and voltages are applied to the gates, the Fermi level ( $E_F$ ) could cross CB, as shown in the right panel of Fig.2.2. Electrons trapped in this triangular potential well form the 2-dimensional electron gas (2DEG) at the interface between the strained-Si layer and

the top relaxed  $Si_{0.7}Ge_{0.3}$  layer. In terms of energy levels in this quantum well, there are in general six-fold degenerate states (with equivalent energy level) at conduction band minimum for relaxed crystalline silicon. Due to the strain in the lattice, these six states split into four states that go up in energy and two states that go down in energy. The lower two states are also split in energy and we call this splitting the valley splitting. [6, 7].

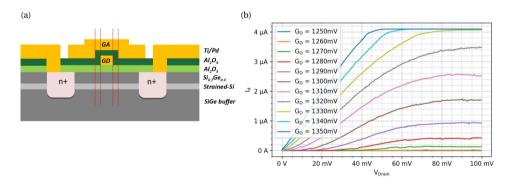

Figure 2.2: Left: cross-section of a Si/SiGe based quantum dot. A step-graded SiGe $_x$  buffer layer is grown until reaching a stably 30% germanium composition. A thin silicon layer (around 10 nm) is strained between two relaxed Si $_{0.7}$ Ge $_{0.3}$  layers. The upper layers are composed of Si/Si $_{0.2}$  cap, dielectric and metal in sequence. The reservoirs are defined by phosphorus implantation. Right: band diagram of the substrate heterostructure. A corner of the conduction band minimum falls below the Fermi level, allowing electrons to fill the energy states inside. 2DEG is then formed at the interface between the top Si $_{0.7}$ Ge $_{0.3}$  layer and the strained-silicon layer[6].

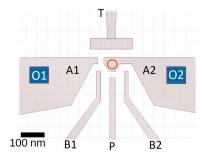

A 1-2nm thick silicon cap layer deposited on top of the heterostructure is used to prevent oxidation of SiGe. Metal gates isolated by dielectric layers ( $Al_2O_3$ ) define the potential landscape in the quantum well. Thus, few electrons are confined in a nanoscale island, and the remaining two-dimensional freedom in the 2DEG is removed. Fig.2.3 shows the top view of a single quantum dot, the accumulation gates Al and A2 induce electrons from reservoirs (phosphorus implantation areas) to the Si quantum well. The plunger gate P controls the electrochemical potential of a quantum dot and the barrier gates Bl and B2 control the tunnel barrier to the next dot. When a bias voltage is applied between the reservoirs on both sides of the quantum dot, a current flows through the quantum dot depending on the alignment of the quantum dot electrochemical potentials, as discussed in the next section[8].

Figure 2.3: Layout design of a single quantum dot. Electrons are confined in the region indicated by a red circle.

14 2. BACKGROUND

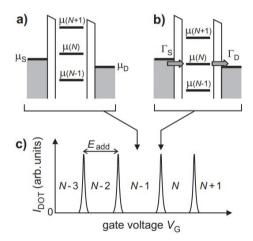

#### 2.1.2. COULOMB PEAKS AND COULOMB DIAMONDS

The number of electrons on a quantum dot is limited by the Coulomb blockade effect, which can be observed through Coulomb peaks or Coulomb diamonds in the measurement. We provide some explanation in this section.

The electrochemical potential of a quantum dot is defined as the difference in total energy of an N-electron dot and an (N-1)-electron dot, expressed as

$$\mu(N) = U(N) - U(N-1). \tag{2.4}$$

Due to the small size of the quantum dots, adding an electron to the dot results in a change in its electrochemical potential, the amount can be calculated as

$$E_{add} = \mu(N+1) - \mu(N) = E_c + \Delta E,$$

(2.5)

where  $E_c$  is the charging energy that equals to  $e^2/C$  (e the elementary charge and C the total capacitance of the dot),  $\Delta E$  is the energy spacing between two discrete orbital levels<sup>2</sup>. Since the conditions for electron tunnelling are critically related to the electrochemical potential on both sides of the barrier, the electron tunnelling from a reservoir to the dot can be blocked if the electrochemical potential of the dot after adding the next electron is higher than that of the reservoir. To remove this blockade, voltages are applied to the plunger gate to change the dot's electrochemical potential<sup>3</sup>.

Figure 2.4: The electrochemical potential of the dot is altered by the plunger gate voltage  $V_G$ . a) No energy level falls within the window set by the bias voltage at source and drain reservoirs  $\mu_S - \mu_D = -|e|(V_S - V_D)$ . b) One level falls within the bias window and one electron after another can pass through the dot. The current depends on the tunneling rate between the dot and the reservoir on the left  $\Gamma_S$  and on the right  $\Gamma_D$  as indicated with arrows. c) Schematic plot of the current flowing through the dot as a function of the plunger gate voltage, giving rise to Coulomb peaks. The distance between peaks reveals the addition energy[4].

<sup>&</sup>lt;sup>2</sup>A quantum dot can be viewed as an artificial atom with quantized orbital levels.  $\Delta E$  can be zero when two electrons are added to the same orbital[9].

<sup>&</sup>lt;sup>3</sup>The electrochemical potential depends linearly on the gate voltage.

As illustrated in Fig. 2.4, the electrochemical potentials corresponding to different numbers of electrons on the dot  $(\mu(N-1), \mu(N), \mu(N+1)...)$  form a ladder. Applying voltages on the plunger gate  $(V_G)$  moves the ladder up or down while keeping the space between the levels constant. A bias voltage is applied to the source and drain reservoirs, opening an energy window of  $\mu_S - \mu_D$ . When no electrochemical potential level in the dots falls within the bias window (Fig. 2.4(a)), no current flows through the dot. When the energy level satisfies  $\mu_S \geq \mu(N) \geq \mu_D$  (Fig. 2.4(b)), an electron can tunnel from the source to the dot and then to the drain. Then another electron can tunnel from the source to the dot and so on. This cycle forms a current. The current value depends on the tunnelling rate  $\Gamma_S$  and  $\Gamma_D$ . Therefore, sweeping the gate voltage while measuring the current flowing through the dot results in a plot showing single-electron tunnelling current (Fig. 2.4(c)), known as Coulomb peaks. The distance between the peaks is constant as long as the dot size remains the same and the orbital level spacing can be neglected (constant-interaction model). The peaks broaden with increased temperature [4, 10].

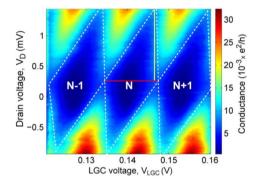

Figure 2.5: Coulomb diamond plot of an SET at 30mK. A 2D scan of the drain voltage  $V_D$  (source voltage  $V_S$ =0) and the gate voltage  $V_{LGC}$ , with colours representing the conductance. Diamond-shaped areas corresponding to the zero-conductivity can be observed [11].

So far we are assuming that the source-drain bias voltage is low such that at most one level falls in the bias window (low-bias regime). When increasing the bias voltage, multiple electrochemical potential levels could fall within the energy window. In this case, multiple electrons can pass through the dot simultaneously, resulting in a higher current (high-bias regime). The Coulomb diamond plot is obtained by a 2-dimensional scan of the source-drain voltage and the plunger gate voltage, with current flowing through the dot (or the conductance) represented by colours. Fig. 2.5 shows an example of the Coulomb diamond plot of a single electron transistor (SET)<sup>4</sup>. In the diamond-shaped areas (in dark blue), the current is blocked and the number of electrons on the dot is constant. Outside the diamond area, currents are flowing through the dot, the amplitude of which is higher with higher bias voltages. With this plot we could further check the stability of the dot. From the Coulomd diamond size, we can extract the lever arm from the gate to the dot potential. The lever arm  $\alpha_G$  converts the change of the plunger gate voltage  $\Delta V_p$  to the change of the electrochemical potential of the dot  $\Delta E$ , expressed

<sup>&</sup>lt;sup>4</sup>A single quantum dot can be viewed as a SET.

as  $\Delta E = -\alpha_G \Delta V_p$ . From the Coulomb diamond plot,  $\alpha_G$  can be extracted as the ratio between the bias voltage and the gate voltage (represented by line segments in yellow and red, respectively, in Fig. 2.5). This type of diamond plot provides more information when a static magnetic field is applied, there are additional lines to reveal the spin up and down states [4].

## **2.1.3.** MEASUREMENT TECHNIQUES

#### Charge sensing

As just mentioned, the number of electrons on a quantum dot can be counted according to the measurement of Coulomb peaks or diamonds. However, when electrons are depleted to the last few, the tunnelling rate could be very low, so it would be difficult to measure the tunnelling current directly. (With the tunnelling rate of 100 kHz, the tunnelling current is about 10 fA.) A widely used way to monitor the electron numbers on a dot is placing a sensing dot or quantum point contact (QPC) close to the quantum dot. The sensing dot is capacitively coupled to the quantum dot area. Adding electrons to the quantum dot leads to a change of the current flowing through the sensing dot or QPC. One advantage of this so-called charge sensing technique is that the quantum dots states are not affected by the measurement [4].

#### Spin readout

When applying a static magnetic field, the energy state of a single electron in the dot is split into spin-up and spin-down states. The spin-down state is regarded as ground state for silicon based qubits. Since it is hard to measure the tiny magnetic moment of a spin directly, the spin state is measured indirectly by making the charge state change depending on the spin state. The method that converts the spin states to charge states, which can be detected with a sensing dot nearby is called spin-to-charge conversion[12, 13].

The spin readout experiment consists of 3 stages as shown in Fig.2.6(a). The plunger gate voltage  $V_p$  is tuned to empty the dot, inject an electron and read out its spin state. Firstly, the dot is emptied by making the dot's energy levels corresponding to both spin up and spin down states higher than the Fermi energy  $E_F$  of the reservoir, as depicted in the first column of Fig.2.6(c). (Since the figure describes electron spin states based on GaAs dots, here spin-up is regarded as a ground state and spin-down is regarded as an excited state.) Then the plunger gate voltage is increased to pull both levels below  $E_F$ . This allows an electron to tunnel from the reservoir to the dot with a random spin state (second column of Fig.2.6(c)). After  $t_{wait}$ , the plunger gate voltage is reduced to make  $E_F$  lies between the spin up and spin down levels (third column of Fig.2.6(c)). If the electron is spin up, it remains in the dot. No change in the current flowing through the sensing dot ( $\Delta I_{QPC}$ ) occurs. If the electron is spin down, it tunnels out from the dot and another electron with up state tunnels into the dot afterwards. This results in current changes on the sensing dot, as shown in the red circle of Fig.2.6(b). Thus, the electron spin states can be determined according to the features in the sensing dot current[12].

$<sup>^{5}</sup>t_{wait}$  needs to be longer than the electron tunnelling time. Meanwhile, when increasing  $t_{wait}$ , the possibility of spin down in readout results decreases due to the spin relaxation.

Figure 2.6: Elzerman spin-to-charge readout technique. a) Voltage pulses are applied to the plunger gate  $(V_p)$  to inject a single electron onto the quantum dot and measure its spin state. b)Changes of the current flowing through the sensing dot, which is affected by 2 factors: the amplitude of  $V_p$  and electron tunnelling on and off the dot. c) Energy diagrams for different stages of the experiment, details are described in the main text[12].)

## 2.2. SWITCHED-CAPACITOR CIRCUIT AND APPLICATION

Next, we move on to the electronics aspect to discuss the switched-capacitor circuit. It consists of a transistor as a switch and a capacitor as a local battery. The circuit schematic is shown in the left half of Fig.1.3. It is also known as a simple sample-and-hold circuit in analog electronics. To switch on an n-type transistor, the voltage on the transistor gate  $V_g$  needs to satisfy  $V_g^{ON} - V_{th} > V_{in}^{MAX}$ , where  $V_{th}$  and  $V_{in}^{MAX}$  are the transistor threshold voltage and the maximum input voltage, respectively. Then the output voltage (the voltage on the plunger gate  $V_p$  in Fig.1.3) follows  $V_{in}$ , namely it samples the signal. When switching off the transistor by setting  $V_g^{OFF} - V_{th} < V_{in}^{MIN}$  ( $V_{in}^{MIN}$  being the minimum input voltage)<sup>6</sup>,  $V_p$  remains constant. Thus, the input voltage is held locally on the capacitor. A sample-and-hold circuit is often used to maintain the input of an ADC during conversion. For the ADC to produce accurate results, the holding voltages need to be precise and stable. Therefore, extra structures (e.g. complementary switches, differential inputs, etc) are sometimes implemented to improve its performance[14].

This structure of a transistor and a capacitor in series is also commonly applied as a memory cell. The structure is repeated and arranged in a rectangular array to form a DRAM matrix. The transistor gates share the word-lines and the drain of the transistors share the bit-lines. Each cell encodes one data bit of information by the charged/discharged

<sup>&</sup>lt;sup>6</sup>The voltage region between  $V_g^{ON}$  and  $V_g^{OFF}$  is much larger than  $V_{in}^{MAX} - V_{in}^{MIN}$  to avoid false switches in the subthreshold region.

state of the storage capacitor. The most significant advantage of a DRAM is that the memory cell structure is simple, which also results in high cell densities. However, charges on the capacitor always slowly leak off, so memory refreshing is required to periodically rewrite the data in the capacitors[15].

For the application in this study, we take advantage of the structure simplicity of switched-capacitor circuits. However, since the maintained voltages are used for electron confinement, requirements on the voltage accuracy here are higher than that for DRAMs, ranges from  $1\mu V$  to 1 mV[16].

#### 2.2.1. Precision considerations

Here we review considerations on the accuracy of the floating gate voltage in the literature, which is the basis for our choices of device dimensions. We will first discuss two mechanisms that lead to a random error in the floating node voltage, and next review mechanisms that in principle produce a systematic error.

Fundamentally, the voltage resolution  $\Delta V$  of a floating node is limited by the electron charge, e, as

$$\Delta V = e/C_H \,, \tag{2.6}$$

where  $C_H$  is the total capacitance of the floating node to ground. It is dominated by the holding capacitor in our case. In order to keep  $\Delta V$  below 1  $\mu$ V,  $C_H$  should be larger than 160 fF.

Next, thermal noise is present due to the transistor channel resistance when the transistor is switched on. The random thermal noise voltage is maintained on the holding capacitor after switching off the transistor. The root-mean-square (RMS) noise voltage on the capacitor is calculated as [17]

$$V_n^{rms} = \sqrt{k_B T/C_H} \,. \tag{2.7}$$

For instance, to obtain a noise level below 1  $\mu$ V at a temperature of 10 mK, the holding capacitance must exceed 138 fF.

Note that the final noise level is independent of the transistor channel resistance. We summarize the derivation of Eq. 2.7 below for a better understanding.

When an SC circuit works in sampling mode, the transistor can be modelled as a noise source  $V_{ni}$  in series with an ideal resistor R (the resistance equal to the on-resistance of the transistor). The noise spectral density of the resistor is

$$V_{ni}^2 = 4kTR, (2.8)$$

expressed in units of  $V^2/Hz$ . Here k is the Boltzman constant and T the temperature in kelvin. Since the transfer function of an RC circuit from input to output is

$$H(j\omega) = \frac{1}{1 + j\omega RC},\tag{2.9}$$

with  $\omega = 2\pi f$ , the noise spectral density at the output is

$$V_{no}^{2}(f) = \left| H(j2\pi f) \right|^{2} V_{ni}^{2}(f) = 4kTR \left| \frac{1}{1 + j2\pi fRC} \right|^{2}. \tag{2.10}$$

The total mean-squared voltage at the output is obtained by integrating the spectral density over the entire frequency spectrum,

$$V_{no(rms)}^{2} = \int_{0}^{\infty} V_{no}^{2}(f)df = 4kTR \int_{0}^{\infty} \frac{1}{1 + (j2\pi fRC)^{2}} df.$$

(2.11)

Since

$$\int_{y=0}^{\infty} \frac{1}{1+y^2} dy = (tan^{-1}y)\Big|_{y=0}^{\infty} = \frac{\pi}{2},$$

(2.12)

we have

$$V_{no(rms)}^{2} = \frac{4kTR}{2\pi RC} \int_{0}^{\infty} \frac{1}{1+y^{2}} dy = \frac{kT}{C}.$$

(2.13)

In short, we see that the thermal noise spectral density at the input is proportional to R, while it is filtered by an RC low-pass circuit with the bandwidth inversely proportional to R. This results in kT/C in the end [18].

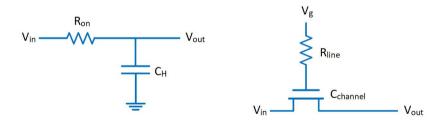

A first systematic offset in the floating node voltage is caused by channel charge injection. This effect refers to the charges that get redistributed to the drain and source upon switching a transistor off[14, 18]. As indicated in the left panel of Fig.2.7 , when  $FET_1$  is switched off, charges in the channel of  $FET_1$  are injected into the floating node and cause an error  $\Delta V_c$  in the stored voltage. Under the assumption that charges split equally to the source and drain, this error can be expressed as

$$\Delta V_c = \frac{C_{channel}(V_g^{ON} - V_{in} - V_{th})}{2C_H} , \qquad (2.14)$$

with  $C_{channel}$  the capacitance between the transistor gate and the channel,  $V_g^{ON}$  the "on" voltage on the gate of  $FET_1$ . Assuming  $V_g^{ON}$  is set 0.1 V higher than  $V_{in} + V_{th}$ , the holding capacitance needs to be 50 times larger than the transistor channel capacitance to make  $\Delta V_c$  less than 1 mV. In practice, the splitting fraction is also related to the switching speed, impedance at both sides and so on[19, 20].

Figure 2.7: Systematic voltage offsets due to channel charge injection (left panel) and gate-source parasitic capacitance (right panel).

Another factor that introduces systematic offsets in the maintained voltage is the parasitic capacitance from the transistor gate to the floating node (see the right panel of Fig.

2.7). In series with the holding capacitance, it shifts the voltage on the floating node by an amount that depends on the voltage on the gate of  $FET_1$ , given by [14, 18]

$$\Delta V_p = \Delta V_g \frac{C_{gs}}{C_{gs} + C_H}, \qquad (2.15)$$

where  $\Delta V_g$  is the switching range used to turn the transistor on and off and equals  $V_g^{ON} - V_g^{OFF}$ . Assuming  $\Delta V_g$  is 1 V, to make  $\Delta V_p$  less than 1 mV, the ratio of  $C_H$  to  $C_{gs}$  should be larger than 1000.

Importantly, different from the random variations in the floating gate voltage, the systematic shifts can be accounted for in the calibration phase, hence they do not impose strict requirements on  $C_H$ .

Table 2.1 summarizes the specifications for providing bias voltages to the floating node. As we shall see, in general a larger holding capacitance reduces these errors, however, it also increases the footprint and power dissipation, both of which eventually can limit scalability as well [21].

|                                     | $\Delta V < 1\mu V$               | $\Delta V < 1mV$      |

|-------------------------------------|-----------------------------------|-----------------------|

| Single charge limit (Eq. 2.6)       | $C_H > 160 fF$                    | $C_H > 160 aF$        |

| Thermal noise (Eq. 2.7)             | $C_H > 138 fF$                    | $C_H > 138zF$         |

| Channel charge injection (Eq. 2.14) | $C_H > 5 \times 10^4 C_{channel}$ | $C_H > 50C_{channel}$ |

| Parasitic capacitor (Eq. 2.15)      | $C_H > 10^6 C_{gs}$               | $C_H > 10^3 C_{gs}$   |

Table 2.1: Specifications of the transistor and the capacitor in an SC circuit for reaching  $1\mu$  V or 1 mV resolution of maintained voltages.

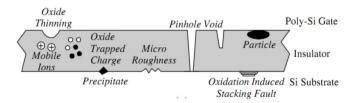

In the end, we briefly introduce the imperfection of holding capacitors. There are always defects in the dielectric materials used for capacitors, which form low-resistance conduction paths and slowly discharge the capacitor. Fig. 2.8 describes some sources of defects in a MOS capacitor. The conduction process in insulators includes tunnelling, thermionic emission, ionic conduction and so on. Each of them may dominate the leakage current depending on the insulator qualities, temperature and voltage conditions. In many cases, these mechanisms are not independent of each other [22, 23].

Figure 2.8: Schematic of defects in an insulator[23].

#### 2.2.2. POWER CONSUMPTION

To charge a capacitor *C* through a resistor *R*, we denote a general calculation of power consumption before adapting the results in our specific circuit.

When charging the capacitor, the current can be expressed as

$$i(t) = Ie^{(-t/\tau)},$$

(2.16)

where the initial current I = V/R, V is the final capacitor voltage. The time constant  $\tau = RC$ .

The power dissipated in the resistor as a function of time is

$$P(t) = i(t)^{2} R = I^{2} R e^{(-2t/\tau)}$$

(2.17)

Integrate the power over time to calculate the total energy as

$$E = \int_0^\infty I^2 R e^{(-2t/\tau)} dt = \frac{I^2 R \tau}{2} = \frac{1}{2} C V^2.$$

(2.18)

Note that during the charging phase, the energy dissipated in the resistor of an RC circuit is equal to the energy stored in the capacitor and independent of the resistance. The stored energy is converted to heat during the discharging phase.

In our case, consider charging the floating node with an RC module shown in the left panel of Fig. 2.9, and discharging the node through parasitic resistance on the leakage path, then the total generated heat can be expressed as

$$P_1 = C_H f_g (V_1 - V_2)^2 , (2.19)$$

where  $V_1$  and  $V_2$  are the high and low voltages on the holding capacitor during operation, and  $f_g$  is the switching frequency of the transistor. If we refresh the floating node to compensate for a 1 mV drop with a 1 Hz frequency, the power dissipation associated with repeatedly refreshing the stored voltage is  $10^{-18}$  W when the holding capacitor is 1 pF. This is orders of magnitude smaller than the heat dissipated during switching in

Figure 2.9: Left: when refreshing the holding capacitor, currents flow through the on-resistance of the transistor to charge/discharge the holding capacitor. Right: when switching the transistor, currents flow through the signal line resistance to charge/discharge the transistor channel capacitor.

the resistance in the line between a pulse generator and the gate of the transistor (right panel of Fig.2.9), which can be expressed as

$$P_2 = C_{channel} f_g (V_g^{ON} - V_g^{OFF})^2. (2.20)$$

For a transistor with a 0.01 pF channel capacitance and 1 V switching range, the power dissipated on the signal line to its gate is  $10^{-12}$  W. Even if we assume that this power is entirely dissipated on-chip, it would still in principle allow  $10^8$  floating gate voltages to be maintained assuming  $100~\mu\mathrm{W}$  available cooling power at the chosen operating temperature.

Making the transistors smaller reduces  $C_{channel}$  and  $C_{gs}$ , which reduces switching power dissipation as well as the systematic shifts in the floating gate voltage. However, secondary effects appear when the device is scaled down. For instance, when the channel width is lower than 1  $\mu$ m, the threshold voltage  $V_{th}$  increases due to the narrow-channel effect [24, 25]. Then a higher gate voltage is required to turn on the transistor which is more likely to cause hysteresis and breakdown.

## REFERENCES

- [1] D. Loss and D. P. DiVincenzo, *Quantum computation with quantum dots*, Phys. Rev. A **57**, 120 (1998).

- [2] M. A. Nielsen and I. L. Chuang, *Quantum Computation and Quantum Information:* 10th Anniversary Edition (Cambridge University Press, 2010).

- [3] L. Lao, QUANTUM COMPUTING IN PRACTICE: FAULT-TOLERANT PROTOCOLS AND CIRCUIT-MAPPING TECHNIQUES, Ph.D. thesis, Delft University of Technology (2019).

- [4] R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, *Spins in few-electron quantum dots*, Rev. Mod. Phys. **79**, 1217 (2007).

- [5] F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. L. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, *Silicon quantum electronics*, Rev. Mod. Phys. 85, 961 (2013).

- [6] M. Eriksson, S. Coppersmith, and M. Lagally, Semiconductor quantum dot qubits, MRS Bulletin 38, 794–801 (2013).

- [7] M. Friesen, S. Chutia, C. Tahan, and S. N. Coppersmith, *Valley splitting theory of SiGe/Si/SiGe quantum wells*, Phys. Rev. B **75**, 115318 (2007).

- [8] P. SCARLINO, SPIN AND VALLEY PHYSICS IN A SI/SIGE QUANTUM DOT, Ph.D. thesis, Delft University of Technology (2016).

- [9] S. Tarucha, D. G. Austing, T. Honda, R. J. van der Hage, and L. P. Kouwenhoven, *Shell filling and spin effects in a few electron quantum dot*, Phys. Rev. Lett. **77**, 3613 (1996).

- [10] L. P. Kouwenhoven, C. M. Marcus, P. L. McEuen, S. Tarucha, R. M. Westervelt, and N. S. Wingreen, *Electron transport in quantum dots*, in *Mesoscopic Electron Transport*, edited by L. L. Sohn, L. P. Kouwenhoven, and G. Schön (Springer Netherlands, Dordrecht, 1997) pp. 105–214.

- [11] P. J. Koppinen, M. D. Stewart, and N. M. Zimmerman, *Fabrication and electrical characterization of fully cmos-compatible si single-electron devices*, IEEE Transactions on Electron Devices **60**, 78 (2013).

- [12] J. M. Elzerman, R. Hanson, L. H. Willems van Beveren, B. Witkamp, L. M. K. Vandersypen, and L. P. Kouwenhoven, *Single-shot read-out of an individual electron spin in a quantum dot*, Nature **430**, 431 (2004).

- [13] K. Ono, D. G. Austing, Y. Tokura, and S. Tarucha, *Current rectification by pauli exclusion in a weakly coupled double quantum dot system*, Science **297**, 1313 (2002).

- [14] B. Razavi, *Design of Analog CMOS Integrated Circuits* (McGraw-Hill Education, 2001).

- [15] B. Keeth, R. J. Baker, B. Johnson, and F. Lin, *DRAM Circuit Design. Fundamental and High-Speed Topics* (Wiley-IEEE Press, 2007).

- [16] L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, and M. Veldhorst, *Interfacing spin qubits in quantum dots and donors hot, dense, and coherent*, npj Quantum Information 3, 34 (2017).

- [17] R. W. Brodersen, P. R. Gray, and D. A. Hodges, *Mos switched-capacitor filters*, Proceedings of the IEEE **67**, 61 (1979).

- [18] D. A. Johns and K. Martin, *Analog Integrated Circuit Design* (John Wiley and Sons, 1997).

- [19] G. Wegmann, E. Vittoz, and F. Rahali, *Charge injection in analog mos switches*, IEEE Journal of Solid-State Circuits **22**, 1091 (1987).

- [20] B. Sheu and C. Hu, *Switch-induced error voltage on a switched capacitor*, IEEE Journal of Solid-State Circuits **19**, 519 (1984).

- [21] D. P. Franke, J. S. Clarke, L. M. K. Vandersypen, and M. Veldhorst, *Rent's rule and extensibility in quantum computing,* Microprocessors and Microsystems **67**, 1 (2019).

- [22] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices (Wiley, 2006).

- [23] D. K. Schroder and L. G. Rubin, *Semiconductor material and device characterization* (American institute of physics, 1991).

- [24] D. A. Neamen, *Semiconductor Physics and Devices: Basic Principles* (McGraw-Hill, 4th edition, 2012).

- [25] T. M. Lu, J. K. Gamble, R. P. Muller, E. Nielsen, D. Bethke, G. A. Ten Eyck, T. Pluym, J. R. Wendt, J. Dominguez, M. P. Lilly, M. S. Carroll, and M. C. Wanke, *Fabrication of quantum dots in undoped Si/Si*<sub>0.8</sub>*Ge*<sub>0.2</sub> *heterostructures using a single metal-gate layer*, Applied Physics Letters **109**, 093102 (2016).

# PROCESS DEVELOPMENT AND EXPERIMENTAL SETUP

On-chip integration of electronic circuits and quantum dots is currently not an industrystandard process. Therefore, prototypes are made in research labs for the proof of concept. Since quantum dots are more fragile and demanding compared to micrometer scale electronic circuits, the general rule of integration is to integrate the electronic circuits where possible without affecting the fabrication flow of quantum dots.

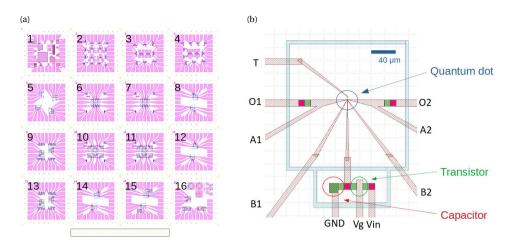

## 3.1. FABRICATION PROCESS

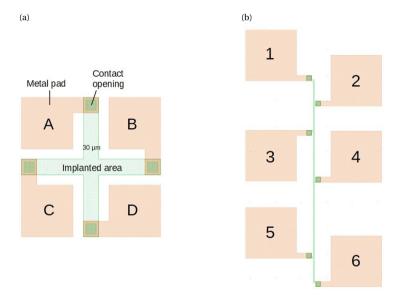

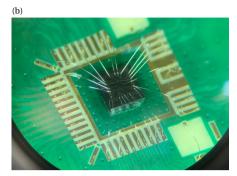

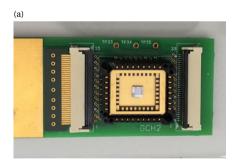

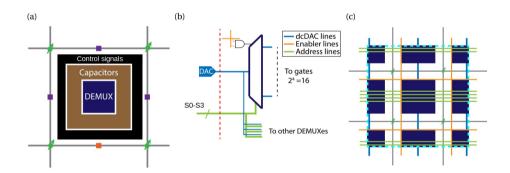

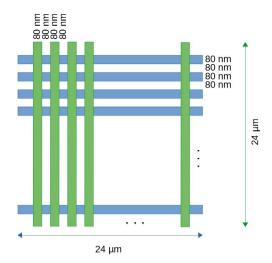

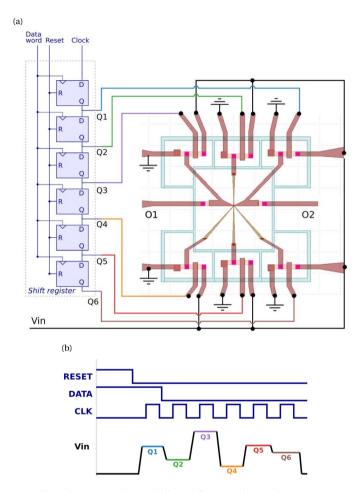

Before describing fabrication steps in detail, we will first give an overview of the device layout. Fig.3.1(a) shows the whole design of a 1 cm by 1 cm chip consisting of 16 cells, among which, relevant to this study are Cell 2: individual transistors; Cell 5: individual single quantum dots; Cell 12 and 15: quantum dots with floating gates; and Cell 16: test structures. Fig.3.1(b) zooms in part of Cell 12 and shows the pattern of a floating gate device composed of a single quantum dot and a switched-capacitor circuit. Here the fine gates of the quantum dot are in tens of nanometer scale and the transistor and capacitor are a few micrometers. There are generally two ways to process them: define all patterns on a chip using ebeam-lithography, or first define large patterns (micrometer scale) on a wafer using photo-lithography, then dice the wafer and continue making fine patterns (nanometer scale) using ebeam lithography. The former approach saves substrate in the early process development period and avoids transferring samples between labs in practice<sup>1</sup>. The latter method accelerates the process and improves the reproducibility once the large scale fabrication (pre-fab) is a success. Information on the full ebeam-lithography option is provided in appendix A. We will describe the combined-lithography option step by step in section 3.1.1 and appendix B. We process optical lithography at Else Kooi Lab (EKL), and ebeam-lithography at Van Leeuwenhoek Laboratory (VLL).

<sup>&</sup>lt;sup>1</sup>Early samples with gold gates are forbidden to process in the Else Kooi Lab.

Figure 3.1: (a) Device layout with 16 cells on a 1 cm by 1 cm chip. Capacitors, transistors, quantum dots, floating gate devices and test structures are fabricated through the same process. (b) The pattern of a quantum dot with floating plunger gate. The quantum dot is in tens of nanometer scale and the switched-capacitor circuit in the micrometer scale.

The cross section of a quantum dot with a floating gate is shown in Fig. 3.2. We use a single patterned metal layer to define the potential landscape that confines electrons in the quantum dot. For the capacitor, the top plate is formed by a metal gate and the bottom plate by a heavily implanted region in the semiconductor, with a dielectric separating the plates. The transistor is a field-effect transistor with the buried quantum well acting as the channel at cryogenic temperature.

Figure 3.2: Schematic of the cross section of a single floating gate device (not to scale)

# **3.1.1.** DEVICE FABRICATION OVERVIEW

### **Substrate**

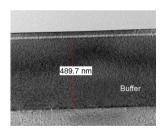

The Si/SiGe heterostructure is grown by reduced-pressure chemical vapor deposition on a 4-inch diameter crystalline Si wafer in EKL. From bottom to top, it contains a  $Si_{1-x}Ge_x$  buffer layer with 0% to 30% germanium concentration, a 10 nm strained-Si layer, a 30 nm  $Si_{0.7}Ge_{0.3}$  layer and a 1-2 nm Si/SiO<sub>2</sub> cap. The substrate used in this study is provided by Amir Sammak under supervision of Giordano Scappucci, both at QuTech [1].

### Optical markers and trench etching

The first pattern in the fabrication process is to define optical markers for mask alignment. In addition, to prevent electron accumulation in the quantum well from contact pads or drain of the transistor to the quantum dot gates, trenches (light blue pattern in Fig. 3.1(b)) used to isolate the quantum dot are also defined in this step, both require 100 nm deep etching into the Si/SiGe substrate.

The patterning process is executed on EVG 120 Coater-Developer and ASML PAS 5500/80 wafer stepper (with exposure wavelength of 365 nm) as follows. Same processes are applied to define implantation areas in the next step.

- · Spin coating:

- Pre-bake at 130  $^{\circ}$ C for 95 seconds with hexamethyldisilazane (HDMS) treatment to improve photoresist adhesion

- Spin coat 1.4 µm positive photoresist (SPR3012)

- Post-bake at 95 °C for 90 seconds

- Exposure:

- Optical lithography with energy density of 150 mJ/cm<sup>2</sup> to pattern markers

- Optical lithography with energy density of 140 mJ/cm<sup>2</sup> to pattern trenches

- Development:

- Post-exposure bake at 115 °C for 90 seconds

- Develop with MF322 for 57 seconds

- Hard bake at 100 °C for 90 seconds

The Si/SiGe substrate is dry-etched in Trikon Omega 201 plasma etcher. The sequence and conditions are listed in Table 3.1.

|                 | Gasses                          |          | Platen | ICP   | Platen      | Etch |

|-----------------|---------------------------------|----------|--------|-------|-------------|------|

| Step            | and flows                       | Pressure | RF     | RF    | temperature | time |

| 1. breakthrough | CF <sub>4</sub> /O <sub>2</sub> |          |        |       |             |      |

| native oxide    | 40/20 sccm                      | 5 mTorr  | 60 W   | 500 W | 20 ° C      | 10 s |

|                 | Cl <sub>2</sub> /HBr            |          |        |       |             |      |

| 2. Si/SiGe etch | 80/40 sccm                      | 60 mTorr | 10 W   | 500 W | 20 ° C      | 10 s |

Table 3.1: Si/SiGe etching condition