## Digital-Intensive Up-Converters for Wireless Communication

Shen, Y.

10.4233/uuid:e42721d6-6bf6-47b3-a683-3497f3d917ae

**Publication date**

**Document Version** Final published version

Citation (APA)

Shen, Y. (2021). Digital-Intensive Up-Converters for Wireless Communication. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:e42721d6-6bf6-47b3-a683-3497f3d917ae

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Digital-Intensive Up-Converters for Wireless Communication

Yiyu Shen

## Digital-Intensive Up-Converters for Wireless Communication

## Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. dr. ir. T. H. J. J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op

Tuesday 23 November 2021 at 12:30 o'clock

door

## Yiyu SHEN

Master of Science in Electrical Engineering, Katholieke Universiteit Leuven, Leuven, Belgium, and Master of Engineering in Integrated Circuit Engineering, Tsinghua University, Beijing, China.

geboren te Beijing, China.

This dissertation has been approved by the promotor:

Prof. dr. ing. L. C. N. de Vreede

Composition of the doctoral committee:

Rector Magnificus voorzitter

Prof. dr. ing. L. C. N. de Vreede Delft University of Technology, promotor Dr. S. M. Alavi Delft University of Technology, co-promotor

### Independent members:

Dr. ir. F. van Rijs Ampleon

Prof. dr. P. Wambacq Vrije Universiteit Brussel, Belgium Prof. dr. ir. P. G. M. Baltus Eindhoven University of Technology

Prof. dr. ir. B. Nauta University of Twente

Prof. dr. ir. W. A. Serdijn Delft University of Technology

Prof. dr. C. S. Vaucher Delft University of Technology, reserve member

Yiyu Shen,

Digital-Intensive Up-Converters for Wireless Communication,

Ph.D. Thesis Delft University of Technology.

Keywords: up-converters, digital-intensive transmitters (DTXs), digital power amplifiers (DPAs), polar transmitters, efficiency enhancement, phase modulators, direct-digital RF modulators (DDRMs), IQ-image, transmitter line-ups.

ISBN 978-94-6419-378-7

Copyright © 2021 by Yiyu Shen

Front & Back: cover by Pinpaishejibang, using a photo of EWI building in TU Delft taken by Yiyu Shen, a photo of TU Delft Library available at https://www.tudelft.nl/huisstijl/downloads, and a painting of Vincent Willem van Gogh (Dutch, Zundert 1853–1890 Auvers-sur-Oise) titled Wheat Field with Cypresses (1889), currently exhibited at Metropolitan Museum of Art in New York.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed in the Netherlands.

## Contents

| $\mathbf{C}$                          | onter        | ${f nts}$                                                                 | i  |  |  |

|---------------------------------------|--------------|---------------------------------------------------------------------------|----|--|--|

| 1                                     | Introduction |                                                                           |    |  |  |

|                                       | 1.1          | Introduction                                                              | 1  |  |  |

|                                       | 1.2          | CMOS TXs: Challenges and Opportunities                                    | 3  |  |  |

|                                       |              | 1.2.1 Challenges                                                          | 3  |  |  |

|                                       |              | 1.2.2 Opportunities                                                       | 4  |  |  |

|                                       | 1.3          | Thesis Objective                                                          | 5  |  |  |

|                                       | 1.4          | Thesis Outline                                                            | 6  |  |  |

|                                       | Refe         | erences                                                                   | 8  |  |  |

| 2                                     | Wir          | reless TX line-ups Review                                                 | 9  |  |  |

|                                       | 2.1          | Efficiency of Class-A, Class-B, and Class-AB PAs in Power Back-Off Region | 9  |  |  |

|                                       | 2.2          | Analog Cartesian Line-Ups                                                 | 12 |  |  |

|                                       | 2.3          | Polar TXs                                                                 | 13 |  |  |

|                                       |              | 2.3.1 Supply Modulators                                                   | 14 |  |  |

|                                       |              | 2.3.2 Envelope Tracking System                                            | 15 |  |  |

|                                       | 2.4          | Digital-Intensive TX Line-Ups                                             | 15 |  |  |

|                                       |              | 2.4.1 DPAs and Digital-Intensive Polar TXs                                | 16 |  |  |

|                                       |              | 2.4.2 DPA-Based Cartesian DTXs                                            | 18 |  |  |

|                                       |              | 2.4.3 Direct-Digital RF Modulator                                         | 19 |  |  |

| 2.5 Efficiency Enhancement Techniques |              | Efficiency Enhancement Techniques                                         | 20 |  |  |

|                                       |              | 2.5.1 Supply Switching: Class-G Operation                                 | 21 |  |  |

|                                       |              | 2.5.2 Doherty Power Amplifiers                                            | 22 |  |  |

|                                       |              | 2.5.3 Outphasing Power Amplifiers                                         | 23 |  |  |

|                                       | 2.6          | Conclusion                                                                | 24 |  |  |

|                                       | Refe         | erences                                                                   | 24 |  |  |

ii Contents

| <b>3</b>   | ly Integrated Digital-Intensive Polar Doherty Transmitter 2 |                                                                      |

|------------|-------------------------------------------------------------|----------------------------------------------------------------------|

|            | 3.1                                                         | Introduction                                                         |

|            | 3.2                                                         | Digital-Controlled Output Stage                                      |

|            |                                                             | 3.2.1 Doherty DPA                                                    |

|            |                                                             | 3.2.2 ACW-AM and ACW-PM Curves                                       |

|            | 3.3                                                         | System Architecture                                                  |

|            | 3.4                                                         | Implementation of the Output Stage                                   |

|            |                                                             | 3.4.1 Unit Cell Implementation                                       |

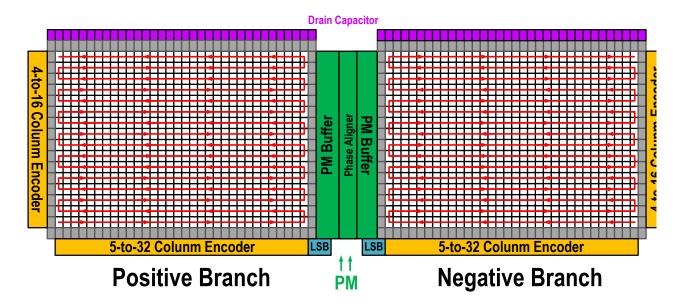

|            |                                                             | 3.4.2 DPA Bank Floorplan                                             |

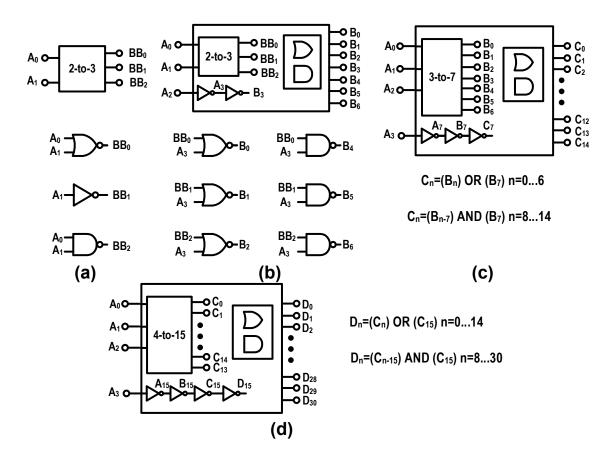

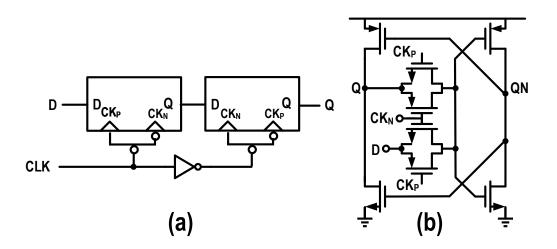

|            |                                                             | 3.4.3 Thermometer Encoder and DFF                                    |

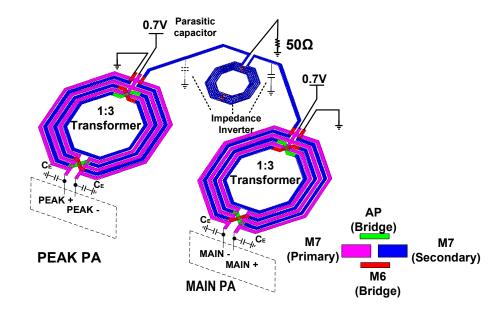

|            |                                                             | 3.4.4 Output Matching Network                                        |

|            | 3.5                                                         | Implementation of Digital Baseband                                   |

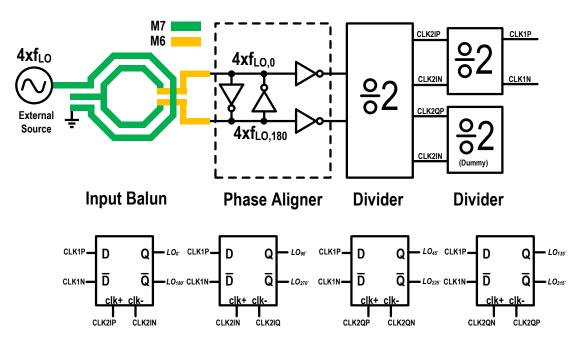

|            | 3.6                                                         | Implementation of LO Generation Circuits                             |

|            | 3.7                                                         | Digital Pre-Distortion                                               |

|            | 3.8                                                         | Measurement Results                                                  |

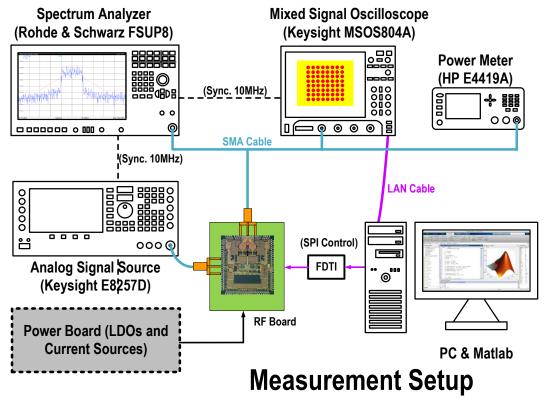

|            |                                                             | 3.8.1 Measurement Setup                                              |

|            |                                                             | 3.8.2 CW Measurement Results                                         |

|            |                                                             | 3.8.3 Single-Tone and Two-Tone Measurement Results                   |

|            |                                                             | 3.8.4 Broadband Measurement Results                                  |

|            |                                                             | 3.8.5 Performance Summary and Comparison with the State-of-the-Art 5 |

|            | 3.9                                                         | Conclusion                                                           |

|            | Refe                                                        | erences                                                              |

|            |                                                             |                                                                      |

| 4          |                                                             | DAC-Based Wideband Phase Modulator 5                                 |

|            | 4.1                                                         | Overview of Phase Modulators                                         |

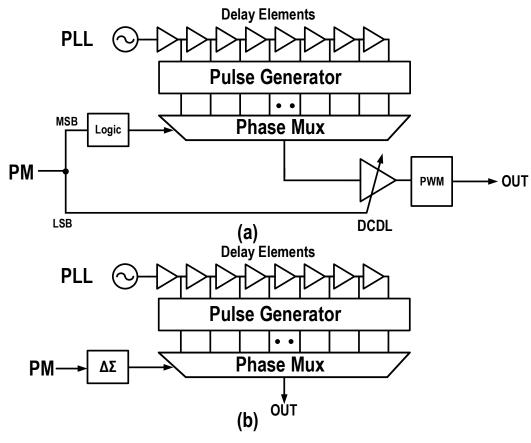

|            |                                                             | 4.1.1 PLL-Based Phase Modulators                                     |

|            |                                                             | 4.1.2 Delay Line-Based Phase Modulators 6                            |

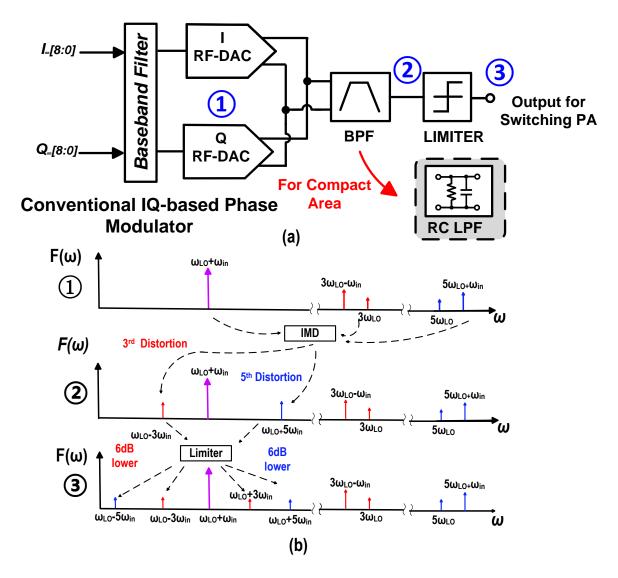

|            |                                                             | 4.1.3 Cartesian-Based Phase Modulators 6                             |

|            | 4.2                                                         | Towards Wideband Cartesian-Based Phase Modulator 6                   |

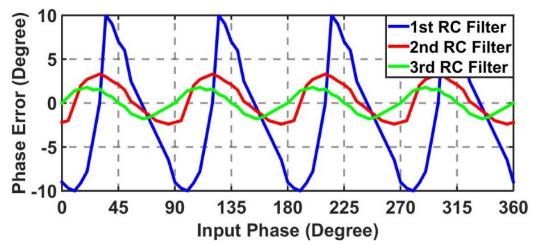

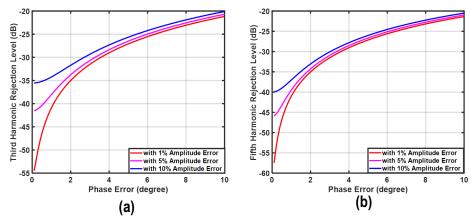

|            |                                                             | 4.2.1 Phase Error Source Analysis                                    |

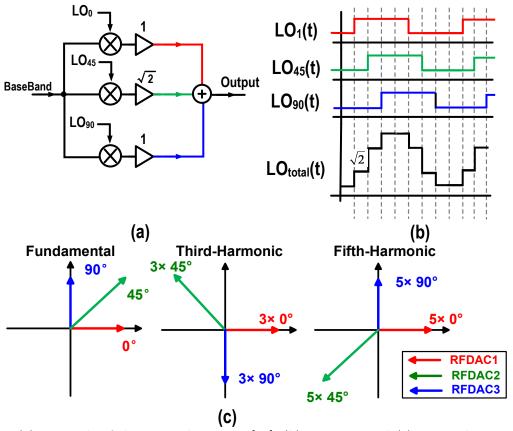

|            |                                                             | 4.2.2 Proposed System Architecture                                   |

|            |                                                             | Design of RFDAC                                                      |

|            |                                                             | 4.3.1 Design of unit cell                                            |

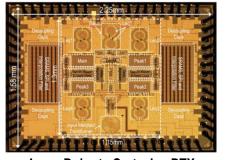

|            |                                                             | 4.3.2 Floorplan                                                      |

|            | 4.4                                                         | Implementation of Limiter                                            |

|            | 4.5                                                         | Measurement Results                                                  |

|            |                                                             | 4.5.1 Single-tone Test                                               |

|            |                                                             | 4.5.2 Modulated Signal Measurement                                   |

| 4.6        |                                                             | Conclusion                                                           |

| References |                                                             |                                                                      |

Contents

| 5 | $\mathbf{A} \mathbf{V}$    | Videband                                    | d IQ DDRM with an IQ-Mapping Technique                     | <b>7</b> 9 |  |  |  |  |

|---|----------------------------|---------------------------------------------|------------------------------------------------------------|------------|--|--|--|--|

|   | 5.1                        | Direct-D                                    | Digital RF Modulators                                      | 79         |  |  |  |  |

|   |                            | 5.1.1                                       | Concept of Direct-Digital RF Modulators                    | 79         |  |  |  |  |

|   |                            | 5.1.2 C                                     | Comparison between DDRM and DPA-Based Cartesian DTXs       | 81         |  |  |  |  |

|   |                            | 5.1.3 I                                     | Design Challenges of DDRMs                                 | 86         |  |  |  |  |

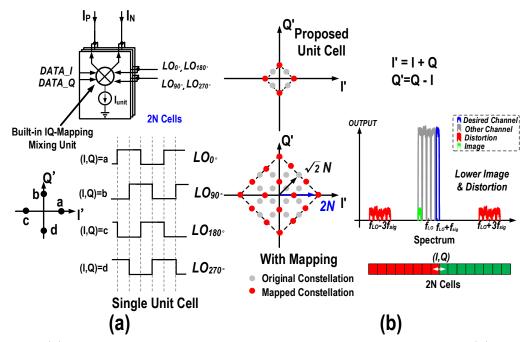

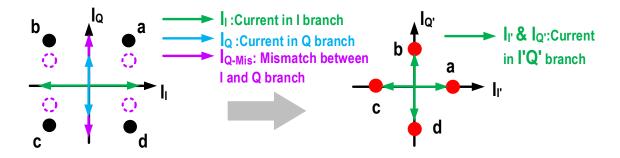

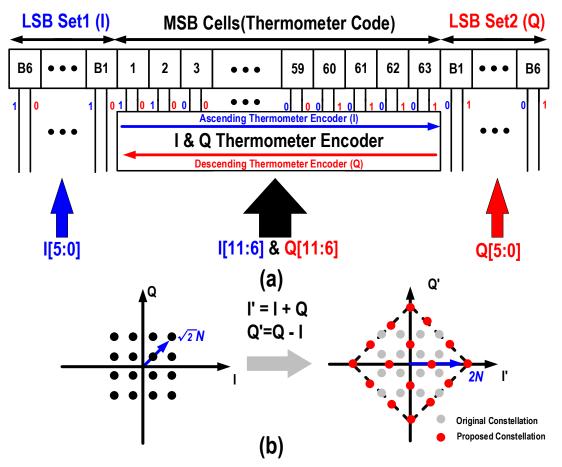

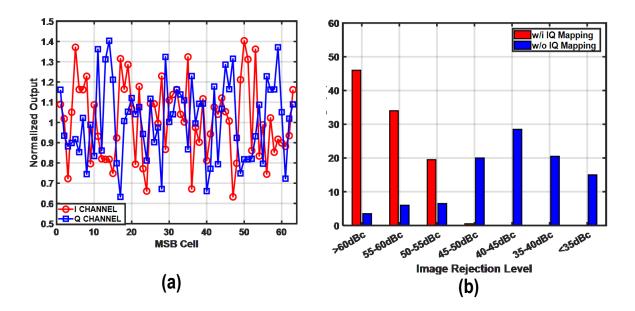

|   | 5.2                        | IQ-Mapp                                     | ping Technique                                             | 89         |  |  |  |  |

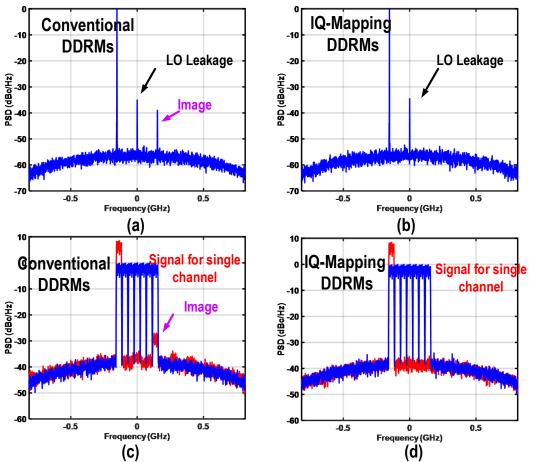

|   |                            | 5.2.1 In                                    | mproved Output Power and Efficiency                        | 90         |  |  |  |  |

|   |                            | 5.2.2 In                                    | ntrinsic Image Rejection                                   | 91         |  |  |  |  |

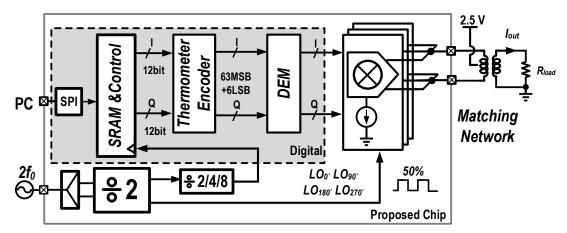

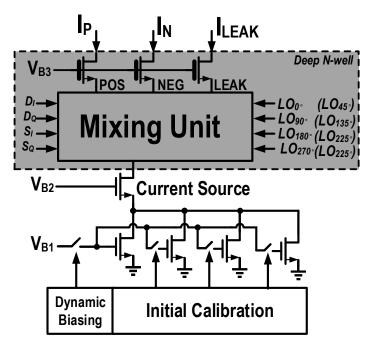

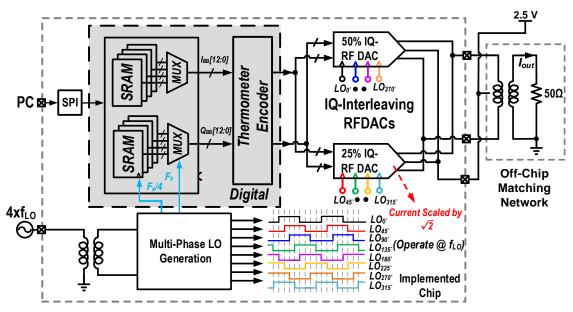

|   | 5.3                        | System A                                    | Architecture                                               | 93         |  |  |  |  |

|   | 5.4 Implementation of DDRM |                                             |                                                            |            |  |  |  |  |

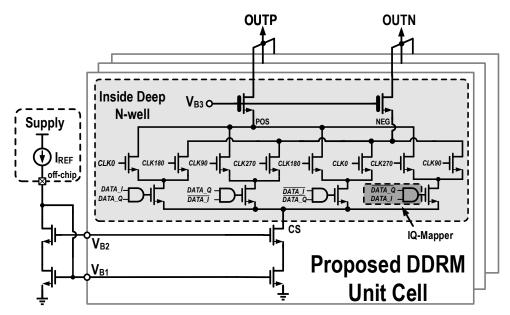

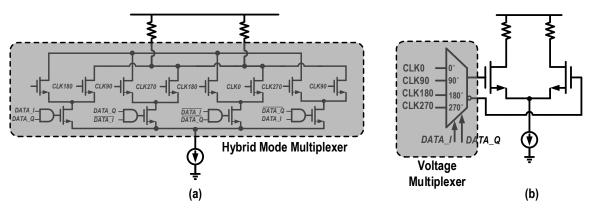

|   |                            | 5.4.1 S                                     | Schematic of DDRM                                          | 95         |  |  |  |  |

|   |                            | 5.4.2 E                                     | Binary Cells                                               | 97         |  |  |  |  |

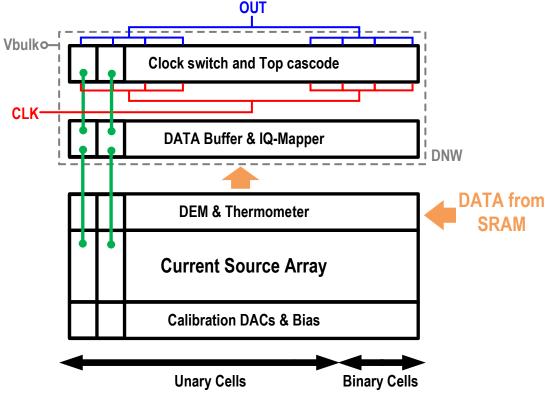

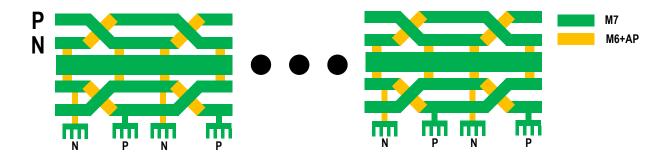

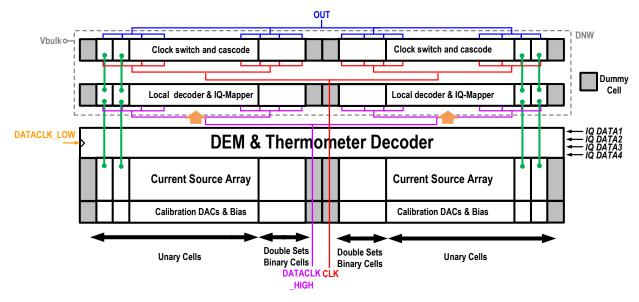

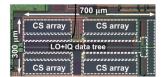

|   |                            | 5.4.3 F                                     | Floorplan of RFDAC                                         | 97         |  |  |  |  |

|   |                            | 5.4.4 L                                     | O Distribution Network                                     | 97         |  |  |  |  |

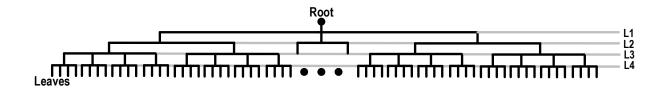

|   |                            | 5.4.5 C                                     | Output Tree Layout                                         | 99         |  |  |  |  |

|   |                            | 5.4.6 L                                     | Local Data Decoder                                         | 99         |  |  |  |  |

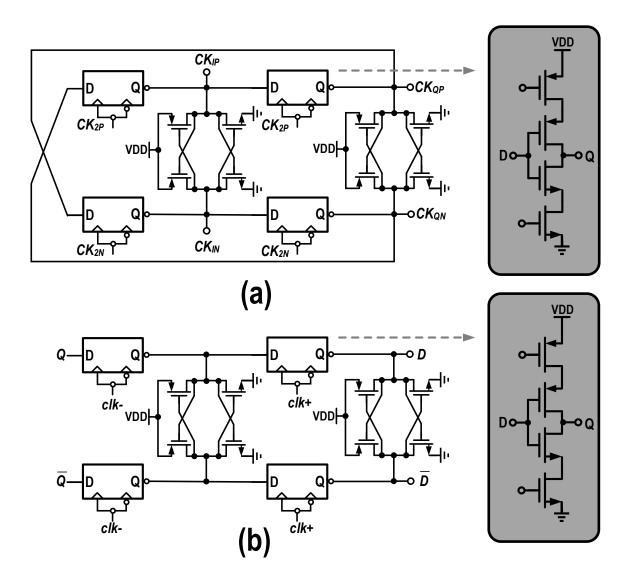

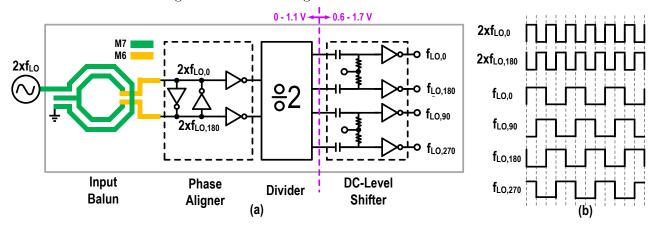

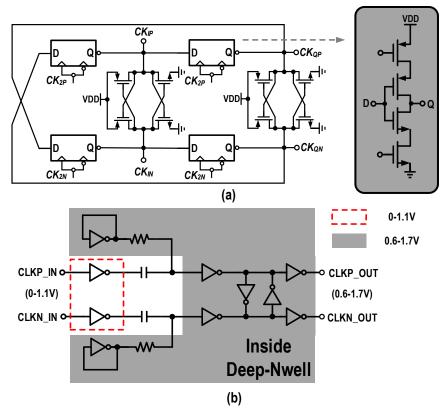

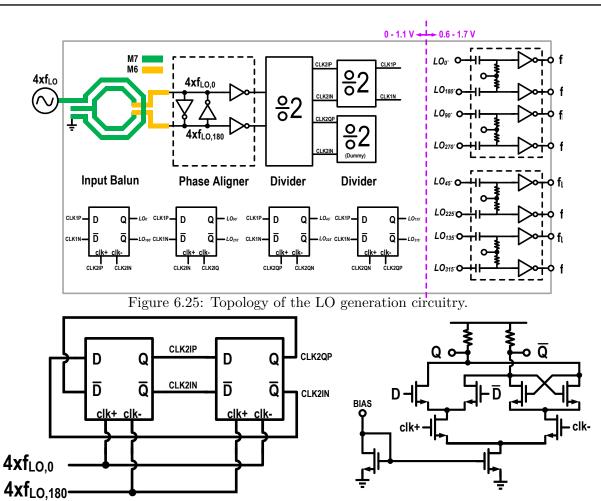

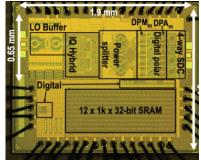

|   | 5.5                        | Impleme                                     | entation of LO Clock Generation                            | 99         |  |  |  |  |

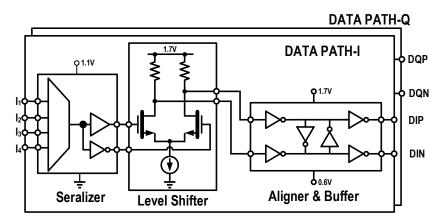

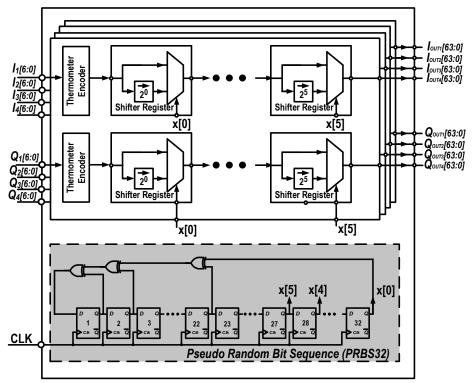

|   | 5.6                        | Impleme                                     | entation of Data Path                                      | 101        |  |  |  |  |

|   |                            | 5.6.1 In                                    | nterpolation Filters                                       | 102        |  |  |  |  |

|   |                            | 5.6.2 I                                     | DEM and Thermometer Encoder                                | 104        |  |  |  |  |

|   | 5.7                        | Measure                                     | ement Results                                              | 104        |  |  |  |  |

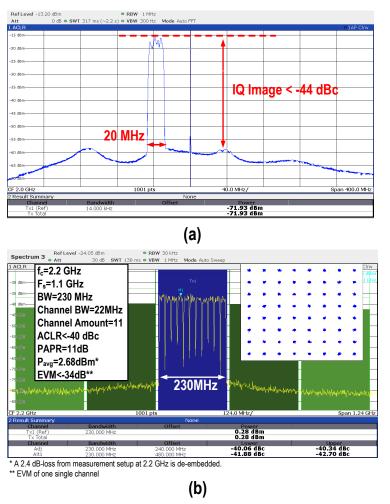

|   |                            | 5.7.1 C                                     | CW Test                                                    | 105        |  |  |  |  |

|   |                            | 5.7.2 S                                     | Single-Tone and Two-Tone Tests                             | 106        |  |  |  |  |

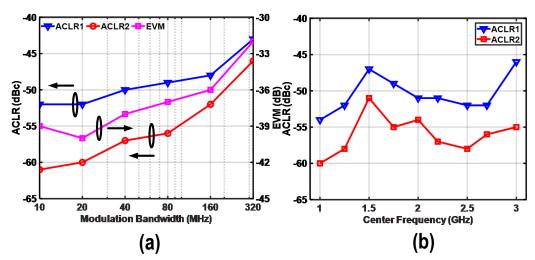

|   |                            | 5.7.3 E                                     | Broadband Signal Test                                      | 106        |  |  |  |  |

|   |                            | 5.7.4 C                                     | Comparison with the State-of-the-Art                       | 111        |  |  |  |  |

|   | 5.8                        | Conclusi                                    | ion                                                        | 111        |  |  |  |  |

|   | Refe                       | erences                                     |                                                            | 112        |  |  |  |  |

| _ |                            | - 10 - :                                    |                                                            |            |  |  |  |  |

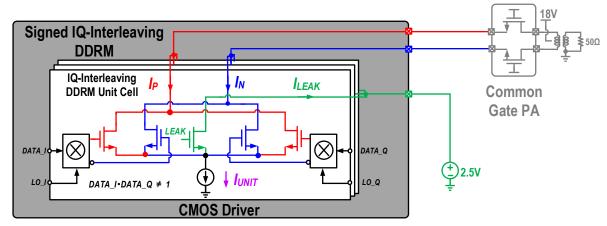

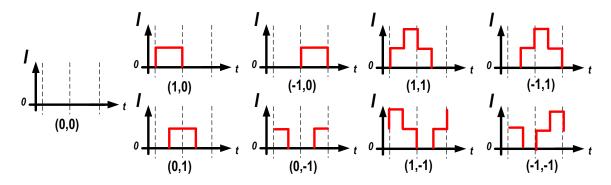

| 6 |                            | , •                                         | erleaved DDRM as a Driver for a Common-Gate/Common-Base PA |            |  |  |  |  |

|   | 6.1                        | Using the DDRM as the Driver for a CG/CB PA |                                                            |            |  |  |  |  |

|   | 6.2                        | Auxiliary Current Division Path             |                                                            |            |  |  |  |  |

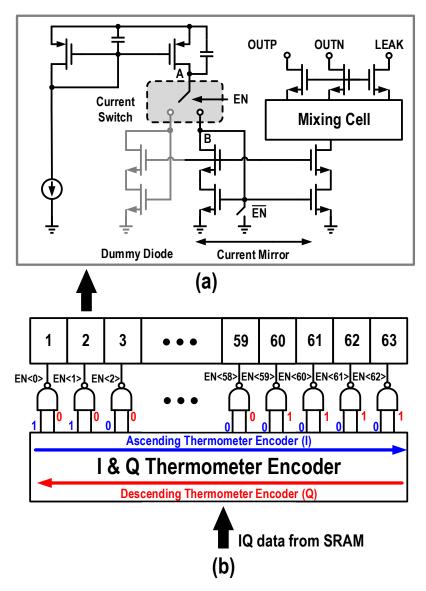

|   | 6.3                        | _                                           | Q-Mapping Unit Cell                                        |            |  |  |  |  |

|   |                            |                                             | Q-Mapping in Signed RFDAC                                  |            |  |  |  |  |

|   |                            |                                             | Comparison with Unsigned IQ-Mapping Technique in Chapter 5 |            |  |  |  |  |

|   |                            |                                             | Design of the Unit Cell                                    |            |  |  |  |  |

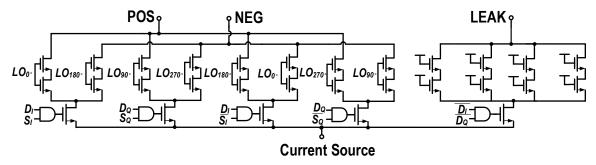

|   | 6.4                        | v o 1                                       |                                                            |            |  |  |  |  |

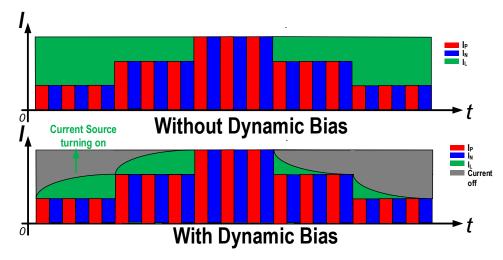

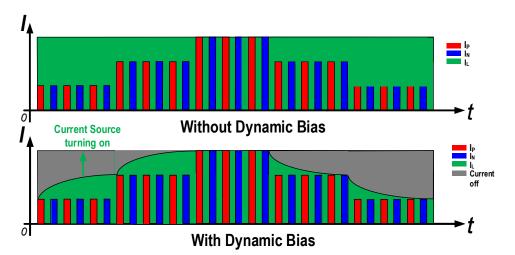

|   |                            |                                             | Concept of Dynamic Biasing Technique                       |            |  |  |  |  |

|   |                            |                                             | mplementation                                              |            |  |  |  |  |

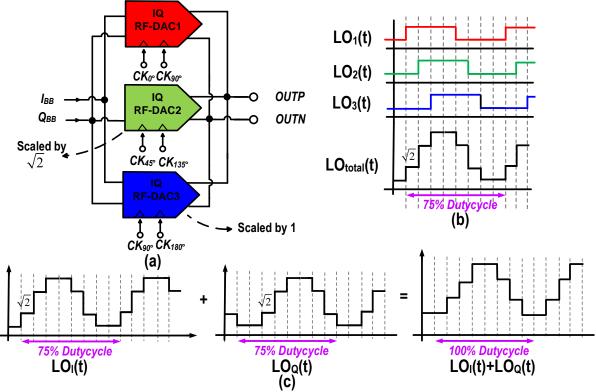

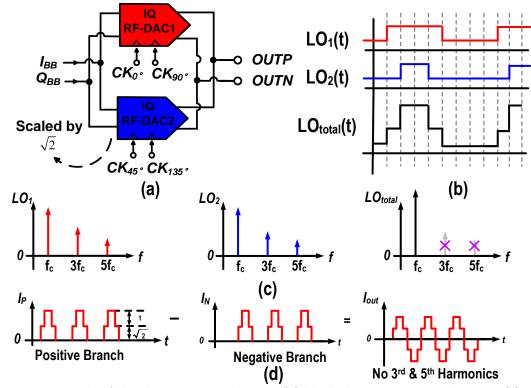

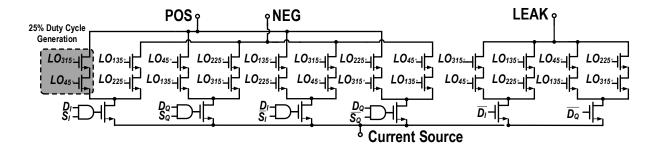

|   | 6.5                        |                                             | Harmonic Rejection Technique                               |            |  |  |  |  |

|   |                            |                                             | Class-B Type Harmonic Rejection                            |            |  |  |  |  |

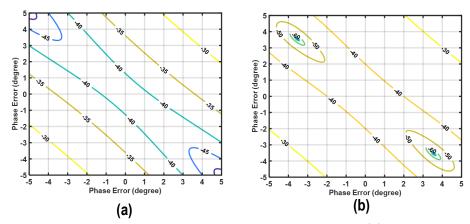

|   |                            | 6.5.2 In                                    | nfluence of Amplitude and Phase Mismatch                   | 132        |  |  |  |  |

iv Contents

|                      |                 | 6.5.3  | Implementation                                 | . 133 |  |

|----------------------|-----------------|--------|------------------------------------------------|-------|--|

|                      | 6.6             | Systen | Architecture                                   | . 136 |  |

|                      | 6.7             | Design | Consideration of the CG/CB PA                  | . 138 |  |

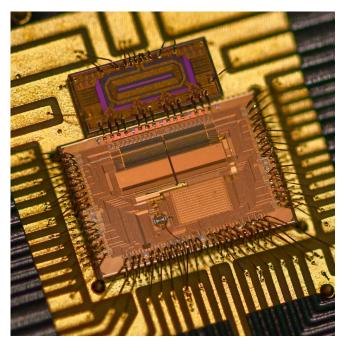

|                      | 6.8             | Experi | mental Results with Standalone CMOS Driver     | . 140 |  |

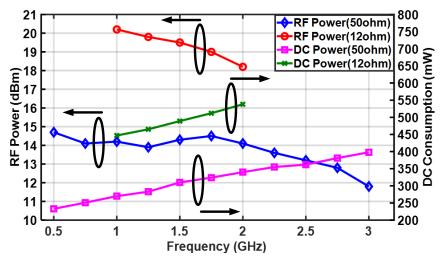

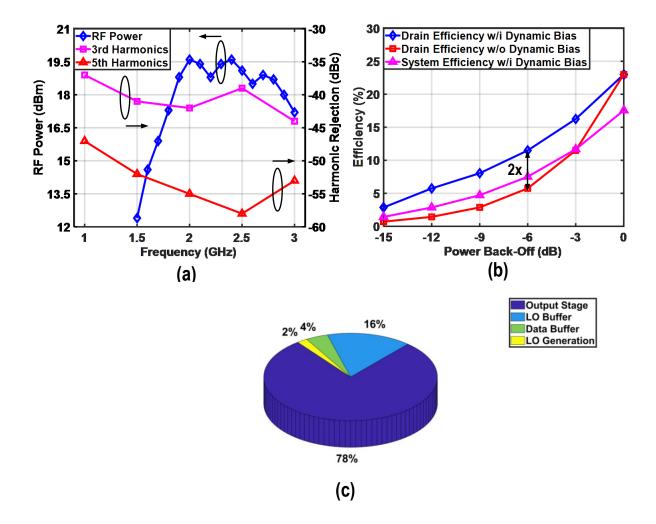

|                      |                 | 6.8.1  | CW Measurement                                 | . 140 |  |

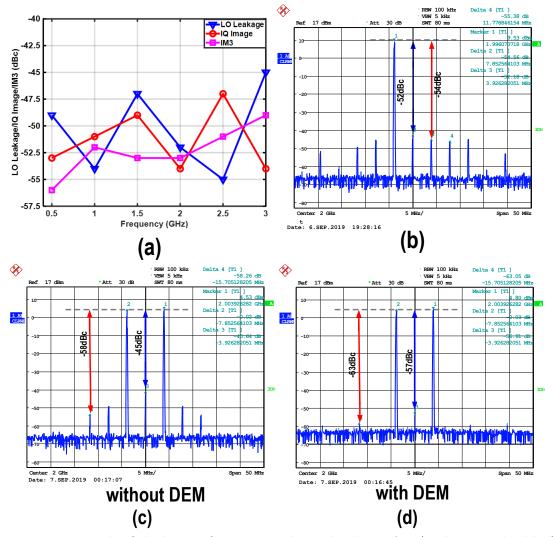

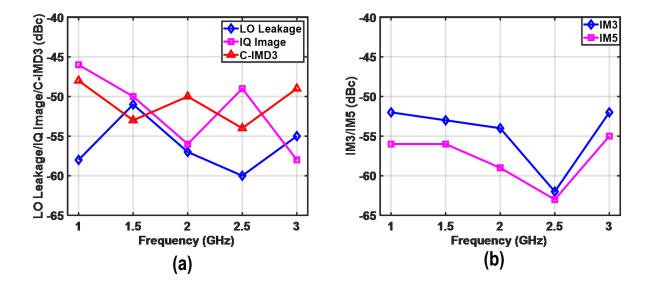

|                      |                 | 6.8.2  | Single-Tone and Two-Tone Measurement           | . 143 |  |

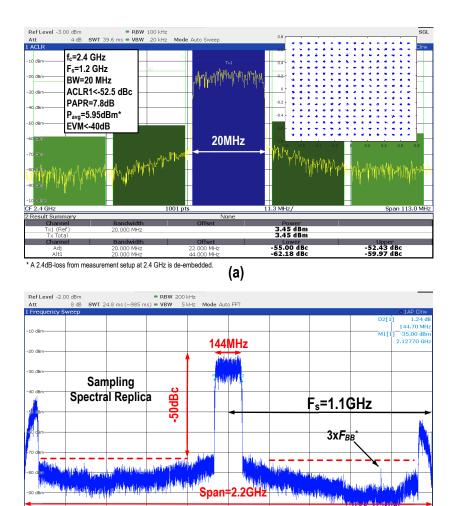

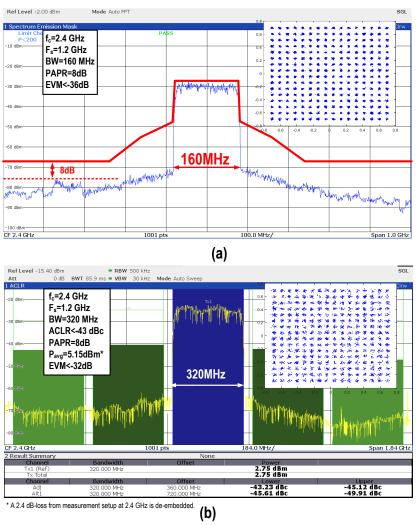

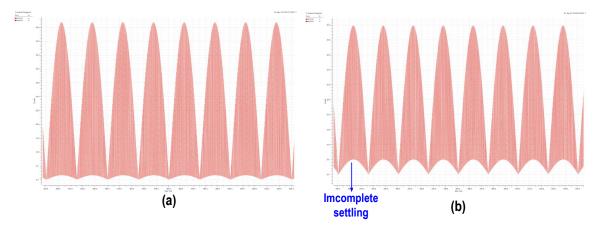

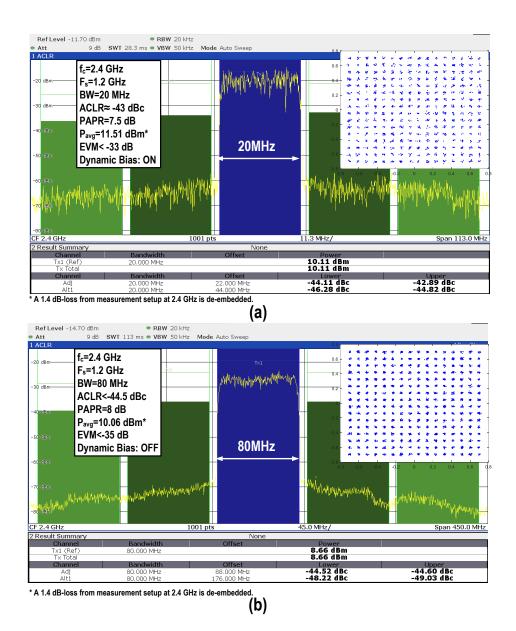

|                      |                 | 6.8.3  | Broadband Signal Measurement                   | . 143 |  |

|                      |                 | 6.8.4  | Comparison to State-of-the-Art TXs             | . 145 |  |

|                      | 6.9             | Experi | mental Results with a CB BJT PA                | . 145 |  |

|                      | 6.10            | Conclu | ısion                                          | . 147 |  |

|                      |                 |        |                                                |       |  |

| 7                    | Con             | clusio | n                                              | 151   |  |

|                      | 7.1             | Thesis | Outcome                                        | . 151 |  |

|                      | 7.2             |        | al Experiences and Contributions to Other DTXs |       |  |

|                      | 7.3             |        | stions for Future Developments                 |       |  |

|                      | Refe            |        |                                                |       |  |

| Li                   | st of           | Figure | es                                             | 156   |  |

| Li                   | st of           | Tables | 3                                              | 163   |  |

| Summary              |                 |        |                                                |       |  |

| Sa                   | Samenvatting    |        |                                                |       |  |

| List of Publications |                 |        |                                                |       |  |

| A                    | Acknowledgement |        |                                                |       |  |

## CHAPTER.

## 1

## Introduction

## 1.1 Introduction

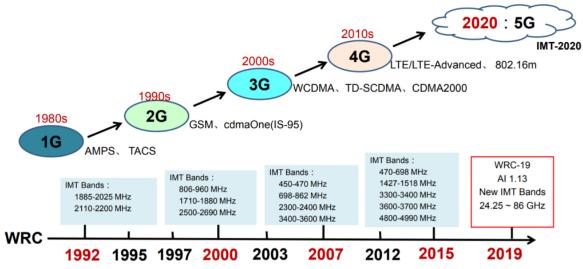

Nowadays, telecommunication is of profound importance to modern society. This is due to the increasing demand for fast and reliable data streams. Cellular communication has evolved over several generations of wireless standards. These have ranged from second-generation cellular, based on the global system for mobile communications (GSM) and enhanced data rates for GSM evolution (EDGE), to third-generation (3G) cellular systems, based on wideband code division access (WCDMA), to fourth-generation (4G) cellular, using 3GPP long-term evolution (LTE), to today's fifth-generation (5G), based on the 3GPP 5G new radio (5G-NR) (Fig. 1.1). Besides cellular communication, various other applications such as localization or near-field communication (NFC) are also reliant on wireless channels. This has resulted in additional standards such as: wireless local area networks (WLANs, IEEE 802.11), bluetooth (BT)/bluetooth low energy (BLE), and ultra-wideband (UWB), which have all been developed to fulfill the very different demands of these wireless links. All these wireless links need to co-exist and be co-integrated into portable devices such as tablets and smartphones.

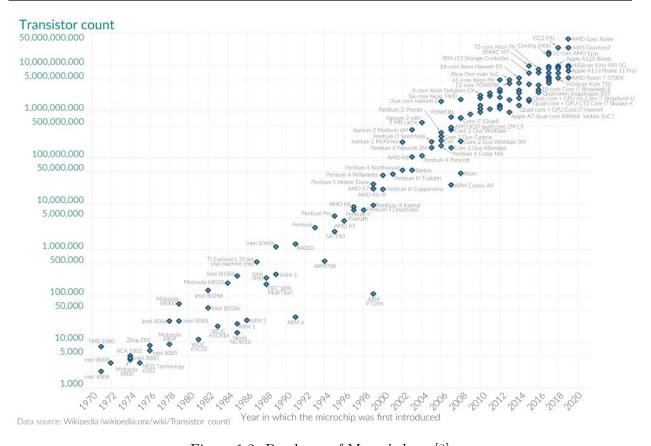

Along with the ongoing iterations in wireless standards, another evolution never seems to stop, namely "Moore's Law". The past decade has witnessed this law, which has dictated industries oriented from complementary-metal-oxide-semiconductor (CMOS) processes, downscale the gate length from 28 nm to 5 nm. For every reduction in size by a factor of two, the transistor density in a CMOS process doubles, while the transistors can operate at a lower supply voltage with reduced parasitics. Consequently, transistors have become faster and more friendly in digital signal

2 Introduction

Figure 1.1: Evolution of cellular mobile communication standards. [1]

processing (DSP) applications. Moreover, their cut-off frequency has improved, enabling their use in RF analog/mixed-signal applications as well.

The improvements in CMOS technology offer a growing potential for expansion into (new) applications in (wireless) market segments which have been traditional strongholds of III-V technology, e.g. GaAs, GaN, or bipolar-based technologies such as SiGe. These more traditional RF technologies, until now, still offer the best performance in terms of linearity, output power, and efficiency when considering purely analog-oriented RF circuits. On the other hand, these analog implementations suffer from low integration, poor design logistics, high costs, while their analog nature yields drift and circuit inaccuracies that can degrade spectral purity. Since CMOS is already the technology of choice for the baseband and signal processing parts of wireless systems, the following question arises: "What if we change the nature of the RF front-end, such that we can start truly benefiting from the power of CMOS in "digital" (switching) operations?"

It is this research question that provides the foundation of this thesis. To answer this research question sufficiently, we will focus on the transmitter (TX) (and its modulator/pre-drivers) of a wireless system. It is this key building block that proves to be the most power-hungry and offers the biggest challenges in electrical performance in terms of: bandwidth, output power, linearity/spectral purity, and efficiency. Consequently, this dissertation will explore novel TX architectures that enable high-performance sub-6 GHz TX systems with simultaneously high spectral purity and efficiency. The concepts proposed in this thesis open up a new realm for revolutionary digital-intensive TX (DTX) line-ups that can offer higher functionality, higher performance, and increased integration at reduced costs. These properties are essential to the successful implementation of massive multiple-input-multiple-output (mMIMO) wireless systems, which require between 4, 16, 32, 64, 128, or even 256 more TX line-ups, compared to conventional wireless systems.

Figure 1.2: Roadmap of Moore's law. [2]

## 1.2 CMOS TXs: Challenges and Opportunities

### 1.2.1 Challenges

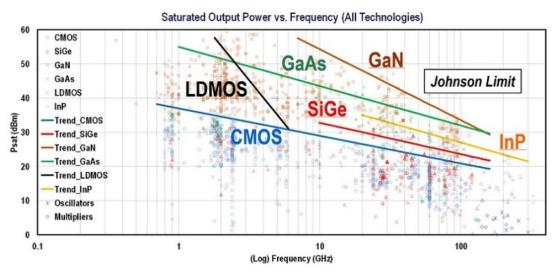

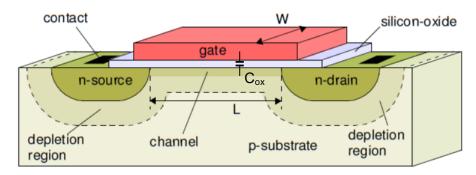

As mentioned above, the high cut-off frequencies of today's CMOS technologies have paved the way for high performance CMOS-based analog circuits. However, their low output power is still one of the biggest obstacles in developing fully integrated TXs for wireless applications. As can be seen in Fig. 1.3, the achievable  $P_{\rm sat}$  of a CMOS power device is much lower than that of devices fabricated in other technologies [3]. One of the reasons for this is the thin gate oxide layer in these modern CMOS processes. The need for such a thin oxide can be understood by considering the side view of the MOS transistor in Fig. 1.4 [4]. To suppress field-effect-transistor (FET) operation degradation, the doping of the drain must be very high. Consequently, to boost transistor gain in analog operation and to keep the gate voltage swings low for digital operation, a very thin gate oxide is required. In the most advanced CMOS processes, the gate oxide is now less than 2 nm. Such a thin oxide layer is not immune to breakdown when a high voltage is applied between the gate and source. Therefore, in most cases, the output power of a CMOS device is restricted by this breakdown voltage and is significantly lower than that of III-V technologies.

Another reason for inferior TX performance is the lossy CMOS substrate and its metal stack. These tend to degrade the performance of on-chip passive devices, such as inductors, transformers,

4 Introduction

Figure 1.3: Saturated output power of different semiconductor device technologies vs. frequency. [3]

and capacitors, which are commonly used in RF circuits. Due to the short distance between the metal layers used for routing and the low ohmic substrate, as well as the absence of thick copper and aluminum layers in a CMOS process, these insertion losses are typically higher than in those of other III-V processes. Therefore, the output power and energy efficiency of CMOS TX chipsets tend to be worse than those in other semiconductor technologies.

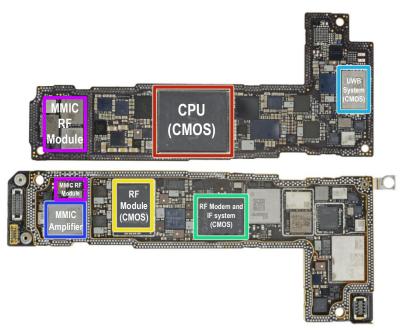

Consequently, to meet the high demands of today's smartphones, monolithic microwave integrated circuit (MMIC)-based power amplifiers (PAs) are used as the RF front-end while CMOS chipsets are only used to drive them. Figure 1.5 presents the front and rear of an Iphone-12 Pro motherboard. The central processing unit (CPU), intermediate frequency (IF) modules, UWB modules, and RF modules are all CMOS technology-based, while the MMIC front-ends are based on III-V technology. In summary, the CMOS chipsets are mainly focused on signal generation and signal decomposition, while III-V front-ends are applied to handle the RF signals going from/to the antennas. Therefore, all the chipsets implemented in III-V technologies are placed close to the antennas. One exception, in Fig. 1.5, is the UWB chipsets. Due to its low RF output power, the related UWB CMOS chipset can directly drive the antenna.

These disadvantages in CMOS process will deteriorate with CMOS process-scaling: the supply voltage decreases with each process evolution along with the related transistor breakdown voltage. Unfortunately, the targeted RF output power does not scale down as CMOS technology evolves. Therefore, it is increasingly more difficult to generate sufficient RF power with the most advanced CMOS technologies.

### 1.2.2 Opportunities

Despite the aforementioned challenges in TX design, employing advanced CMOS technologies also brings some key advantages. First of all, the speed of CMOS circuitry is significantly improved as the technology evolves, providing an excellent platform for DSP. For example, in a 40 nm LP

1.3 Thesis Objective 5

Figure 1.4: Side view of typical CMOS devices. [4]

CMOS process, the minimum delay of a single inverter can drop below 20 ps, which is less than half of the delay in a 0.18  $\mu m$  process. As such, it can provide faster signal processing at an even lower level of power consumption. This enables the use of digital calibration and correction for analog circuits. Furthermore, the FETs in a modern CMOS process exhibit excellent switching characteristics. Switching PAs, such as class-D, class-E, and class-F PAs, can be relatively easily employed with CMOS circuits to achieve better efficiency performance than with analog linear PAs. These rapid improvements have opened the door for so-called DTXs which have narrowed the performance gap between CMOS-based TX implementations and their more conventional counterparts. As a result, recently, DTX has become a popular topic in the RFIC research domain.

## 1.3 Thesis Objective

From the discussion above, one can conclude that the power efficiency and linearity of (traditional) CMOS-based TXs suffer from many compromises made in process and circuit design. To realize high-efficiency, high-linearity sub-6G DTXs in a modern CMOS process, novelties at both the system and circuit level must be introduced. The objective of this thesis is to develop these techniques and illustrate their effectiveness in proof-of-concept demonstrators.

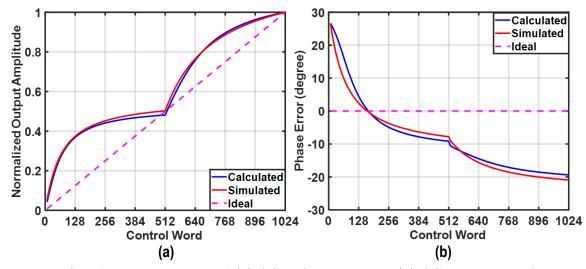

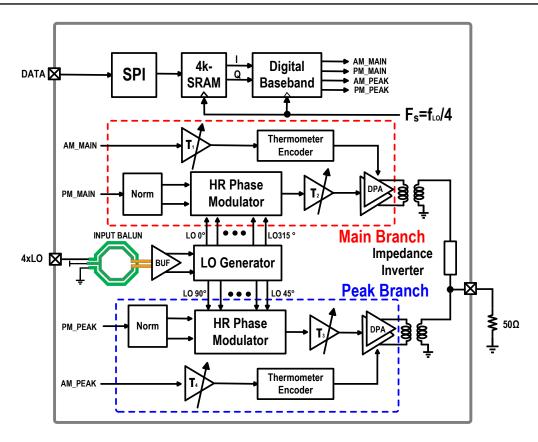

In the first half of this dissertation, the polar TX architecture is chosen as the starting point due to its high efficiency performance. Next, modifications to the polar TX architecture are proposed to extend its modulation bandwidth, while still achieving an output spectrum with high purity. For this purpose, a dedicated ultra-wideband phase modulator has been developed with high phase accuracy. To facilitate the handling of complex modulated signals with a large peak-to-average power ratio (PAPR), a Doherty efficiency enhancement technique has been adopted to further enhance the polar TX-lineup efficiency in power back-off (PBO) region. To improve the overall polar TX line-up efficiency, the entire digital baseband circuitry has been co-integrated on-chip, including coordinate rotation digital computing (CORDIC) and digital pre-distortion (DPD), yielding the first fully functional system-on-chip (SoC) polar Doherty DTX demonstrator.

Although this polar demonstrator demonstrates state-of-the-art linearity performance, it still needs some DPD to meet the spectral mask requirements. In practical low-to-medium power

6 Introduction

Figure 1.5: Front and rear mainboard of an iPhone-12 (Courtesy of Apple Inc.).

applications, such a DPD unit, including an error-correction loop could result in the consumption of too much supply power and therefore might lower the achievable overall TX line-up efficiency. This is especially a concern when targeting very large modulation bandwidths (e.g., > 100 MHz). Therefore, in the second part of this thesis, an alternative approach to the DTX design problem is explored. A very linear, wideband Cartesian DTX architecture is selected as the starting point, after which we aim to improve its power efficiency. Given this strategy, two direct digital RF-modulators (DDRMs) are proposed that provide superior spectral purity and excellent wideband performance, with improved efficiency over conventional Cartesian DTX architectures.

## 1.4 Thesis Outline

This thesis is organized as follows.

• Chapter 2 gives an overview of the fundamentals used in conventional analog TX line-ups and PAs, and the evolution from analog-intensive TX line-ups towards DTX line-ups. In addition, this chapter gives a brief overview of efficiency enhancement techniques to improve the average efficiency of a wireless system when dealing with complex signals such as quadrature amplitude modulation (QAM) or an orthogonal frequency division multiplexing (OFDM) signal.

After the introduction in Chapters 1 and 2, the thesis splits into two parts. The first part is focused on the design and implementation of a fully-integrated digital-intensive polar Doherty TX, which to the best of the author's knowledge, is the first-ever reported fully integrated SoC polar Doherty DTX. The second part of the thesis covers the design of very linear wideband DDRMs. Details of these two different concepts are explained in the following part.

1.4 Thesis Outline 7

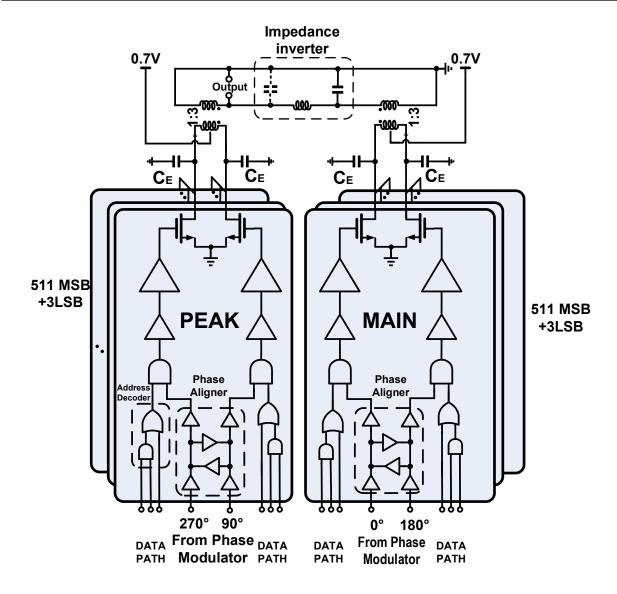

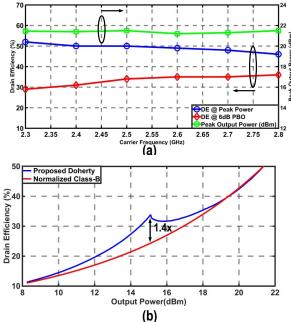

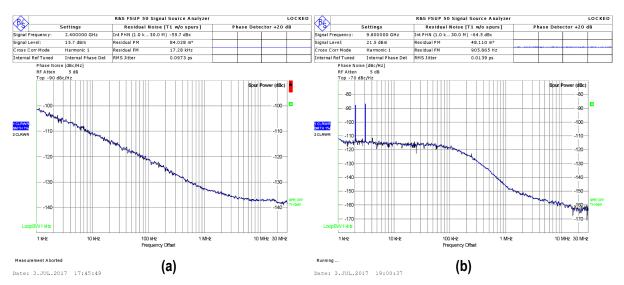

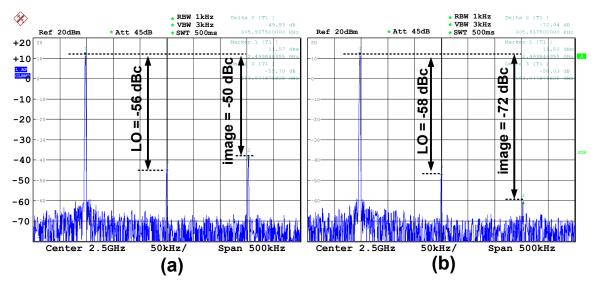

• Chapter 3 provides the system-level discussion of the segmented class-E digital Doherty TX. A comprehensive analysis of the segmented switched-mode class-E output stages with their amplitude-control-word (ACW)-AM and ACW-PM distortion is given and extended here to also cover the behavior of the proposed Doherty configuration. The design and implementation details of the complete DTX chain are provided in this chapter, except for the wideband phase modulator which is discussed in Chapter 4. The realized Doherty digital PA (DPA) achieves a measured drain efficiency of respectively 49.4 % at peak power and 33.7 % drain efficiency at its 6 dB PBO point. Using the on-chip DPD functionality, it can support 40 MHz 64-QAM signals at an operating frequency of 2.4 GHz, while achieving an average drain efficiency of 25 %.

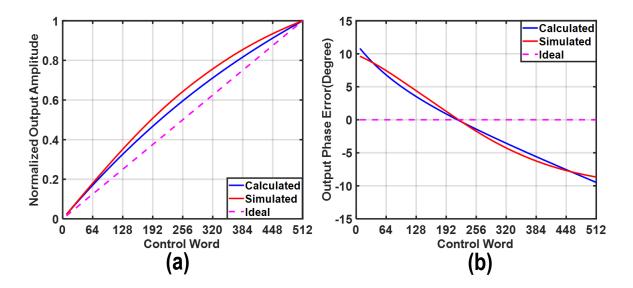

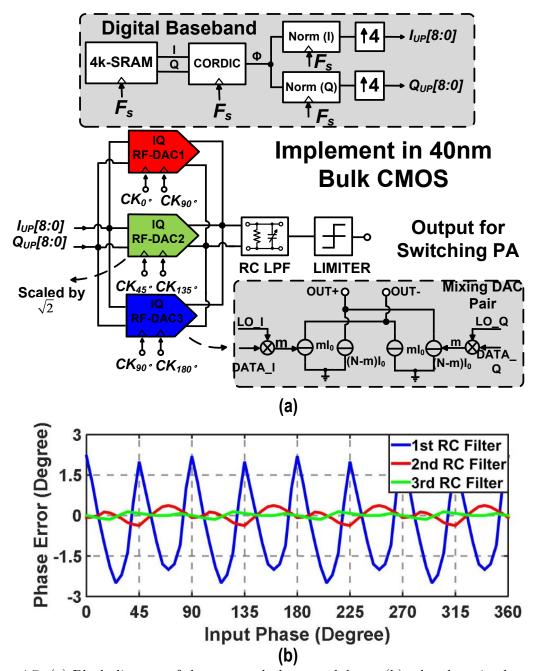

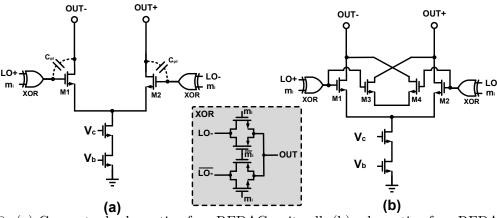

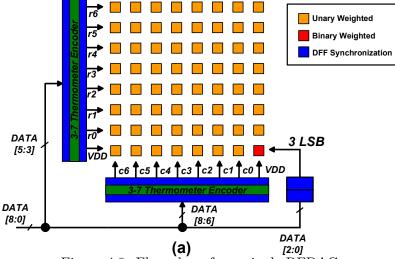

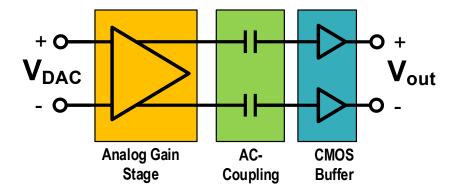

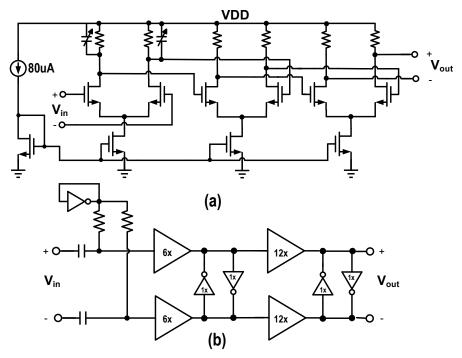

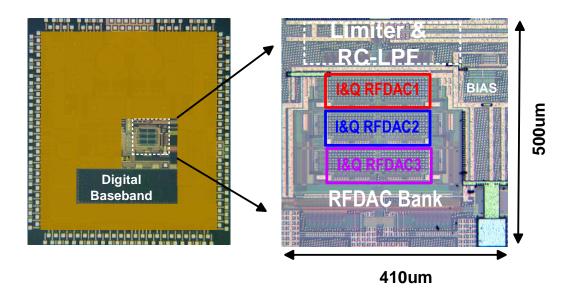

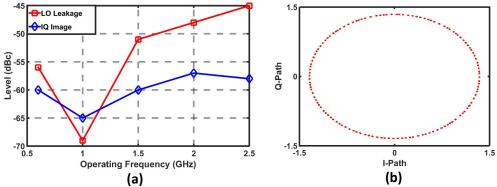

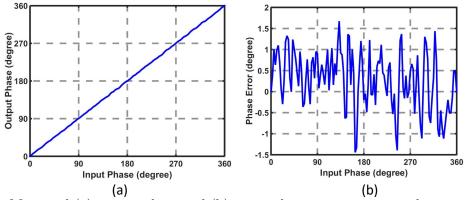

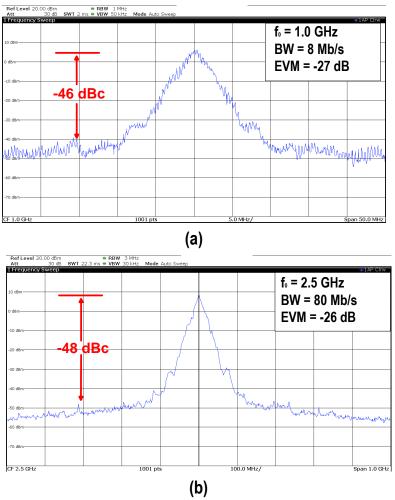

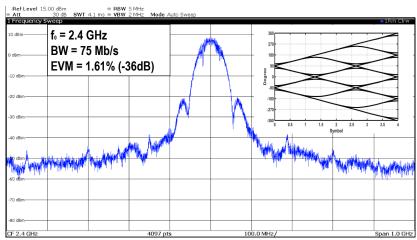

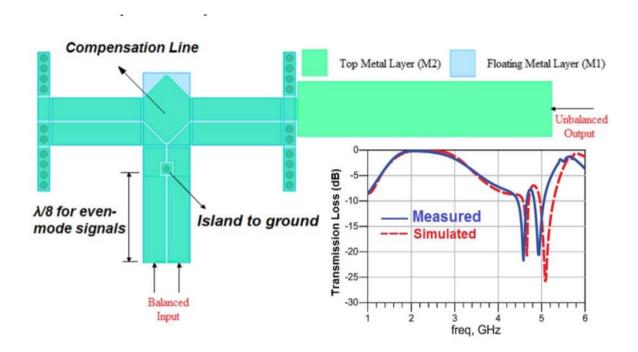

• Chapter 4 concentrates on the design of an ultra-wideband phase modulator. The severe bandwidth expansion in polar TXs can exceed 3× to 5× the original modulation bandwidth, which yields severe design challenges for the phase modulator in these systems. Any bandwidth constraint in such a phase modulator results in limitations on the spectral purity of the output signal. In these phase modulators, a common source of phase distortion is the presence of third-order counter-intermodulation C-IMD3) products, which result from the folding back of intermodulation (IM) products around the higher harmonics. In the proposed ultra-wideband phase modulator, harmonic rejection (HR) techniques are deployed to suppress these undesired mixing products, and thus, enhancing its phase linearity. To enlarge its video bandwidth, the proposed phase modulator uses an RFDAC-based Cartesian architecture that employs a current-steering topology. Measurement results show that this phase modulator can successfully support 80 MHz of modulation bandwidth with an error-vector-magnitude (EVM) of better than -27 dB, making it an excellent candidate for realizing (future) wideband polar TXs.

Chapters 5 and 6 cover the second part of this thesis and are mainly focused on the DDRM architecture to achieve high linearity performance combined with very large modulation bandwidths. In addition, several dedicated efficiency enhancement techniques are proposed for this architecture.

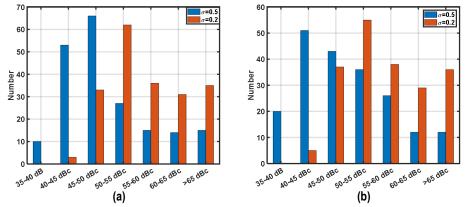

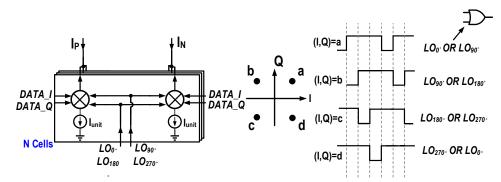

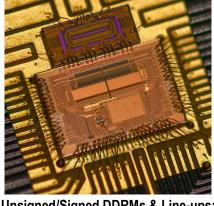

• Chapter 5 provides first a comprehensive comparison between DPA based Cartesian DTXs and DDRMs. This shows the advantages and disadvantages of these two increasingly popular architectures. Following that, we propose an advanced IQ-mapping technique for unsigned DDRM operation, which offers both an efficiency and linearity advantage over conventional DDRM implementations. These improved properties are also supported by an analysis. The proposed DDRM architecture is demonstrated to support a video bandwidth up to 320 MHz without DPD.

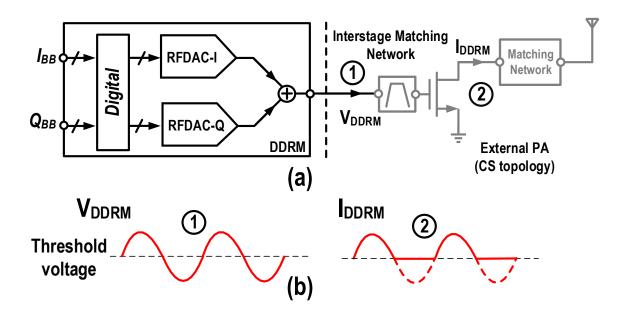

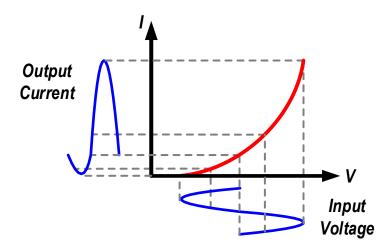

Although unsigned DDRMs can provide superior linearity performance, the PAs they are driving is the bottleneck in the linearity of the entire line-up. Conventionally, these PAs are configured as a common source (CS)/common emitter (CE) topology, which yields the highest gain but suffers from non-linear I-V relations. In a traditional analog design, these non-linear I-V curves are utilized

8 Introduction

to clip the waveforms in the output stage, and as such, boost the efficiency. However, at the same time, it is this non-linear behavior that yields distortion in the TX output signal.

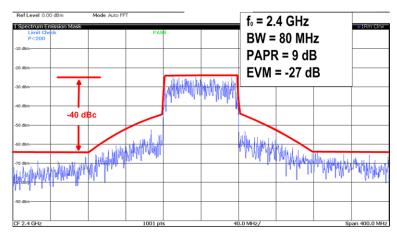

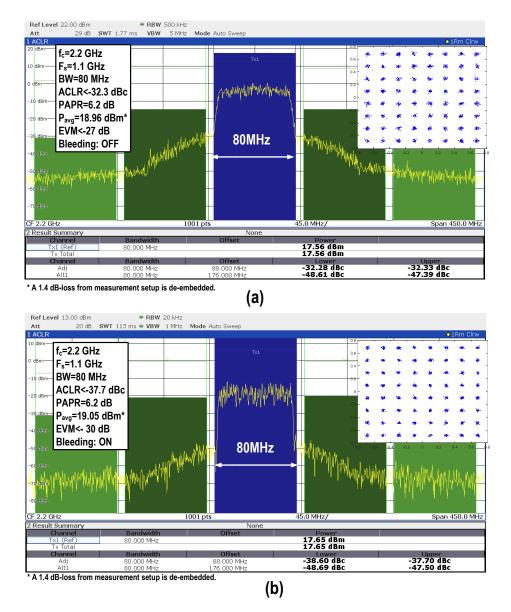

- Chapter 6, addresses this problem by introducing a new TX line-up based on a signed DDRM that drives a common-gate (CG)/common-base (CB) output stage in pure current-mode operation. In this approach, the waveform clipping, needed for improving the efficiency in the CG/CB PA, is implemented by introducing a novel auxiliary current division path in the DDRM unit cells which allows engineering of the current waveform. Furthermore, signed IQ-mapping, dynamic biasing, and class-B-like HR techniques are also applied to the proposed driver to boost the efficiency and linearity of the line-up. To adapt to the proposed CMOS driver, several special considerations are included in the design and layout of the CG/CB PA. Based on the experimental results, the proposed driver operates over a 1-3 GHz frequency range while generating 19.6 dBm peak RF power with 505 mW DC power consumption at 2.4 GHz. For a 160 MHz 256-QAM signal, the measured adjacent channel leakage ratio (ACLR) is better than -40.5 dBc. When connected to a CB SiGe PA, the peak output power is about 27 dBm with a system efficiency of 20 %. When transmitting an 80 MHz 64-QAM signal at 2.2 GHz, the measured ACLR is -32 and -37.7 dBc, without and with static bleeding current, respectively, with an EVM of -27 and -30 dB, respectively.

- Chapter 7, concludes the thesis with some recommendations for the direction of future work.

## References

- [1] X. Chen, "Status and Trends of Global 5G spectrum,"

- [2] Wikipedia, https://en.wikipedia.org/wiki/Moore%27s law

- [3] H. Wang, T. Huang, N. Sasikanth Mannem, J. Lee, E. Garay, D. Munzer, E. Liu, Y. Liu, B. Lin, M. Eleraky, S. Li, F. Wang, A. S. Ahmed, C. Snyder, S. Lee, H. T. Nguyen, and M. Smith, "Power Amplifiers Performance Survey 2000-Present," [Online]. Available: https://gems.ece.gatech.edu/PA\_survey.html

- [4] K. Bult, "Basic analog CMOS design: an intuitive approach" TU Delft 2012.

## CHAPTER

# 2

## Wireless TX line-ups Review

This chapter gives an overview of the most popular wireless TX line-ups and PA architectures of today. As such, Section 2.1 is focused on the PA output stage itself and compares the efficiency performance of several conventional analog linear PAs. Sections 2.2 and 2.3 review traditional analog Cartesian and polar (up-converting) TX architectures, respectively. With this foundation in place, the digital-intensive counterparts of these popular architectures are introduced in Section 2.4. To address the needs of modern high-order modulation schemes, various efficiency enhancement techniques are discussed in Section 2.5. Finally, Section 2.6 concludes this chapter.

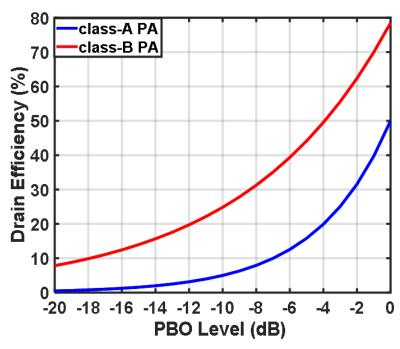

## 2.1 Efficiency of Class-A, Class-B, and Class-AB PAs in Power Back-Off Region

Linear PAs are often categorized according to their conduction angle, which is determined by the bias condition used in the final stage. When the resulting conduction angle is  $2\pi$  or  $\pi$ , the PAs are categorized as class-A or class-B. Class-AB PA operation occurs when the conduction angle is between  $\pi$  and  $2\pi$ . The use of lower conduction angles is mainly motivated by the ambition to improve PA efficiency. Different efficiency definitions are used in the literature. However, in our discussion, we will use the drain efficiency  $\eta_{\text{drain}}$ . This term is defined as the RF output power delivered to the load normalized by the DC power consumption which drawn from the supply source

connected to the drain of a linear PA:

$$\eta_{\text{drain}} = \frac{P_{\text{RF}}}{P_{\text{DC}}} = \frac{V_{\text{RF}}}{VDD} \cdot \frac{I_{\text{RF}}}{I_{\text{DC}}}$$

(2.1)

where  $P_{\rm RF}$  is the RF output power delivered to the load,  $P_{\rm DC}$  is the total DC power consumption from the supply,  $I_{\rm RF}$  is the root-mean-square (R.M.S) output current,  $V_{\rm RF}$  is the R.M.S output voltage, VDD is the supply voltage connected to the train, and  $I_{\rm DC}$  is the DC current drawn from the supply. As shown in (2.1), the drain efficiency can be split into two parts: the ratio between the RF voltage and DC voltage and the ratio between the RF current and DC current. In an ideal case, when the PA is at peak power, the maximum instantaneous voltage  $V_{\rm max}$  equals VDD. In a class-A PA, when  $V_{\rm max}$  equals VDD, then the R.M.S value of the sinusoidal output voltage is:

$$V_{\rm RF} = \frac{\rm VDD}{\sqrt{2}} \tag{2.2}$$

In a proper class-A design, the drain current at the peak power has an amplitude equal to the class-A quiescent current:

$$I_{\rm RF} = \frac{I_{\rm DC}}{\sqrt{2}} \tag{2.3}$$

Therefore, after substituting (2.2) and (2.3) with (2.1), the peak drain efficiency of a class-A PA, occurring at peak power, is:

$$\eta_{\text{peak,class-A}} = \frac{V_{\text{RF}}}{\text{VDD}} \cdot \frac{I_{\text{RF}}}{I_{\text{DC}}} = 50 \%$$

(2.4)

Consequently, when the output amplitude is only half of the peak amplitude, both output voltage and current are half of its peak counterpart. Therefore, the drain efficiency in the 6 dB PBO region (25 % of the peak power) for a class-A PA is:

$$\eta_{\text{6dB,class-A}} = 12.5 \% = \frac{1}{4} \eta_{\text{peak,class-A}}$$

(2.5)

In class-B PAs, the drain current is a half-wave rectified sine-wave. Since the conductance angle equals  $\pi$ , the R.M.S value of output current is:

$$I_{\text{OUT}} = \frac{2\sqrt{2}}{\pi} I_{\text{DC}} \tag{2.6}$$

while the maximum  $V_{\text{OUT}}$  is the same as VDD, which is:

$$V_{\rm RF} = \frac{\rm VDD}{\sqrt{2}} \tag{2.7}$$

Consequently, the maximum drain efficiency for a class-B PA is:

$$\eta_{\text{peak,class-B}} = \frac{V_{\text{RF}}}{\text{VDD}} \cdot \frac{I_{\text{RF}}}{I_{\text{DC}}} = \frac{\pi}{4} = 78.5 \%$$

(2.8)

Figure 2.1: Drain efficiency of an ideal class-A and class-B power amplifier versus PBO level, relative to the peak power condition at 0 dB.

In the 6 dB PBO region, the DC current is proportionally reduced with respect to the output current while VDD remains the same, thus:

$$\eta_{\text{6dB,class-B}} = 39.2 \% = \frac{1}{2} \eta_{\text{peak,class-B}}$$

(2.9)

Therefore, the class-B PA can achieve higher drain efficiency performance both at peak power (78.5 % vs. 50 %), and in the 6 dB PBO region (39.2 % vs. 12.5 %), as shown in Fig. 2.1. However, linearity is typically degraded in a class-B PA compared to a class-A PA due to the non-linear I-V relationship with the amplifying transistor. In practice, to balance the efficiency and linearity, the linear PA is usually biased between class-A and class-B mode (class-AB), which requires the conductance angle to be between  $\pi$  and  $2\pi$ . The efficiency and linearity properties of a class-AB PA are also between those of a class-A PA and a class-B PA.

In analog mixed-signal or digital-intensive designs, the definition of class-A and class-B is ultimately more general. Class-A circuits are typically defined as cases where the DC current does not scale down with the amplitude of the output signal, while class-B circuits are related to the situations where the DC current does scale down linearly with the output signal. Comparable to the linear PA discussions, digital-intensive class-AB-like circuits are referred to as in-between types of class-A and class-B operation.

Figure 2.2: Block diagram of an analog intensive Cartesian TX.

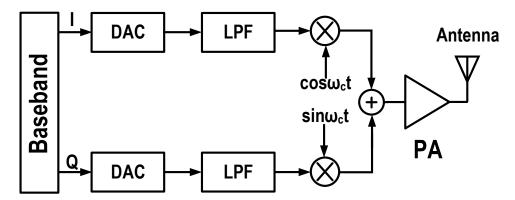

## 2.2 Analog Cartesian Line-Ups

Typically, an RF TX line-up should perform signal modulation, up-conversion, and amplification. A typical block diagram of the conventional analog Cartesian line-up is shown into Fig. 2.2. Usually, it consists of a digital baseband, digital-to-analog converters (DACs), low-pass filters (LPFs), mixers, and a PA. In modern wireless TXs, the data provided to be transmitted is mostly in the form of quadrature signals, i.e., IQ data. Such IQ signals are pre-processed in a digital baseband block. A typical processing step is the use of pulse shaping into transform the rectangular data waveform to a much smoother pulse shape, and as such, suppress inter-symbol interference (ISI). Although such pulse shaping can also be done in the analog domain, such a filter would be bulky, especially for a lower signal bandwidth. What is more, different wireless standards usually need different pulse shaping. For example, in Gauss frequency shift keying (GFSK), the pulse shape is Gaussian, but in QAM, it is to use a square-root raised cosine (SRRC) filter. Therefore, to make the TX unit more compact and compatible with various wireless standards, this pulse shaping is almost exclusively done in the digital domain. After the digital baseband, the digital data with a sampling rate of  $F_s$  is transferred to the analog domain by the baseband DAC, which implicitly acts as a zero-order hold (ZOH) interpolation filter. Consequently, since there will be sampling spectral replicas at  $F_s$  and its harmonics, here a LPF is used to filter out the sampling spectral replicas. Next, a quadrature mixer configuration is used to up-convert the IQ baseband signals to the RF domain, where the resulting complex modulated signal will further be amplified by the drivers and final PA stage before transmission by the antenna.

In these analog-intensive direct-conversion TXs, the design challenges are mostly centered around the PA design, which needs to provide the targeted output power to the antenna with adequate linearity and good efficiency. These PAs typically employ large transistors. Therefore, often there will be a pre-driver needed between the mixers and PA. Note that in a TX line-up, since the signal amplitude is high, the noise of the mixers is considered to be less critical than in the receiver chain.

2.3 Polar TXs

Figure 2.3: Block diagram of a polar TX line-up.

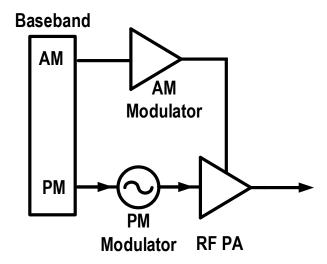

## 2.3 Polar TXs

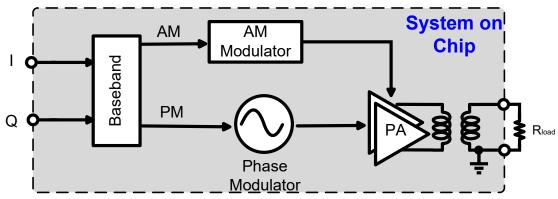

Another popular TX architecture is the polar architecture, which is sometimes also known as the envelope elimination and restoration (EER) configuration. A typical polar TX line-up is shown in Fig. 2.3. Here the IQ signal decomposes into a digital amplitude modulation (AM) and phase modulation (PM) by applying a CORDIC algorithm during the digital baseband signal processing.

$$\begin{cases} AM = \sqrt{I^2 + Q^2} \\ PM = \tan^{-1} \frac{Q}{I} \end{cases}$$

(2.10)

The PM data is used to modulate the LO signal in a phase modulator. The resulting analog phase-modulated output signal, with a constant envelope, is amplified by an efficient PA, while the AM information is restored through the PA supply modulation. Because the AM information is conveyed by the AM modulation, a non-linear switching PA (e.g., class-D, class-E, or class-F) can be employed to amplify the PM signal. This allows a much higher efficiency to be achieved compared to the use of linear PAs (e.g., class-A and class-AB PAs). By using an ideal switching PA and DC-to-DC supply converter, this architecture can achieve 100 % efficiency in theory.

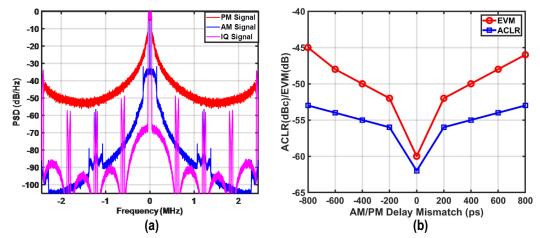

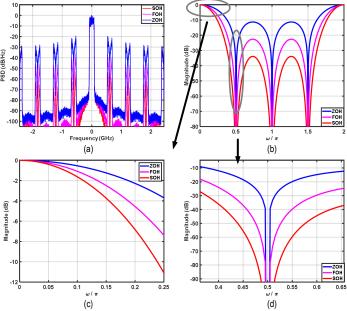

Although the use of a switching PA will boost the efficiency in polar TXs, it comes at the expense of bandwidth extension. Figure 2.4(a) shows the spectrum for the original signal, and the related AM and PM signal in a polar TX. The bandwidth of the original signal in Figure 2.4(a) is only 20 MHz, but due to the non-linear decomposition in (2.10), the bandwidths of the AM and PM signal are extended. In particular, the PM signal will have a bandwidth that is 3-5 times higher than that of the original signal. As a consequence, the phase modulator must be able to handle a signal with a much larger bandwidth than the original signal, which significantly increases the design burden. What is worse, any mismatch between the group delay in the AM and PM path is also a source of distortion. Such mismatch will result in phase errors which can severely corrupt

Figure 2.4: (a) Spectrum of IQ signal, AM and PM signal in a polar TX; (b) degradation of ACLR and EVM vs. AM/PM delay mismatch in a polar TX with 10 MHz 64-QAM signal.

ACLR and EVM performance. This is illustrated in Fig. 2.4(b). When considering a 10 MHz 64-QAM signal and a delay mismatch of 800 ps, the EVM and ACLR are degraded to -45 dB and -54 dBc, respectively. Note that this delay alignment requirement becomes gradually stringent with increasing video bandwidth.

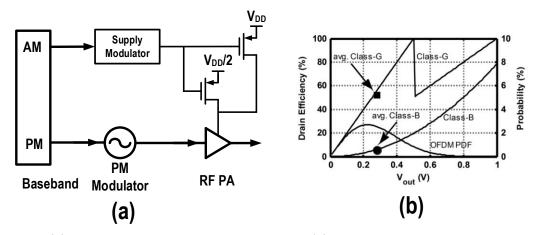

## 2.3.1 Supply Modulators

Supply modulators shown in Fig. 2.4(a) need to handle at least three times the bandwidth of original bandwidth. Therefore, it usually appears as the efficiency and linearity bottleneck in a polar TX.

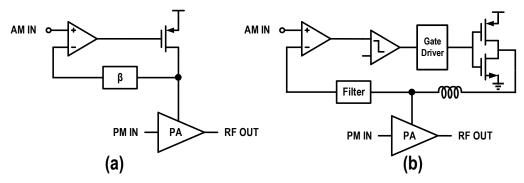

The simplest implementation of a supply modulator is using a linear voltage regulator (shown in Fig. 2.5(a)). This approach provides a reasonable bandwidth, a good power supply rejection ratio (PSRR), and potentially excellent spectral purity ([1]). However, in the PBO region, its efficiency would still follow the class-B-like roll-off. This can be understood by considering that the switching PA in Fig. 2.5(a) would draw the same current from its regulated supply as the linear regulator does from the supply voltage. Another way of looking at it would be that the voltage drop-over of the linear regulator is wasted and, as such, degrades the overall TX efficiency. In these configurations, the feedback loop will, in the end, limit the bandwidth of the supply modulator.

A switching regulator dynamic DC-to-DC converter (Fig. 2.5(b)) has been proposed to boost the efficiency in the literature ([2]). However, these configurations can only support small video bandwidths that comprise only a small fraction of the switching frequency. Ignoring this constraint would result in voltage ripples on their outputs, yielding extra spurious components. To support higher bandwidths while still meeting the stringent spectral requirements from modern communication systems, a sufficiently high switching frequency in the DC-DC converter is required, thus yielding a degradation of the efficiency.

Figure 2.5: Supply modulator: (a) linear regulator; (b) switching regulator.

## 2.3.2 Envelope Tracking System

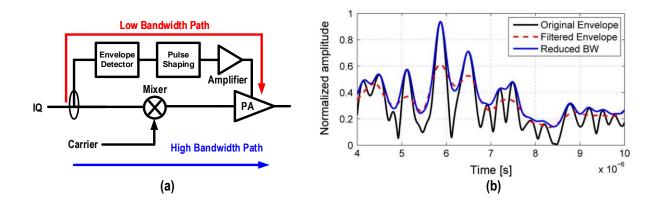

The key bottleneck to overcome for the supply modulator in a polar system in achieving high bandwidth lies in the bandwidth limitation of the feedback loop. Other bottlenecks are the phase modulator bandwidth and the precise AM-PM alignment requirement in terms of group delay. Envelope Tracking (ET) systems have been proposed to avoid the problem of the feedback loop bandwidth and AM-PM path alignment ([3] and [4]). A conceptual block diagram of this type of system is shown in Fig. 2.6. In an ET system, the AM information of the TX signal is used to control a supply modulator, such that it tracks the desired output signal envelope with some margin (voltage headroom). In contrast to an EER system, the signal entering the PA will contain both AM and PM information, as such avoiding the alignment problem. Consequently, a linear PA is needed for the RF signal amplification. It is now the PA itself that determines the signal quality rather than the AM path with a supply modulator, as in EER. This approach makes this ET architecture much more relaxed in terms of implementation, and therefore higher bandwidths can be achieved compared to the EER system. The achievable efficiency of an ET system can be very good ([4]), but it is not as high as that of an EER system due to the use of a linear amplifier and the remaining voltage headroom in the supply voltage tracking. Also, the ET supply modulator can be relaxed more in terms of bandwidth (low bandwidth path Fig. 2.6) since it no longer needs to precisely track/define the output signal envelope. By using appropriate data processing to reduce the bandwidth, it can be made even relatively slow. By using these ET approaches, bandwidths up to 40 MHz ([4]) can be achieved.

## 2.4 Digital-Intensive TX Line-Ups

Recently, DTXs have gained attention due to their excellent hardware scalability with nanoscale CMOS and the great potential to incorporate extensive digital correction circuitries such as DPD. These properties are essential in achieving high system integration, linearity, and efficiency at a low cost. This section will give a short review of existing DTX architectures. It mainly categorizes DTXs into two categories: polar DTXs and Cartesian DTXs. For the Cartesian DTXs, we will discuss the DPA-based Cartesian DTXs and DDRMs.

Figure 2.6: (a) Block diagram of envelope tracking system; (b) time domain waveform of AM signal [3].

Figure 2.7: Equivalent model of a DPA in polar DTXs.

## 2.4.1 DPAs and Digital-Intensive Polar TXs

One of the underlying reasons for an ET system that it can support higher video bandwidth than an EER system is the fact that the up-converter is an open-loop system, which can provide larger bandwidths than a close-loop system. Similarly, direct-digital amplitude modulation is also an open-loop approach that can be applied in polar DTXs. As such, the digital-intensive approach opens up new possibilities to optimize for both TX efficiency and linearity ([5] and [6]).

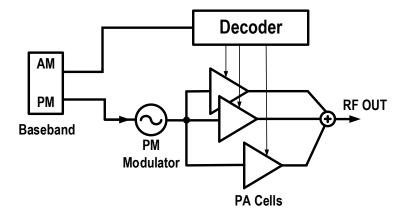

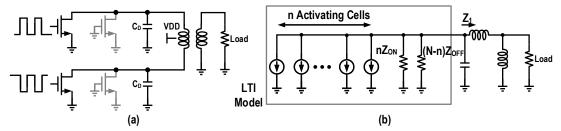

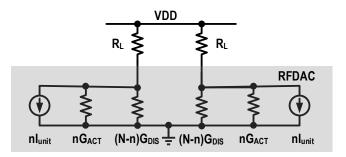

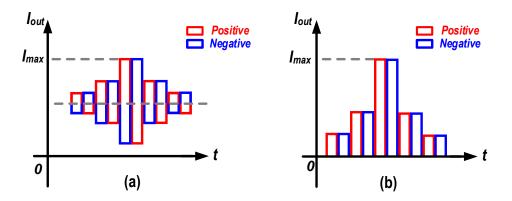

In a direct-digital amplitude modulator, AM modulation is achieved by turning on and off a discrete number of PA unit elements. A conceptual block diagram of this approach is shown in Fig. 2.8. Since direct amplitude modulation is realized with the RFDAC operation, there is no longer a need for a baseband DAC and frequency up-converter, which allows for a decrease in the power consumption of the overall system.

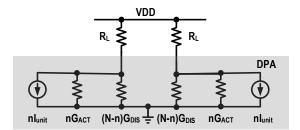

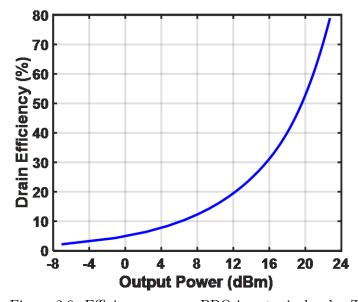

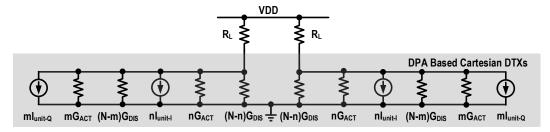

An equivalent model of the DPA is shown in Fig. 2.7, where  $G_{\rm ACT}$  and  $G_{\rm DIS}$  stand for the admittance of each PA unit cell in the on and off state, respectively. To achieve a high efficiency,  $G_{\rm ACT}$  should be much larger than  $G_{\rm DIS}$ . The fact that this configuration functions as a (non-linear) resistive divider implies that will corrupt the linearity. Therefore, in practical implementations, there will be a trade-off between the linearity and efficiency performance with straightforward linear activation of the PA elements. This will be analyzed in more detail in Chapter 3. When benchmarking the direct-digital amplitude modulation technique for its efficiency versus PBO behaviors, as shown in Fig. 2.9, again, we find a similar class-B-like efficiency roll-off, since the

Figure 2.8: Block diagram of a polar DTX with direct AM modulation.

Figure 2.9: Efficiency versus. PBO in a typical polar TX.

output current scales with the signal amplitude. Note that the achievable (theoretical) peak efficiency will depend on the applied (harmonic) impedance matching of the PA stage and duty-cycle ([7] and [8]).

In terms of spectral purity, DPAs are often inferior to their linear counterparts for two reasons. First, their sample and hold nature, which combined with the fact no LPF is taking place (as in the analog TX line-up), yields spectral replicas at the sampling frequency and its harmonics. Second, the effective number of bits (ENOB) is usually limited to 3-6 bits, which limits the out-of-band (OOB) noise floor. In some cases, the DPA needs RF filtering at its output to lower the OOB noise floor. This can severely limit its application in high-power wireless infrastructure systems, where stringent spectral performance is required.

As in the analog polar approach, the digital-intensive polar TX architecture also requires a wideband phase modulator. A phase modulator for this purpose using a digital-intensive approach will be discussed in Chapter 4. Consequently, by using digital-intensive AM and PM modulators,

Figure 2.10: (a) Block diagram of a DPA-based Cartesian DTX and (b) its constellation diagram. [10]

polar TXs can be made truly "digital". This also provides an excellent starting point to incorporate the digital-extensive digital signal correction circuitry such as DPD on the same transceiver IC. Note that in a polar system, this is done quite easily due to its relatively independent amplitude-control-word (ACW)-AM and ACW-PM behavior, allowing a two times 1D correction approach ([5]).

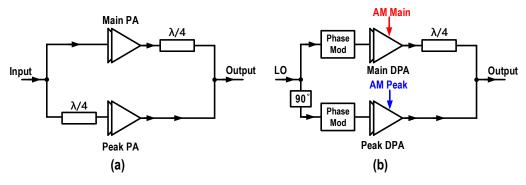

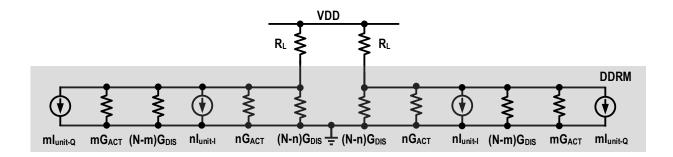

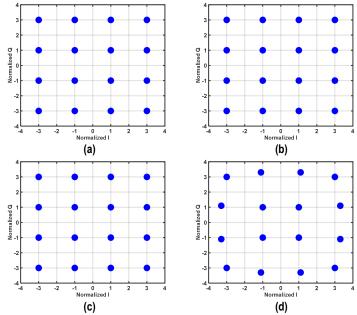

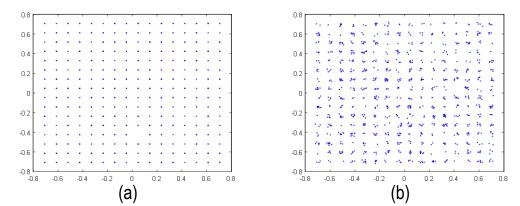

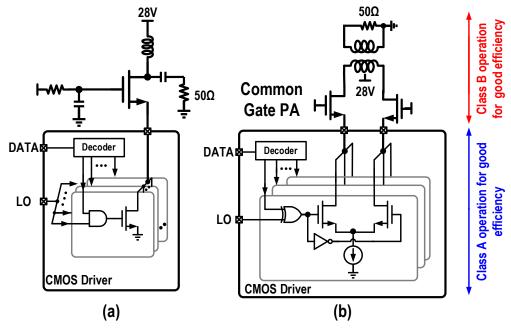

## 2.4.2 DPA-Based Cartesian DTXs

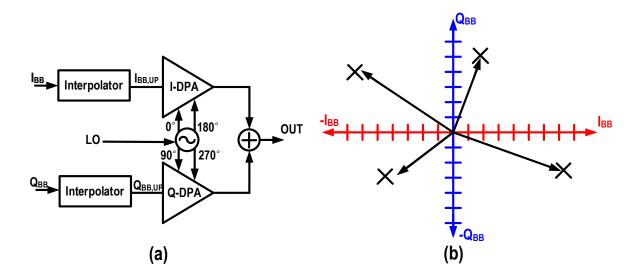

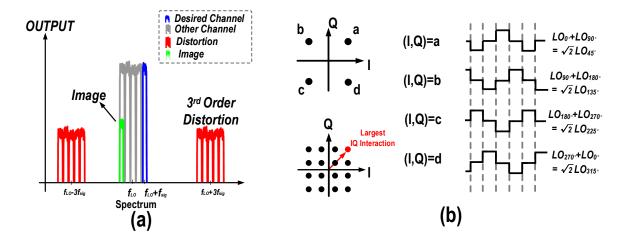

A conceptual diagram of a Cartesian-based DTX is shown in Fig. 2.10(a), which is firstly introduced in [9]. The key difference with the polar approach is that in the Cartesian DTX, there are two DPA branches (instead of one). Each of the DPAs has a fixed phase input signal, which are all 90° apart (this instead of a single input with a varying phase, as found in the polar DTX). At the output of a Cartesian DTX, vector summing is applied. As a result, the entire constellation diagram can be constructed (Fig. 2.10(b)). An advantage of this architecture over polar DTXs is the absence of a wideband phase modulator, which is often the bottleneck to achieving high linearity for large modulation bandwidth. Compared to the conventional analog Cartesian TX in Section 2.2, these Cartesian DTXs can achieve higher system efficiency due to the absence of baseband DACs and quadrature mixers, which typically all operate in class-A conditions.

Unfortunately, the linearity of these Cartesian DTXs is typically not as good as that of a conventional analog Cartesian line-up. This is mainly due to the I-branch/Q-branch interaction in the Cartesian DTX. This interaction worsens when using 50 % duty-cycle summing [11] or when aiming for a high efficiency implementation of the I- and Q-DPA branches [10], which do not rely on the use of unit cell current sources. IQ-interaction cannot be modeled as AM-AM and AM-PM distortion as it requires, in contrast to polar systems (two-times 1D), a full 2-dimensional (2D)

Figure 2.11: Equivalent model of DPA-based Cartesian DTXs.

Figure 2.12: Typical schematic of a (a) baseband DAC and (b) active up-mixer. signal correction in the DPD approach. An analysis of this IQ interaction will be given in Chapter 5.

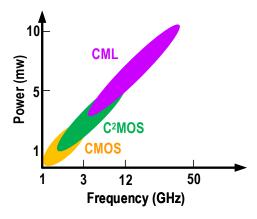

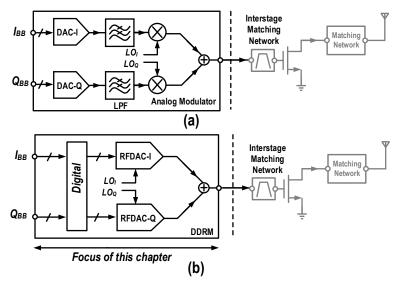

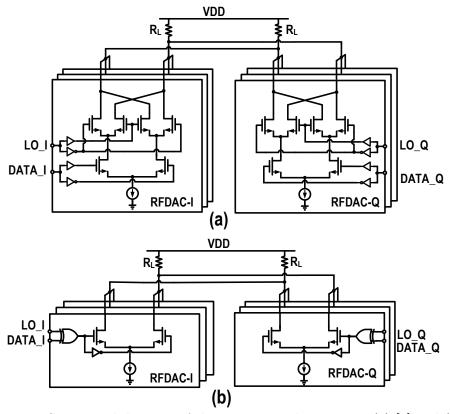

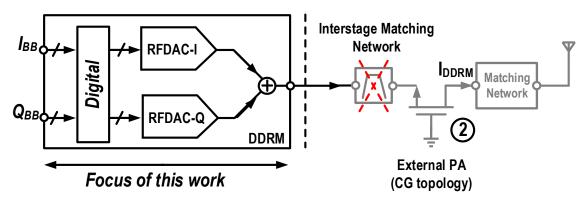

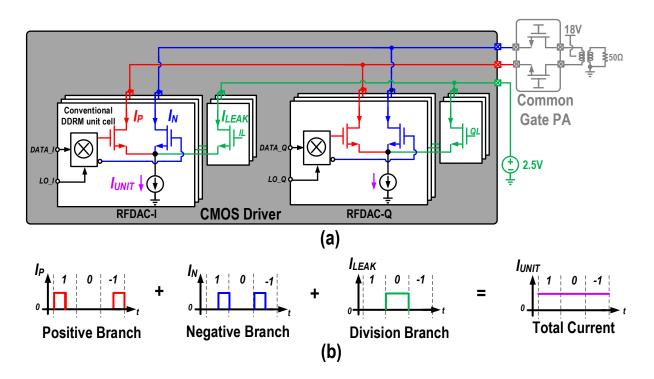

## 2.4.3 Direct-Digital RF Modulator

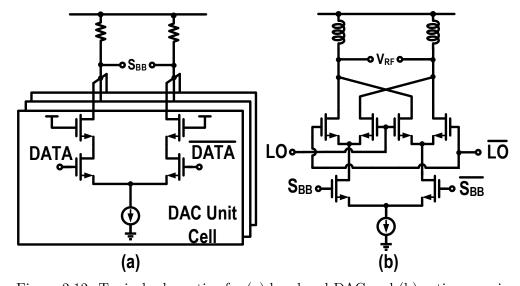

DPA-based Cartesian DTXs are typically centered around a PA-stage design and then extended to other building blocks, including the mixer. This places emphasis on the efficiency at the cost of linearity. The design can be centered more towards the modulator, with the focus on obtaining superior linearity with a less emphasis on efficiency. There is common ground between DPA-based Cartesian DTXs and DDRMs since both of them employ a "digitized" version of the conventional Cartesian architecture. In view of this, Fig. 2.12 shows typical designs of a baseband DAC and a active up-converter for a single channel (I or Q). The baseband DAC usually employs a current-steering topology, which is well-known for its superior linearity. The up-converter topology in Fig. 2.12(b) is essentially a Gilbert cell to improve linearity and noise performance. Usually, in an analog up-converter line-up, there is an LPF between the DAC and mixer to filter out the sampling spectral replicas.

To implement the RF modulator in a more straightforward and digital-intensive way, the baseband DAC and up-converter can be merged together. Such "direct" circuits are called DDRMs, which were first introduced in [12] (Fig. 2.13). Note that the DDRM presented in [12] includes both the I- and Q-branch. The DDRM essentially is a current-steering RFDAC with a 1-bit digital

Figure 2.13: DDRM proposed in [12].

mixer inside each unit cell. By using a high sampling frequency with related data interpolation, the sampling spectral replicas can be pushed far away, and the LPFs can be avoided.

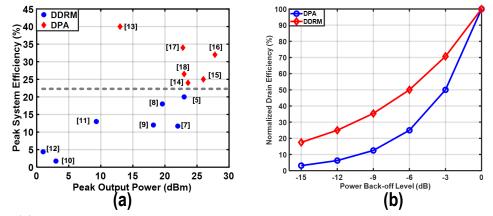

Due to the use of the current-steering topology, the system efficiency of a DDRM is not optimized. For example, in [12], the DDRM generates a WCDMA signal with an average power of -10 dBm which consumes 73 mW of DC power, yielding an overall efficiency of 0.14 %. A more extensive theoretical comparison between the DPA-based Cartesian DTXs and DDRMs will be presented in Chapter 5.

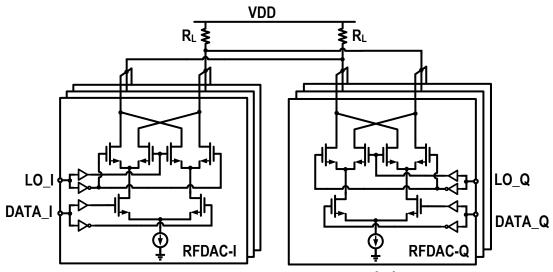

## 2.5 Efficiency Enhancement Techniques

In modern communication systems, due to the use of high-order modulation schemes, the output power of a modulated TX signal when equals to its peak power is only a small fraction of the time. Consequently, it is more effective to consider the average efficiency instead of the peak efficiency. This average efficiency depends both on the amplitude distribution of the modulated TX signal, as well as the TX efficiency in PBO. The amplitude distribution of a modulated signal can be represented by its probability distribution function (PDF). To put this a bit more in perspective, the PDFs of an LTE and a WLAN signal are shown in Fig. 2.14 ([13]), together with the ideal class-AB PA efficiency curve as a function of the PBO level. As can be observed, the average output power of PAs for WLAN and LTE signals is, respectively, about 6 dB and 13 dB less than the peak output power. However, to remain linear, the PA is not allowed to clip the signal. Therefore, as can be concluded from Fig. 2.14, the average drain efficiency of the class-AB PA for these signals is close to only 37 % and 24 % of the peak drain efficiency, respectively.

To mitigate this waste of supply energy, different efficiency enhancement techniques have been proposed over time. The most popular efficiency enhancement techniques can be categorized into two main groups: supply modulation and load modulation. In Section 2.3, the analog supply modulation techniques such as EER and ET have already been briefly discussed. In this section, we introduce

Figure 2.14: Efficiency of a class-AB PA and the PDFs of a LTE signal and a WLAN signal vs. PBO level. [13]

an open-loop supply switching technique, namely: class-G PA operation (also called the dual supply modulator). Next, two popular load modulation techniques are discussed, namely the Doherty and outphasing techniques.

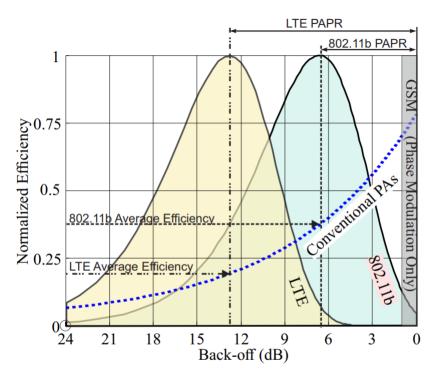

## 2.5.1 Supply Switching: Class-G Operation

As discussed above, the supply modulator often fails to track the amplitude of large bandwidth signals, so a more straightforward, simpler approach is to use a few discrete power supplies (often two supplies) and switch the levels using switches (class-G), which was first introduced in [14]. A conceptual diagram is shown in Fig. 2.15(a). There are two supplies in the system. When the signal is below the 6 dB PBO region; the supply voltage is set to VDD/2, and when the signal is beyond 6 dB PBO, the supply voltage is set to VDD. The efficiency versus the normalized output voltage is shown in Fig. 2.15(b) ([14]). As can be noted, the efficiency below the 6 dB PBO region is enhanced and along with the average efficiency.

In a practical PA design, however, there is usually an RF choke in the supply feed. Therefore, when the supply is switched, there will be a glitch, both in current and in the supply voltage provided. As a result, most class-G implementations use supply voltage switching for average power tracking (APT). Recently, several researchers ([15] and [16]) have employed this concept in supply modulation by dynamically switching the power supply and tracking the envelope of the signal, thus achieving efficiency enhancement similar to that with ET in modulated signals. However, the increased distortion due to the glitch prevents it from achieving a large bandwidth with good signal

Figure 2.15: (a) Top-level topology of the class-G PA; (b) Drain and average efficiency comparisons for a PA with dual supply versus a class-AB PA. [14]

Figure 2.16: (a) Basic Doherty PA; (b) equivalent schematic of the Doherty PA. quality.

## 2.5.2 Doherty Power Amplifiers

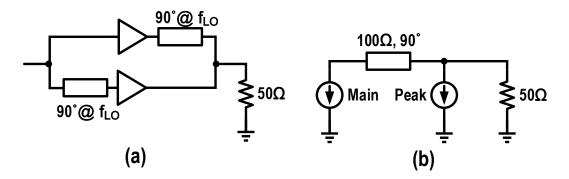

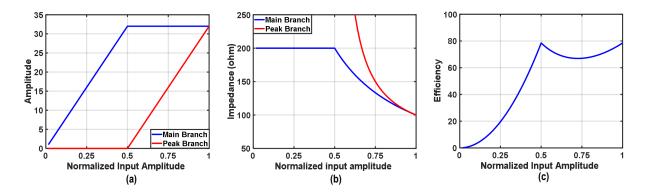

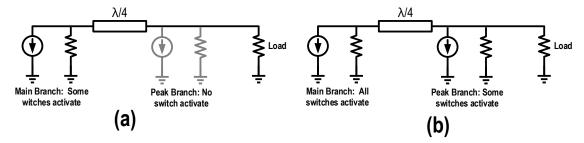

The Doherty PA topology achieves enhanced PBO efficiency by using active load modulation ([17]). Since it can potentially support a large modulation bandwidth without extra computations for the input signals, it has been widely employed in base stations. With the Doherty PA, only low-complexity hardware is needed to support a large modulation bandwidth. Its simplicity and good performance make it a popular choice for base station applications. The basic Doherty PA topology is shown in Fig. 2.16(a), and its equivalent circuit topology is shown in Fig. 2.16(b). It is composed of two branches, namely a main and peak branch, and a  $\lambda/4$  transmission-line-based impedance inverter that acts as a Doherty output power combiner. The Doherty operation itself relies on the predefined interaction between the two PA paths. To obtain this desired interaction for analog implementations, the main PA is biased in class-AB operation, while the peak PA is biased in class-C operation.

When the output signal is below 6 dB PBO ( $V_{\text{out}}$  is smaller than  $V_{\text{out,peak}}/2$ ), only the main PA is active (Fig. 2.17), while the peak PA remains off. In this mode, the impedance seen from the

Figure 2.17: Load impedance (a) and voltage swing (b) of the main PA and peak PA of a Doherty PA; and (c) efficiency curve vs. PBO level.

main PA is constant and is given by the impedance inverter action on  $R_L$  yielding:

$$Z_{\text{main}} = \frac{Z_o^2}{Z_L} \tag{2.11}$$

When the signal is between the -6 dB and 0 dB PBO regions ( $V_{\text{out}}$  is between  $V_{\text{out,peak}}/2$  and  $V_{\text{out,peak}}$ ), the peak PA is activated, and the load impedance seen by the main PA becomes:

$$Z_{\text{main}} = \frac{Z_o^2}{\frac{I_{\text{main}} + I_{\text{peak}}}{I_{\text{main}}} Z_L}$$

(2.12)

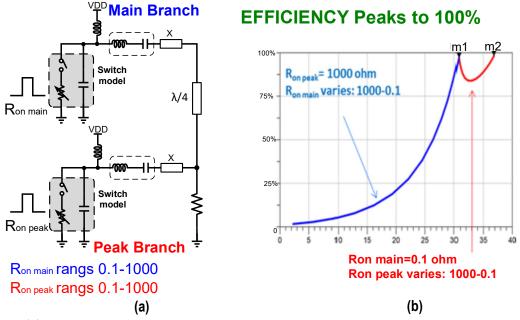

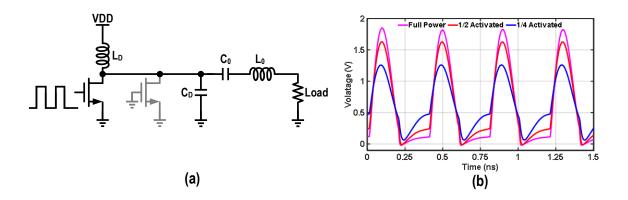

where  $Z_o$  is the characteristic impedance of the transmission line,  $I_{\text{main}}$  and  $I_{\text{peak}}$  are the currents of the main and peak branches, respectively, and  $Z_L$  is load impedance. Note that due to the peak PA activation at 6 dB PBO and the impedance inversion, the impedance for the main is lowered with an increasing  $I_{\text{peak}}$ . This frees the main amplifier from the signal clipping, while its output voltage swing is kept close to the supply voltage (Fig. 2.17(a)). As a result, the maximum drain efficiency is achieved for the main PA. The peak PA will only reach its maximum output voltage swing and efficiency at full output power. Figure 2.17(c) provides the resulting efficiency of the overall Doherty PA versus PBO level, and as such, shows the well-known Doherty efficiency enhancement in PBO region. Doherty operation can also be achieved using energy-efficient RFDACs for the main and peak PA implementation, offering new opportunities to achieve higher TX system integration and performance. We will discuss such an implementation in Chapter 3.

## 2.5.3 Outphasing Power Amplifiers

Implementing an outphasing TX is another well-known technique to obtain efficiency enhancement in the PBO region. In such a TX, to create the output signal, two (saturated) branch PAs are used which produce two equal constant envelope signals that are vector-summed in an output power combiner. The output amplitude of this combiner depends on the relative phase difference between the signals in the two branches. The use of saturated or switch-mode branch amplifiers enhances the TX peak efficiency, which can theoretically reach 100 %. The efficiency in PBO

operation, however, is highly dependent on the type of output power-combiner used. For example, if an isolating power combiner is used, e.g., a Wilkinson power combiner, the effective loading of the branch PAs remains constant and equal to its  $R_{\rm opt}$  for maximum output power. Consequently, no PBO efficiency enhancement takes place, and all excess RF power generated by the branch PAs will be absorbed by the isolation resistor in the Wilkinson combiner. When using a non-isolating power combiner, e.g., a Chireix combiner, loading of the branch amplifiers become dynamically modulated with the outphasing angle, allowing the PBO efficiency enhancement to be achieved. However, this Chireix combiner is inherently narrowband as it relies on "matched" positive and negative reactance compensation for the PA branches. This limits its use in narrowband applications. Outphasing TXs can be implemented for both analog and digital-intensive implementation. Digital-intensive implementation will have a better performance potential than that of analog counterparts. However, the computational overhead can be considerable. Specifically, the number of adders required for outphasing signal decomposition is always much larger than required for a conventional CORDIC in a polar line-up. Especially when targeting low or moderate TX output power, the high computational power can dramatically degrade the overall TX line-up efficiency.

## 2.6 Conclusion

This chapter gives the efficiency and bandwidth considerations of wireless TX architectures. First, linear class-A and class-(A)B operation with related efficiency versus PBO are discussed. Next, conventional analog TX line-up architectures are explained, namely polar and analog Cartesian approaches, and are evaluated in terms of modulation bandwidth. With this established, the next step is taken toward designing their (new) digital-intensive polar and Cartesian counterparts. These new concepts provide a promising path to higher integration while opening up new opportunities to dramatically improve the performance of wireless systems. Two classes of DTXs are identified. The first is the DPA topology, which is mostly focused on achieving high-efficiency through switch-mode PA. The second is the DDRM approach, which favors the use of current-steering-oriented architectures to achieve superior linearity. In conclusion, this chapter explains the need to boost the efficiency in PBO, and for this purpose describes briefly the most popular efficiency enhancement techniques to do so. Building on this foundation of wireless systems, we are ready to enter the field of advanced DTXs.

## References

- [1] E. McCune, "Operating Modes of Dynamic Power Supply Transmitter Amplifiers," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 62, no. 11, pp. 2511-2517, Nov. 2014.

- [2] V. Pinon et al., "A Single-Chip WCDMA Envelope Reconstruction LDMOS PA with 130MHz Switched-Mode Power Supply," 2008 IEEE International Solid-State Circuits Conference - Digest of Technical Papers, San Francisco, CA, 2008, pp. 564-636

2.6 References 25

[3] J. Jeong *et al.*, "Wideband Envelope Tracking Power Amplifiers With Reduced Bandwidth Power Supply Waveforms and Adaptive Digital Predistortion Techniques," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 12, pp. 3307-3314, Dec. 2009.

- [4] D. Chowdhury et al., "2.2 A fully integrated reconfigurable wideband envelope-tracking SoC for high-bandwidth WLAN applications in a 28nm CMOS technology," 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2017, pp. 34-35.

- [5] L. Ye et al., "Design Considerations for a Direct Digitally Modulated WLAN Transmitter With Integrated Phase Path and Dynamic Impedance Modulation," in *IEEE Journal of Solid-State Circuits*, vol. 48, no. 12, pp. 3160-3177, Dec. 2013.

- [6] S. Zheng et al., "A WCDMA/WLAN Digital Polar Transmitter With Low-Noise ADPLL, Wideband PM/AM Modulator, and Linearized PA," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 7, pp. 1645-1656, July 2015.

- [7] S. Cripps "RF Power Amplifiers for Wireless Communications" Artech House Publishers.

- [8] D. Mul et al., "Efficiency and Linearity of Digital "Class-C Like" Transmitters" 2020 50th European Microwave Conference (EuMC), Utrecht, the Netherlands, 2020, pp. 1-4.

- [9] M. S. Alavi et al., "All-Digital RF I/Q Modulator," in IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 11, pp. 3513-3526, Nov. 2012.

- [10] M. S. Alavi et al., "A Wideband 2× 13-bit All-Digital I/Q RF-DAC," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 62, no. 4, pp. 732-752, April 2014.

- [11] Z. Deng et al., "9.5 A dual-band digital-WiFi 802.11a/b/g/n transmitter SoC with digital I/Q combining and diamond profile mapping for compact die area and improved efficiency in 40nm CMOS," 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2016, pp. 172-173.

- [12] P. Eloranta et al., "Direct-digital RF modulator IC in 0.13 /spl um CMOS for wide-band multiradio applications," ISSCC. 2005 IEEE International Digest of Technical Papers. Solid-State Circuits, 2005., San Francisco, CA, 2005.

- [13] C. Ramella *et al.*, "High Efficiency Power Amplifiers for Modern Mobile Communications: The Load-Modulation Approach", *Electronics* 2017, 6, 96.

- [14] J. S. Walling *et al.*, "A Class-G Supply Modulator and Class-E PA in 130 nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 44, no. 9, pp. 2339-2347, Sept. 2009.

- [15] S. Hu et al., "A Broadband Mixed-Signal CMOS Power Amplifier With a Hybrid Class-G Doherty Efficiency Enhancement Technique," in *IEEE Journal of Solid-State Circuits*, vol. 51, no. 3, pp. 598-613, March 2016.

- [16] V. Vorapipat et al., "A Class-G Voltage-Mode Doherty Power Amplifier," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3348-3360, Dec. 2017.

- [17] F. H. Raab *et al.*, "Power amplifiers and transmitters for RF and microwave," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 50, no. 3, pp. 814-826, March 2002.

## CHAPTER

# 3

## Fully Integrated Digital-Intensive Polar Doherty Transmitter

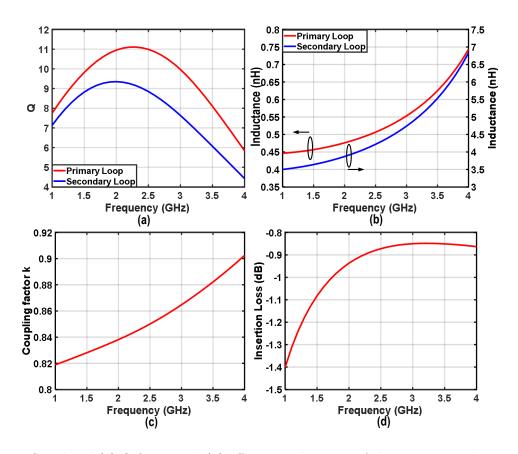

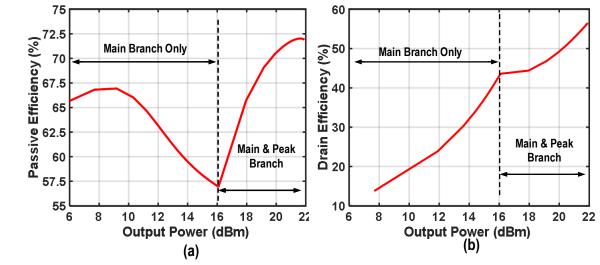

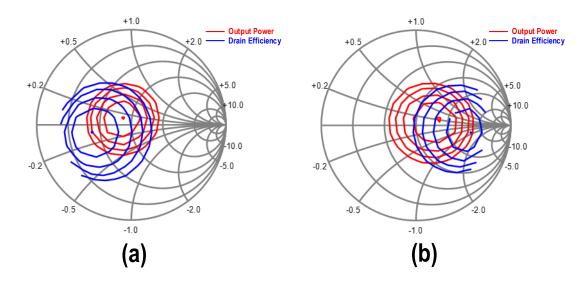

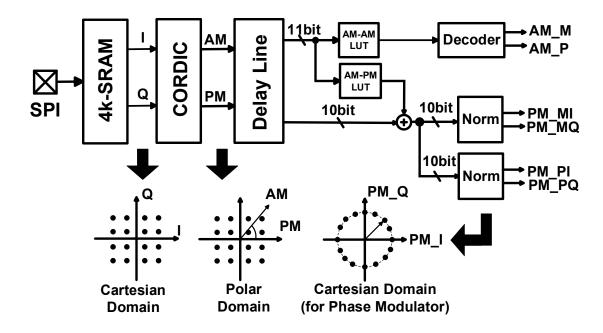

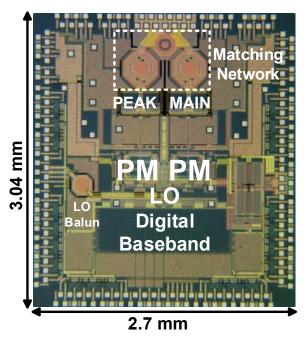

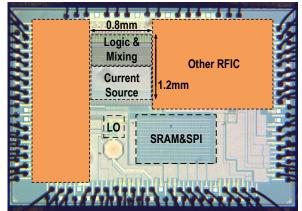

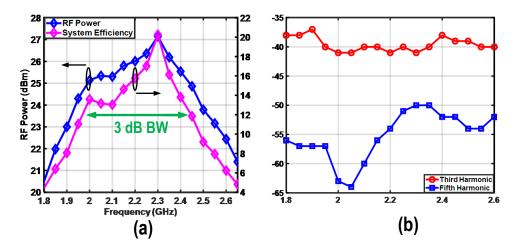

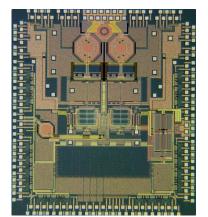

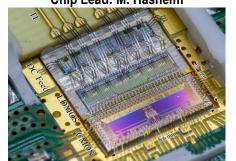

This chapter presents the design, realization, and verification of the world's first fully-integrated bits-in-RF-out digital polar Doherty TX. It has been implemented in a 40 nm bulk CMOS technology and operates from 2.3-2.8 GHz. The proposed architecture comprises CORDIC, digital delay aligners, DPD correction circuitry, and frequency-agile wideband phase modulators. The latter drives the polar main and peak PA switching banks that operate in quasi-load insensitive (QLI) class-E PAs [1]. The output powers are combined by an on-chip transformer-based Doherty power combiner. At 2.5 GHz, its maximum output power reaches +21.4 dBm, while its drain efficiency is 49.4 % at peak power and 33.7 % in the 6-dB PBO region. After applying DPD for a 40 MHz 64-QAM signal, the measured EVM is better than -31 dB, with an ACLR better than -40 dBc at an average drain efficiency of 25 %.

This chapter is organized as follows. Section 3.1 introduces the concept of the polar DTX with its benefits and challenges, and it also presents the research targets of this work. Section 3.2 deduces the segmented QLI class-E PA model and presents the analysis for estimating the ACW-AM and ACW-PM curve of the Doherty DPA. Following that, the overall system architecture is discussed in Section 3.3. Section 3.4 provides the Doherty DPA circuit implementation, while Section 3.5 and Section 3.6 discuss the baseband and LO generation, respectively. Section 3.7 briefly discusses the DPD algorithm used in the measurements. Experimental results are shown in Section 3.8, while Section 3.9 concludes the chapter.

Figure 3.1: Conceptual block diagram of a polar DTX.

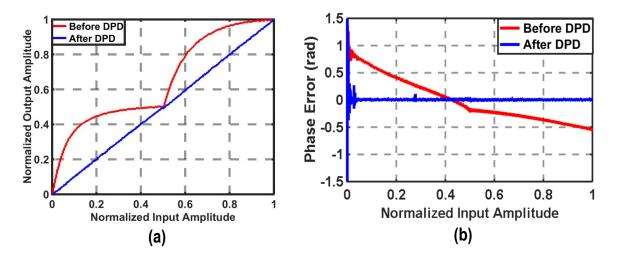

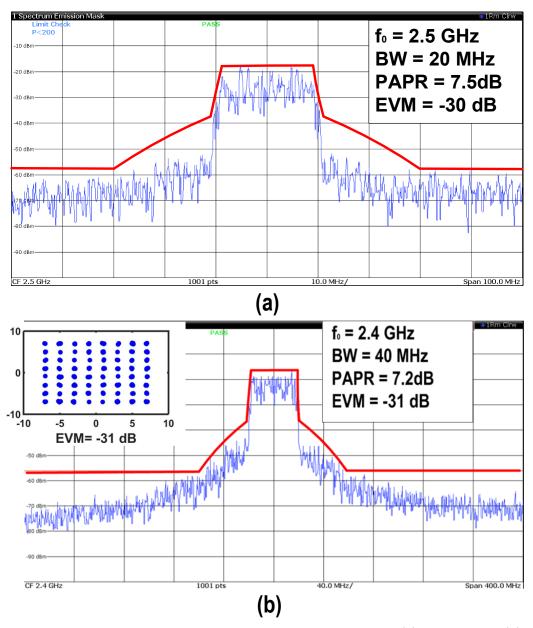

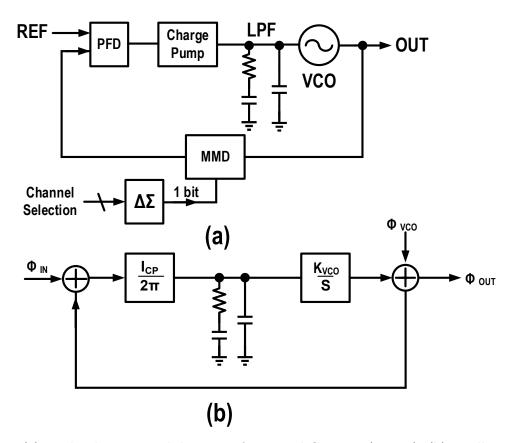

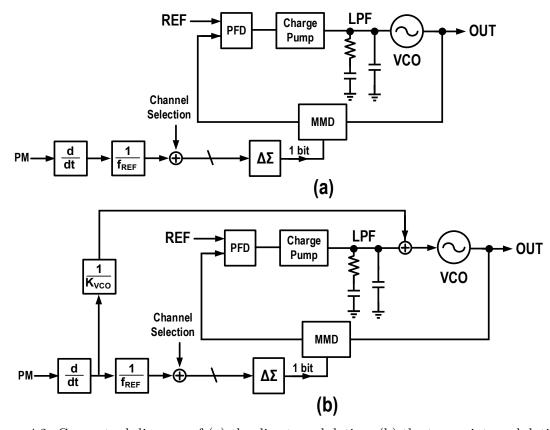

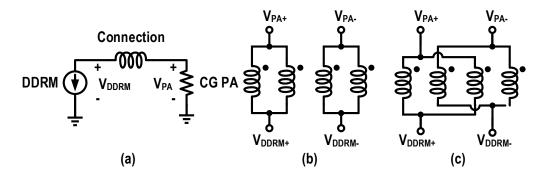

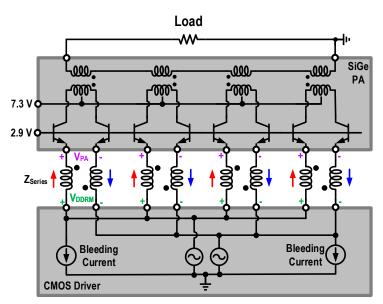

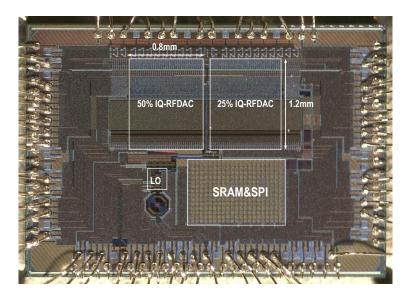

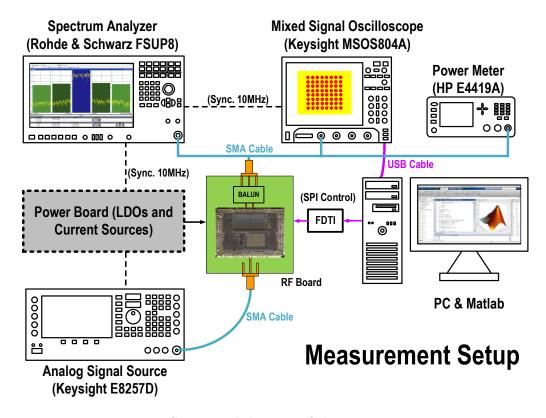

## 3.1 Introduction