# A 2.5-µW Beyond-the-Rails Current Sensor With a Tunable Voltage Reference and ±0.6% Gain Error From -40 °C to +85 °C

Zamparette, Roger; Makinwa, Kofi

DOI

10.1109/LSSC.2022.3219214

Publication date

**Document Version** Final published version

Published in

IEEE Solid-State Circuits Letters

Citation (APA)

Zamparette, R., & Makinwa, K. (2022). A 2.5-μW Beyond-the-Rails Current Sensor With a Tunable Voltage Reference and ±0.6% Gain Error From -40 °C to +85 °C. IEEE Solid-State Circuits Letters, 5, 264 - 267. https://doi.org/10.1109/LSSC.2022.3219214

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 2.5- $\mu$ W Beyond-the-Rails Current Sensor With a Tunable Voltage Reference and $\pm 0.6\%$ Gain Error From -40 °C to +85 °C

Roger Zamparette<sup>®</sup>, *Member, IEEE*, and Kofi Makinwa<sup>®</sup>, *Fellow, IEEE*

Abstract—This letter presents a low-power, fully integrated current sensor for Coulomb-counting. It employs a hybrid delta–sigma modulator  $(\Delta \Sigma M)$  with an FIR-DAC to digitize the voltage drop across a shunt. The modulator's first stage consists of a capacitively coupled chopper amplifier, which enables a beyond-the-rails  $(-0.3\ to\ 5\ V)$  input common-mode voltage range from a 1.8-V supply. A tunable voltage reference is used to accurately compensate for the large temperature coefficient  $(\sim\!3500\ ppm/^\circ C)$  of low-cost metal shunts. With a 20-m $\Omega$  on-chip shunt,  $\pm 2\ A$  currents can be digitized with 0.35% gain error from  $-40\ ^\circ C$  to 85 °C, after a 1-point trim. With a 3-m $\Omega$  PCB trace, currents up to  $\pm 15\ A$  can be digitized with 0.6% gain error over the same temperature range. Fabricated in a standard 0.18- $\mu m$  CMOS process, the sensor occupies 1.6 mm $^2$  and consumes 2.5  $\mu W$ , which is 3x less than the state of the art. It also achieves competitive energy efficiency, with a figure of merit (FoM) of 149 dB.

Index Terms—Coulomb-counting, current sensor, FIR-DAC, fully integrated, high-side, hybrid delta-sigma modulator, on-chip shunt resistor, PCB trace shunt resistor.

### I. INTRODUCTION

Coulomb-counting is a well-known technique for estimating battery state of charge (SOC). It involves measuring and integrating battery current to determine the net influx of charge. Shunt-based current sensors are often used to achieve the required accuracy and dynamic range [1], [3], [5]. These should be configured for high-side sensing to avoid adding extra resistance between the battery and the system ground. However, this requires instrumentation amplifiers or ADCs with a wide input common-mode range (ICMR), ~5 V, for the lithium batteries employed in IoT and wearable devices. Low *instantaneous* power consumption is another key requirement in such applications since Coulomb-counting current sensors are always on. Minimizing their power consumption is a major target of this letter.

Accurate current sensors often employ precision off-chip shunts. To reduce cost, metal shunts made from CMOS interconnect [3], lead-frame metal [4], or PCB traces [5] can also be used. However, they have two main disadvantages. First, their nominal resistance may spread significantly ( $\pm 30\%$ ). Second, their large temperature coefficients (TCs  $\sim 3500$  ppm/°C) result in significant resistance variations over temperature. Although their nominal spread can be trimmed, their large TCs require the use of temperature compensation schemes.

In [4], an on-chip temperature sensor is used to sense and digitize shunt temperature. This information is then used to correct the current sensor output digitally. Although it achieves a gain error of 0.3% over the industrial temperature range (–40 °C to +85 °C), it requires a complex trimming scheme and consumes 20  $\mu W$ .

Manuscript received 20 June 2022; revised 17 August 2022 and 8 October 2022; accepted 23 October 2022. Date of publication 3 November 2022; date of current version 22 November 2022. This work was supported in part by the Semiconductor Research Corporation. This article was approved by Associate Editor Joseph Shor. (Corresponding author: Roger Zamparette.)

The authors are with the Microelectronics Department, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: r.l.britozamparette@tudelft.nl).

Digital Object Identifier 10.1109/LSSC.2022.3219214

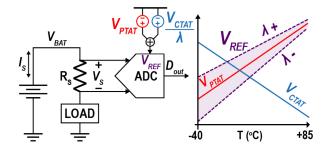

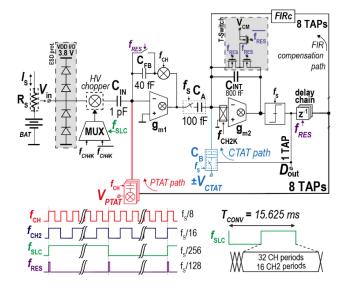

Fig. 1. Block diagram of the proposed current sensor.

In [3], rather than directly measuring the shunt temperature, the TC of a metal shunt is compensated by applying a proportional-to-absolute-temperature (PTAT) voltage reference to the current sensor's ADC. However, it consumes 25  $\mu$ W and only achieves a gain error of 0.9% with an on-chip metal shunt. Furthermore, accurately correcting a PCB trace's slightly different TC still requires using a (relaxed) temperature sensor [5].

However, the current consumption of the aforementioned sensors is still too high for IoT and wearable applications. In [6], a Coulomb-counter that consumes less than 8.5  $\mu$ W is presented, but it relies on a precision off-chip shunt to achieve good accuracy over temperature. A recent work [7] presents a current sensor with a TC-tunable voltage reference, making it suitable for different types of shunts, but its 0.5-mW power consumption is too high.

This letter, an extended version of [8], presents a high-side current sensor that achieves low power consumption and high accuracy with low-cost metal shunts. This is achieved by combining an energy-efficient hybrid  $\Delta\Sigma$  modulator with a TC-tunable voltage reference. This approach obviates the need for an extra temperature sensor and a complex digital back-end. It consumes only 2.5  $\mu$ W, representing a 3× improvement on the state of the art while achieving competitive gain error (<0.6%) and energy efficiency figure of merit (FoM) (149 dB).

#### II. TEMPERATURE COMPENSATION

The proposed TC-tunable voltage reference ( $V_{REF}$ ) is realized by adding a PTAT voltage ( $V_{PTAT}$ ) to a complementary-to-absolute-temperature (CTAT) voltage ( $V_{CTAT}$ ) scaled by an appropriate factor ( $\pm\lambda$ ), thus allowing a low gain error to be achieved for a broad range of shunts. The block diagram of the resulting current sensor is shown in Fig. 1, where the TC-tunable  $V_{REF}$  is given by

$$V_{\text{REF}} = V_{\text{PTAT}} \pm \frac{V_{\text{CTAT}}}{\lambda}$$

(1)

and  $V_S$  is the voltage drop across the shunt. The  $\lambda$  factor can then be tuned to match the TCs of different types of low-cost metal shunts.

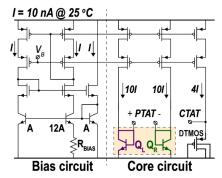

Fig. 2 depicts the circuit that generates  $V_{\rm PTAT}$  and  $V_{\rm CTAT}$ . A differential  $V_{\rm PTAT}$  ( $\Delta V_{\rm BE}$ ) is generated by two NPNs with different current densities. An NPN-based bias circuit generates a well-defined PTAT current I (10 nA @ 25 °C), which is then used to bias the core circuit that generates  $V_{\rm PTAT}$  and  $V_{\rm CTAT}$ . Compared to using a PNP-based bias circuit, this obviates the need for an extra opamp to force  $\Delta V_{\rm BE}$

2573-9603 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 2.  $V_{REF}$  generation.

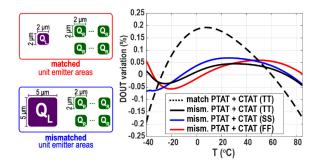

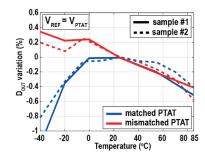

Fig. 3. Effect of the nonlinear PTAT on the  $D_{\rm OUT}$  variation of the on-chip shunt for different process corners.

across  $R_{\rm BIAS}$ , thus reducing power consumption. Also, in the chosen 180-nm process, NPNs have a larger current gain, which reduces base-current-related biasing errors.

However, if  $V_{\rm CTAT}/\lambda$  (typically <1 mV) is derived from the base-emitter voltage of a BJT ( $V_{\rm BE}\sim$ 650 mV @ 25 °C),  $\lambda$  may have to be quite large (>1000) to achieve the target TC. To relax this, a dynamic threshold-voltage MOS transistor (DTMOST) based on a low-threshold device is used to generate a smaller  $V_{\rm CTAT}(V_{\rm SG}\sim$ 65 mV @ 25 °C). As a result,  $\lambda$  can be significantly reduced.

In addition to the mismatch between the shunt's first-order TC (TC1) and  $V_{\rm REF}$ , the shunt's second-order TC (TC2) will also limit the achievable gain error. In this letter, the on-chip shunt, similar to the one used in [3], has an expected TC2 of  $\sim -1$  ppm/K². To mitigate this, a systematic nonlinearity can be introduced in  $V_{\rm PTAT}$  by using NPNs with mismatched unit emitter areas, as shown in Figs. 2 and 3. This mismatch leads to different base resistances, resulting in a small second-order nonlinearity. As shown in Fig. 3, this significantly reduces the variation of  $D_{\rm OUT}$  (=  $V_S/V_{\rm REF}$ ) over temperature. For comparison purposes, two  $V_{\rm PTAT}$  cores were designed, one with matched NPN emitter areas and one with mismatched areas.

# III. READOUT CIRCUITRY

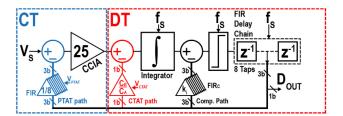

The block diagram of the readout is shown in Fig. 4. It is built around a first-order  $\Delta\Sigma M$  with an 8-tap FIR-DAC. This has a uniform impulse response, which facilitates accurate Coulomb-counting even with dynamic currents. The use of an FIR-DAC reduces the swing at the virtual ground of the loop filter and thus enables the use of a continuous-time (CT) gain stage (25 V/V) before the discrete-time (DT) integrator. This reduces the input-referred kT/C noise of the DT integrator and thus increases energy efficiency. The PTAT portion of  $V_{\rm REF}$  is fed back through an equally weighted (1/8) 8-tap FIR-DAC via the first stage, while the CTAT portion of  $V_{\rm REF}$  is fed back through the first tap of the FIR-DAC via the DT integrator. The gain of the first stage is thus part of the large  $\lambda$ .

To avoid instability due to the extra delay introduced by the FIR-DAC, a compensation FIR-DAC is connected to the output of the first stage. The  $k_i$  coefficients [0, 0.87, 0.75, 0.62, 0.5, 0.37, 0.25, 0.12] are

Fig. 4. Block diagram of the current sensor.

Fig. 5. Single-ended representation of the readout circuit.

chosen to make the sampled impulse response of the resulting loop filter the same as that of an integrator driven by a 1-bit DAC [10].

A single-ended representation of the proposed fully differential current sensor is shown in Fig. 5. Its input stage consists of a capacitively coupled instrumentation amplifier (CCIA) [11], which efficiently amplifies the voltage drop across the shunt resistor  $V_S$ , inherently suppressing offset and 1/f noise, while also isolating its virtual ground voltage from the battery's voltage.

Thanks to the FIR-DAC, the error swing at the CCIA input is reduced by  $6\times$  to around  $\sim$ 20 mV. The CCIA can then be realized as an energy-efficient single-stage current-reuse OTA  $g_{m1}$  (400 nA) with a closed-loop gain of 25 V/V (=  $C_{FB}/C_{IN}$ ).

The CCIA is followed by a chopped switched-capacitor (SC) integrator built around  $g_{m2}$ , also implemented by another current-reused OTA (200 nA). It serves as a summing node for the tunable  $\pm V_{\rm CTAT}/\lambda$  feedback signal, as well as the output of a second 8-tap FIR-DAC that compensates for the extra delay caused by the feedback FIR-DAC. The  $\lambda$  factor is then defined by

$$\lambda = A_{\text{CCIA}} \cdot \frac{C_A}{C_R}.$$

(2)

Since  $A_{CCIA} = 25$  V/V, this approach results in a reasonable ratio between the capacitors  $C_A$  and  $C_B$ , where  $C_A$  is the sampling capacitor of the integrator and  $C_B$  is the feedback CDAC of the CTAT path. To tune  $\lambda$ ,  $C_A$  (60–140 fF) and  $C_B$  (5–25 fF) are 5-bit and 3-bit trimmable capacitors, respectively. An extra bit is responsible for controlling the polarity of the  $\lambda$ . This strategy allows the TC of  $V_{REF}$  to be tuned from 3000 to 4000 ppm/°C. This trimming range allows the  $\lambda$  factor to handle different low-cost shunt resistors and to reduce the resulting first-order gain error to less than 0.1%.

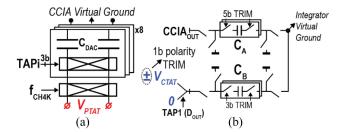

Fig. 6(a) shows the FIR-DAC. It consists of eight sets of two capacitors connected to the virtual ground of the CCIA. The  $V_{\text{PTAT}}$  is then injected through switches connected to the eight different terminals generated by the delay chain (Fig. 5). The  $V_{\text{CTAT}}$  voltage is injected

Fig. 6. (a) FIR-DAC injecting  $V_{\rm PTAT}$  into the virtual ground of the CCIA. (b) Single-ended representation of the SC DAC injecting  $V_{\rm CTAT}$  into the virtual ground of the integrator.

into the loop through an SC DAC, where a single-ended representation is shown in Fig. 6(b). Depending on  $D_{\rm OUT}$  (the first tap of the delay chain),  $\pm V_{\rm CTAT}$  or 0 is feedback. The combination of both DACs generates the  $V_{\rm REF}$  described in (1).

To achieve low offset, both the CCIA and the integrator are chopped. The chopping frequency  $f_{CHOP}$  should be greater than the OTA's 1/f-noise corner, but as low as possible to reduce residual offset due to chopping artifacts. However, due to the CT front-end, the chopping frequency  $f_{CHOP}$  should be set to  $f_S/2$  or  $f_S$  to avoid quantization noise-folding, which happens at  $2f_{CHOP}$ . Conveniently, the equally weighted 8-tap FIR-DAC creates notches in the modulator's noise transfer function (NTF), which allows  $f_{CHOP}$  to be safely set to multiples of  $f_S/2$ Nt, where Nt is the number of taps [10]. The CCIA and the integrator are chopped in this design at  $f_{CH4K} = f_S/8$  and  $f_{CH2K} = f_S/16$ , respectively.

The modulator's residual offset is suppressed by system-level chopping (SLC). This is done by inverting the clock of the CCIA's input chopper [4] and refreshing the memory storage elements (integrator and flip-flops) at every reset phase. A timing diagram of this operation is shown in Fig. 5.

A problem related to the use of CCIAs is the output ripple generated by their offset [11]. As shown in Fig. 5, there is no dc feedback path for this offset, which means that it is amplified by the open-loop gain of  $g_{m1}$  and can potentially cause clipping. To deal with this issue, reset switches were added in parallel with the feedback capacitors. These switches close at every reset phase of the  $\Delta\Sigma M$  operation, when  $gm_1$  is also auto-zeroed by storing the offset at  $C_{IN}$ . Although switch leakage will cause the output ripple to increase slowly, this is limited to less than 100 mV  $_{pp}$  during a conversion time of 16 ms.

The input switches can handle an ICMR from -15 to 15 V. However, in practice, this is limited by ESD protection. In this design, two diodes were placed in series between the input terminals and the ESD supply rail, allowing the ICMR to be extended by approximately 1.4 V beyond the ESD supply rail. In the  $0.18-\mu m$  process used, the combination of series-connected ESD diodes and a 3.8-V I/O pad supply limits the CM voltage range to -0.3 to 5 V, which covers most single-cell battery applications.

The CCIA's gain suppresses the input-referred kT/C noise of the SC integrator, allowing for a small sampling capacitor (~100 fF). However, this low capacitor value and the low sampling frequency of this design impose a high off-impedance requirement for the integrator's reset switch; which would otherwise limit the integrator's dc gain and hence, the modulator's noise floor. To avoid this issue, the reset switch was implemented as a T switch (Fig. 5). This reduces switch leakage significantly, thus preserving the integrator's dc gain.

## IV. MEASUREMENT RESULTS

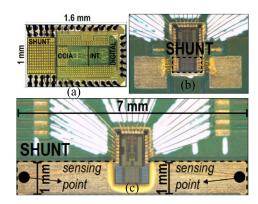

The current sensor prototype, shown in Fig. 7(a), was designed and fabricated in a standard 0.18- $\mu$ m CMOS process. It occupies 1.6 mm<sup>2</sup> and draws 1.4  $\mu$ A from a 1.8-V source, where the digital logic consumes 600 nA. At a sampling frequency of 32 kHz, the ADC has a 5.4  $\mu$ V of resolution at ~16-ms conversion time.

Fig. 7. Chip micrograph. (a) Die micrograph. (b) Die mounted for on-chip measurements. (c) Die mounted over a PCB trace shunt.

Fig. 8. DOUT variation for different kinds of shunt resistors.

For the on-chip shunt (20 m $\Omega$ ) measurements [Fig. 7(b)], four chips were mounted on a PCB. Ten bond wires (<1 mm) were connected to each terminal of the shunt to minimize their series resistance and self-heating, which could create a significant temperature gradient between the shunt and the temperature-sensing transistors. In the case of the PCB shunt (3 m $\Omega$ ) measurements [Fig. 7(c)] four chips were mounted directly onto the PCB trace with a thermally conductive (1 W/mK) and electrically isolating glue to improve thermal contact and maintain galvanic isolation. Similarly, a sample mounted on a lead-frame copper shunt (300  $\mu\Omega$ ) was also measured.

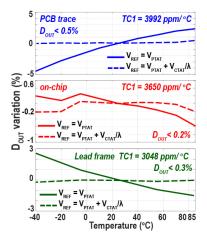

After a gain trim at 25 °C, the sensor was characterized from -40 °C to 85 °C. A fixed value of  $\lambda$  was used for each type of shunt. Fig. 8 shows the typical decimated output  $D_{\rm OUT}$  over temperature for an on-chip shunt, a PCB shunt, and a lead-frame shunt. To demonstrate the sensor's flexibility, results are shown for  $V_{\rm REF} = V_{\rm PTAT}$  and  $V_{\rm REF} = V_{\rm PTAT} + V_{\rm CTAT}/\lambda$ . For the PCB and lead-frame shunts, less than 0.5% of  $D_{\rm OUT}$  variation was measured. As shown in Fig. 8, this drops to less than 0.2% for the on-chip shunt, mainly due to the reduced  $D_{\rm OUT}$  curvature obtained with the mismatched NPN PTAT core, Fig. 9.

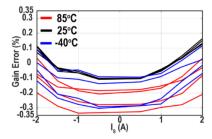

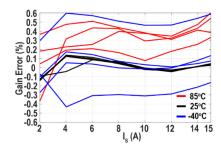

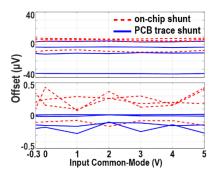

After a gain trim at 25 °C, multiple samples of the sensor were characterized with on-chip and PCB shunts. With  $\lambda = +500$ , the gain error of four on-chip shunt samples remained below 0.35% for currents up to  $\pm 2$  A from -40 °C to 85 °C (Fig. 10). With  $\lambda = -50$ , four PCB shunt samples were measured over a wider ( $\pm 15$  A) current range. An additional  $D_{\rm OUT}^2$  correction factor [3] was added to reduce caused by the combination of shunt self-heating and the finite thermal resistance between the PCB trace and the chip. The gain error then remains below 0.6% (Fig. 11). The offset with ( $\leq 500$  nV) and without SLC ( $\leq 40~\mu V$ ) are shown in Fig. 12 for CM input voltages ranging from -0.3 to 5 V.

Fig. 9. On-chip shunt  $D_{\text{OUT}}$  variation for the matched/mismatched cases.

Fig. 10. Gain error for the on-chip shunt.

Fig. 11. Gain error for the PCB trace shunt.

Fig. 12. Offset measurements.

Table I summarizes the sensor's performance and compares it to the state of the art. The proposed sensor requires  $3 \times$  less supply current and achieves competitive gain error with three types of shunts. Due to its beyond-the-rails ICMR (-0.3 to 5 V), the sensor can be used for battery monitoring in most single-cell battery applications.

# V. CONCLUSION

A flexible current sensor for low-power Coulomb-counting has been presented. An ADC with a TC-tunable  $V_{\rm REF}$  enables the accurate compensation of the TCs of various low-cost shunt resistors, resulting in gain errors <0.6% over the industrial temperature range. This approach does not require an explicit temperature sensor, resulting in significant power savings. Moreover, using a CCIA front-end combined with an 8-tap FIR-DAC enables an energy-efficient design while allowing a beyond-the-rails ICMR. The current sensor draws  $3\times$  less power (2.5  $\mu$ W) than the state of the art while maintaining

TABLE I

PERFORMANCE SUMMARY AND COMPARISON TABLE

|            | This Work   |        | Vroonhoven     | Xu          | Shalmany     |        | Z. Tang      |  |

|------------|-------------|--------|----------------|-------------|--------------|--------|--------------|--|

|            |             |        | ISSCC 20 [6]   | JSSC 18 [3] | JSSC 17 [4]  |        | ISSCC 22 [7] |  |

| PSUPPLY    | 2.5 uW      |        | < 9 µW         | 19.6 µW     | 19.5 µW      |        | 477 µW       |  |

| Gain Error | on-chip     | ±0.35% |                | ±0.9%       | on-chip      | ±0.3%§ |              |  |

|            | PCB trace   |        |                |             | lead-frame   | ±0.3%§ | ±0.25%       |  |

| RANGE      | on-chip     | ±2A    | ±1A            | ±4A         | on-chip      | ±5A    | ±25A         |  |

|            | PCB trace   | ±15A   |                |             | lead-frame   | ±36A   |              |  |

| Shunt      | on-chip     | 20 mΩ  | 50 mΩ <b>*</b> | 10 mΩ       | on-chip      | 10 mΩ  | 2 mΩ         |  |

|            | PCB trace   | 3 mΩ   |                |             | lead-frame   | 260 μΩ |              |  |

| Offset     | on-chip     | 25 µA  | < 100 µA       | 40 µA       | on-chip      | 4 µA   | 3 mA         |  |

|            | PCB trace   | 100 µA |                |             | lead-frame   | 400 µA |              |  |

| ICMR       | -0.3 to 5 V |        | 0 to 60 V      | 0 to 25 V   | low-side     |        | low-side     |  |

| VSUPPLY    | 1.8 V       |        | 1.7 to 60 V    | 1.5 to 2 V  | 1.3 to 1.7 V |        | 1.8 V        |  |

| TRANGE     | -40 to 85°C |        | -50 to 125°C   | -40 to 85°C | -40 to 85°C  |        | -40 to 85°C  |  |

| Resolution | 5.4 µVrms   |        | -              | 1.5 µVrms   | 2 µVrms      |        | 8.5 µVrms    |  |

| TCONV      | 16 ms       |        | -              | 2 ms        | 10 ms        |        | 0.1 ms       |  |

| FoM**      | 149 dB      |        | -              | 162 dB      | 155 dB       |        | 149 dB       |  |

| Tech.      | 0.18        |        | 0.18 BCD       | 0.18 BCD    | 0.13         |        | 0.18         |  |

<sup>\*</sup> Uses a custom/off-chip low-TCR shunt

a competitive energy efficiency FoM of 149 dB and beyond-the-rails ICMR of 5 V. These characteristics make it well suited for low-cost Coulomb-counting in single-cell battery-operated IoT/wearable applications.

#### ACKNOWLEDGMENT

The authors would like to thank Zuyao Chang's technical support.

#### REFERENCES

- "Impedance track<sup>TM</sup> technology battery gas gauge." Texas Instruments. Nov. 2021. [Online]. Available: https://www.ti.com/product/BQ27Z746

- [2] H. Jiang, S. Nihtianov, and K. A. A. Makinwa, "An energy-efficient 3.7-nV/ \$\surd\$ Hz bridge readout IC with a stable bridge offset compensation scheme," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 856–864, Mar. 2019.

- [3] L. Xu, J. H. Huijsing, and K. A. A. Makinwa, "A ±4-a high-side current sensor with 0.9% gain error from 40 °C to 85 °C using an analog temperature compensation technique," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3368–3376, Dec. 2018.

- [4] S. H. Shalmany, D. Draxelmayr, and K. A. A. Makinwa, "A ±36-a integrated current-sensing system with a 0.3% gain error and a 400-μA off-set from 55°C to +85°C," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 1034–1043, Apr. 2017.

- [5] L. Xu, S. H. Shalmany, J. H. Huijsing, and K. A. A. Makinwa, "A ± 12-a high-side current sensor with 25 V input CM range and 0.35% gain error from 40 °C to 85 °C," *IEEE Solid-State Circuits Letters*, vol. 1, no. 4, pp. 94–97, Apr. 2018.

- [6] C. van Vroonhoven, "A 0-to-60V-input VCM Coulomb counter with signal-dependent supply current and ±0.5% gain inaccuracy from 50°C to 125°C," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2020, pp. 348–350.

- [7] Z. Tang, R. Zamparette, Y. Furuta, T. Nezuka, and K. A. A. Makinwa, "A ±25-a versatile shunt-based current sensor with 10kHz bandwidth and ±0.25% gain error from -40°C to 85°C using 2-current calibration," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2022, pp. 66–68.

- [8] R. Zamparette and K. Makinwa, "A ±2A/15A current sensor with 1.4 μA supply current and ±0.35%/0.6% gain error from -40 to 85°C using an analog temperature-compensation scheme," in *Proc. Symp. VLSI Circuits*, 2021, pp. 1–2.

- [9] K. Souri, Y. Chae, F. Thus, and K. Makinwa, "12.7 A 0.85V 600nW all-CMOS temperature sensor with an inaccuracy of  $\pm 0.4^{\circ}$ C ( $3\sigma$ ) from -40 to 125°C," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, 2014, pp. 222–223.

- [10] R. Theertham, P. Koottala, S. Billa, and S. Pavan, "A 24mW chopped CTDSM achieving 103.5dB SNDR and 107.5dB DR in a 250kHz bandwidth," in *Proc. Symp. VLSI Circuits*, 2019, pp. C226–C227.

- [11] Q. Fan, F. Sebastiano, J. H. Huijsing, and K. A. A. Makinwa, "A 1.8 μ W 60 nV/ Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1534–1543, Jul. 2011.

<sup>\*\*</sup> FoM=Dynamic Range + 10log(Bandwidth/Power)

<sup>§</sup> Uses an extra ADC for temperature sensing allied to an extensive calibration.