#### Analysis and Design of Low-Power Receivers Exploiting Non-50 Ω Antenna Impedance and Phase-Only Quantization

Liu, Yao

10.4233/uuid:3cb7ded7-4308-4199-8afa-7027d2991076

**Publication date**

**Document Version** Final published version

Citation (APA)

Liu, Y. (2017). Analysis and Design of Low-Power Receivers: Exploiting Non-50 Ω Antenna Impedance and Phase-Only Quantization. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:3cb7ded7-4308-4199-8afa-7027d2991076

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

Analysis and Design of Low-Power Receivers: Exploiting Non-50  $\Omega$  Antenna Impedance and Phase-Only Quantization

Yao Liu

# Analysis and Design of Low-Power Receivers: Exploiting Non-50 $\Omega$ Antenna Impedance and Phase-Only Quantization

#### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.Ch.A.M. Luyben; voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 13 juni 2017 om 15:00 uur

door

Yao LIU

Master of Science in Electrical Engineering, Huazhong University of Science and Technology, China geboren te Jianli, Hubei, China This dissertation has been approved by the

promotor: Prof. dr. ir. W.A. Serdijn

#### Composition of the doctoral committee:

Rector Magnificus, Technische Universiteit Delft, chairman Prof.dr.ir. W.A. Serdijn, Technische Universiteit Delft, promotor

#### Independent members:

Prof.dr.ing. L.C.N. de Vreede, Technische Universiteit Delft Prof.dr. A. Demosthenous, University College London, UK

Prof.dr.ir. B. Nauta, Universiteit Twente

Prof.dr. ir. P. Baltus,

Technische Universiteit Eindhoven

Technische Universiteit Delft and RF

Communications Consulting

Prof.dr. P.J. French, Technische Universiteit Delft, reservelid

#### Copyright©2017 by Yao Liu

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

To my family

## Summary

Reducing the power consumption of low-power short-range receivers is of critical importance for biomedical and Internet-of-Things applications. Two interesting degrees of freedom (or properties) that have not been fully exploited in the pursuit of low power consumption are the antenna impedance and the phase-only modulation property of FSK/PSK signals. This dissertation explores the possibility of reducing the power consumption of the receiver by utilizing these two degrees of freedom.

The feasibility of using a non-50  $\Omega$  antenna impedance in an active receiver front-end is first studied. A general antenna-electronics interface analysis is carried out, suggesting that power transfer is not the only design objective in the interface, but that the impedances of antenna and load need to be optimized for either voltage or current, depending on which is more favorable to measure with the electronics. This principle has been applied to a co-design example of an inductive antenna impedance and a low-noise amplifier (LNA). A passive voltage gain can be achieved by using the proposed principle, and hence the noise figure (NF) can be reduced without sacrificing power consumption.

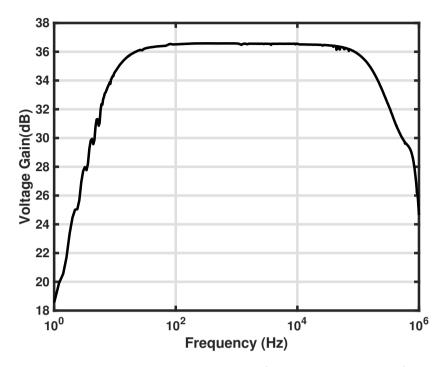

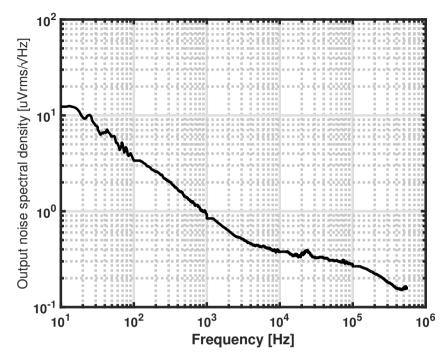

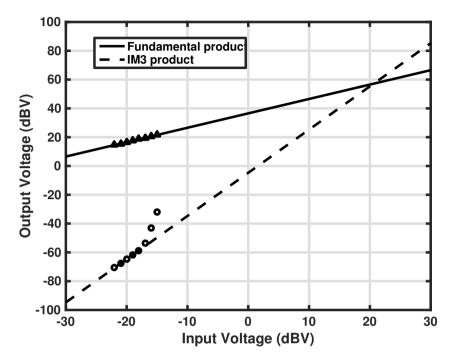

The concept of a non-50  $\Omega$  antenna impedance is also exploited in the context of passive front-ends (PFEs). An inductive antenna impedance proves beneficial for increasing the passive voltage gain of an antenna-LNA interface. The study of the PFE aims for the same voltage-boosting effect by incorporating the inductive antenna impedance in the PFE. An analysis reveals that the inductive antenna impedance introduces two extra degrees of freedom to increase the downconverted voltage of the front-end for a given antenna available power. In order to well maintain the passive voltage gain offered by the inductive antenna impedance together with its resonant load, the passive mixer should present a high-quality-factor capacitive input. This is achieved by incorporating an intermediate inductance in the passive network. The proposed front-end and a baseband LNA are implemented to verify the voltage-boosting effect. The implementation has a passive voltage gain of 11.6 dB, which is close to the state-of-the-art of 12 dB.

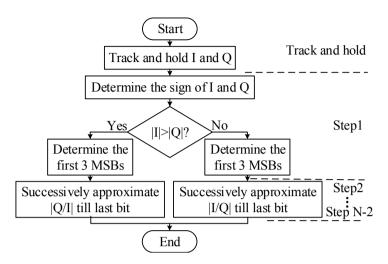

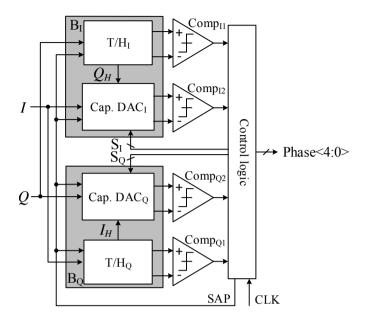

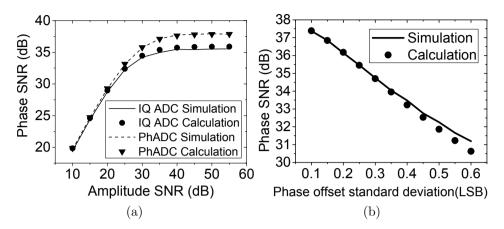

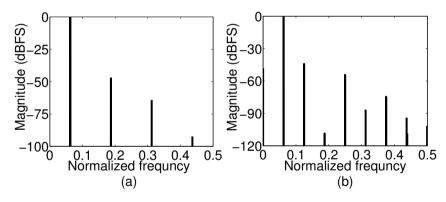

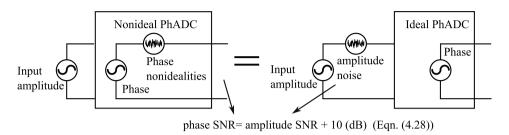

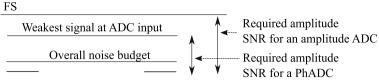

A promising concept which can fully utilize the phase-only modulation property of FSK/PSK signals is that of phase-domain analogto-digital converters (PhADCs). This dissertation also deals with the analysis and design of PhADCs. First of all, analytical methods are proposed to comprehensively compare the PhADC and an (in-phase and quadrature) IQ ADC. Phase signal-to-noise ratio (SNR) expressions of the two ADC types are formulated analytically to facilitate a quantitative comparison of the ADCs. In comparison with the IQ ADC, the PhADC, due to its embedded demodulation attribute, is a more compact quantization and demodulation solution when interference accommodation is not required. Moreover, considering a flash ADC as an example of the low resolution (3-4 bit) IQ ADC, the PhADC has a lower theoretical energy limit than the flash IQ ADC for a given phase effective number of bits (ENOB) due to the immunity to magnitude variations and the phase-only quantization, thereby showing the great room for energy efficiency improvement that the PhADC has. Second, having discussed the interesting attributes of the PhADC, an IQ-assisted conversion algorithm and a corresponding circuit topology to improve the energy efficiency of the PhADC are proposed. Thanks to the successive approximation (SAR)-like algorithm and charge-domain operation, the prototype achieves a FoM of 1.2 pJ/step, which is better than the state-of-the-art of 8.3 pJ/step. Finally, the explicit relationship between the input amplitude SNR and the output phase SNR of the PhADC has been formulated. This relationship facilitates the system analysis of a receiver using a PhADC.

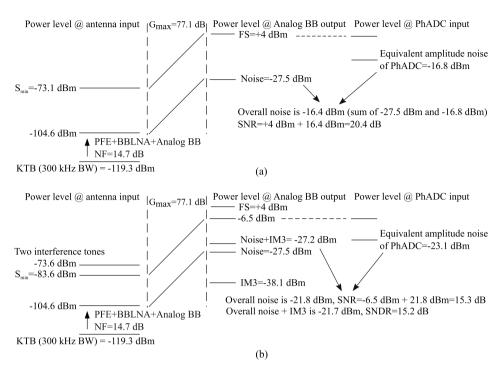

Using the proposed PFE and charge-redistribution PhADC, a receiver system is constructed. Based on the measured performance of the PFE and the PhADC, the simulated performance of a PGA and a 2<sup>nd</sup>-order filter and the analysis outcomes of the PhADC presented in Chapter 4, the benefit of using the PhADC for a receiver system is quantified. For the proposed PFE and the IEEE 802.15.6 application, two ADCs (for I and Q paths) with a SNR of 30.4 dB are

needed if an amplitude ADC is used, while a PhADC with a phase SNR of 24.5 dB (when the input amplitude is -11.9 dBm) is sufficient if a PhADC is used. For an antenna input level of -83.6 dBm (which corresponds to the minimum input level that has been specified for the PhADC), the presented receiver system demonstrates a sufficient overall SNR for the IEEE 802.15.6 standard, thereby paving the way to fully-integrated low-power receivers for the standard.

## Samenvatting

Het verminderen van het energieverbruik van laagvermogens- korte-afstands-ontvangers is van cruciaal belang voor biomedische en Internet-of-Things (IoT) toepassingen. Twee interessante vrijheidsgraden (of eigenschappen) die niet ten volle zijn benut in het streven naar een laag energieverbruik zijn de antenne-impedantie en de alleen-fase modulatie-eigenschap van FSK/PSK-signalen. Dit proefschrift onderzoekt de mogelijkheid van het verminderen van het energieverbruik van de ontvanger met behulp van deze twee graden van vrijheid.

De haalbaarheid van het gebruik van een niet- $50\Omega$  antenne-impedantie in een actief ontvanger-frontend wordt eerst bestudeerd. Een algemene antenne-elektronica koppeling-analyse wordt uitgevoerd, waarvan het resultaat suggereert dat vermogensoverdracht niet de enige ontwerpdoelstelling is in de koppeling, maar dat de impedanties van de antenne en de belasting moeten worden geoptimaliseerd voor ofwel spanning of stroom, afhankelijk van wat gunstiger te meten of aan te sturen is met de elektronica. Dit principe is toegepast op een co-ontwerp-voorbeeld van een inductieve antenne-impedantie en een ruisarme voorversterker (Engels: low-noise amplifier, LNA). Passieve spannings-versterking kan worden bereikt met behulp van het voorgestelde beginsel, en derhalve kan het ruisgetal (Engels: noise figure, NF) worden gereduceerd zonder in te boeten aan energieverbruik.

Het begrip van een niet-50  $\Omega$  antenne-impedantie is ook benut in de context van passieve front-ends (PFE's). Een inductieve antenne-impedantie blijkt gunstig voor het verhogen van de passieve spanningsversterking van een antenne-LNA koppeling. De studie van het PFE beoogt hetzelfde spanningsverhogings-effect door het opnemen van de inductieve antenne-impedantie in het PFE. Uit de analyse blijkt dat de inductieve antenne-impedantie twee extra graden van vrijheid introduceert voor het verhogen van de omlaag geconverteerde

spanning van het front-end voor een bepaald beschikbaar antennevermogen. Om de passieve spannings-versterking, aangeboden door de inductieve antenne-impedantie samen met zijn resonante belasting, goed te handhaven, dient de passieve mixer een capacitieve input met een hoge kwaliteits-factor te laten zien. Dit wordt bereikt door het opnemen van een tussenliggende inductantie in het passieve netwerk. Het voorgestelde front-end en een basisband LNA zijn geïmplementeerd om het spanningsverhogingseffect te verifiëren. De realisatie heeft een passieve spannings-versterking van 11,6 dB, hetgeen de state-of-the-art van 12 dB benadert.

Een veelbelovend concept dat volledig gebruik kan maken van de eigenschap van alleen-fase modulatie van FSK/PSK signalen is dat van fase-domein analoog-naar-digitaal-omzetters (Engels: phasedomain analog-to-digital converters, PhADCs). Dit proefschrift houdt zich ook bezig met de analyse en het ontwerp van PhADCs. Bovenal worden analysemethoden voorgesteld voor een volledige vergelijking van de PhADC en een (in-fase en kwadratuur) IQ ADC. Uitdrukkingen voor de fase-signaal-ruis-verhouding (Engels: signal-tonoise-ratio, SNR) van de twee ADC types zijn analytisch geformuleerd voor een kwantitatieve vergelijking van de ADC's. In vergelijking met de IQ ADC is de PhADC, als gevolg van de ingebouwde demodulatieeigenschap, een compactere kwantisatie- en demodulatie-oplossing wanneer interferentie-accommodatie niet vereist is. Bovendien, bijvoorbeeld in het geval van een flits- (Engels: flash) ADC als lage-resolutie (3-4 bits) IQ ADC, heeft de PhADC een lagere theoretische energielimiet dan de flits IQ ADC voor een gegeven effectief aantal bits (Engels: effective number of bits, ENOB) van de fase, vanwege de immuniteit voor sterkte-variaties en de alleen-fase kwantisatie, waarmee de grote potentie voor verbetering van de energie-efficiëntie middels de PhADC wordt aangetoont. Ten tweede, na de interessante eigenschappen van de PhADC te hebben besproken, wordt een IQ-ondersteund conversie-algoritme en een bijbehorende circuit-topologie om de energieefficiëntie van de PhADC te verbeteren voorgesteld. Dankzii het opeenvolgende-benaderings- (Engels: successive approximation, SAR) achtige algoritme en de werking in het ladingsdomein behaalt het prototype een maat van verdienste (Engels: figure of merit, FoM) van 1,2 pJ/conversie-stap, hetgeen beter is dan de stand van de techniek van 8.3 pJ/conversie-stap. Ten slotte wordt de expliciete relatie tussen

de ingangs-amplitude SNR en de uitgangs-fase SNR van de PhADC geformuleerd. Deze relatie vergemakkelijkt de systeemanalyse van een ontvanger die gebruik maakt van een PhADC.

Met het voorgestelde PFE en ladings-herverdelings-PhADC is een ontvanger-systeem gebouwd. Gebaseerd op de gemeten performatie van het PFE en van de PhADC, de gesimuleerde prestaties van een instelbare versterker (Engels: programmable gain amplifier, PGA) en een 2e-orde filter en de resultaten na analyse van de PhADC die beschreven in hoofdstuk 4, zijn de voordelen van de PhADC voor een ontvanger gekwantificeerd. Voor de voorgestelde PFE en de IEEE 802.15.6 toepassing zijn twee ADC's (voor het I- en het Q- pad) met een SNR van 30.4 dB nodig als een amplitude ADC wordt gebruikt, terwijl een PhADC met een fase-SNR van 24.5 dB (wanneer het ingangs-niveau -11.9 dBm is) voldoet. Voor een antenne met een ingangsniveau van -83.6 dBm (wat overeenkomt met het gedefinieerde minimum ingangsniveau voor de PhADC), toont de voorgestelde ontvanger een voldoende totale SNR voor de IEEE 802.15.6 standaard. Dit stelt de weg open tot volledig geïntegreerde ontvangers met een laag vermogensverbruik voor de standaard.

## Contents

| Sι | ımm  | ary                                                       | i  |

|----|------|-----------------------------------------------------------|----|

| Sa | amen | vatting                                                   | iv |

| 1  | Intr | roduction                                                 | 1  |

|    | 1.1  | Motivation                                                | 3  |

|    |      | 1.1.1 Non-50 $\Omega$ antenna impedance                   | 3  |

|    |      | 1.1.2 Phase-only quantization and demodulation            | 5  |

|    | 1.2  | Challenges and objectives                                 | 6  |

|    |      | 1.2.1 Active and passive receiver front-ends with non-    |    |

|    |      | $50 \Omega$ antenna impedances                            | 6  |

|    |      | 1.2.2 Phase-domain ADC                                    | 8  |

|    | 1.3  | Thesis organization                                       | 9  |

| 2  | Co-  | design of low-noise amplifiers and non-50 $\Omega$ anten- |    |

|    | nas  | 2                                                         | 11 |

|    | 2.1  | Introduction                                              | 11 |

|    | 2.2  | Co-design principle                                       | 11 |

|    | 2.3  | A co-design example: a 900 MHz LNA with an induc-         |    |

|    |      | tive antenna impedance                                    | 16 |

|    | 2.4  | Conclusions                                               | 19 |

| 3  | Pas  | sive receiver front-ends with non-50 $\Omega$ antennas    | 21 |

|    | 3.1  | Introduction                                              | 21 |

|    | 3.2  | A passive front-end with an inductive antenna impedance   | 22 |

|    |      | 3.2.1 Voltage gain                                        | 24 |

|    |      | 3.2.2 Effects of switch on-resistance                     | 31 |

|    |      | 3.2.3 Bandwidth                                           | 33 |

|    |      | 3.2.4 Noise analysis                                      | 34 |

x CONTENTS

|    | 3.3   | Passive front-end implementation                     | 38  |

|----|-------|------------------------------------------------------|-----|

|    |       | 3.3.1 Passive network                                | 39  |

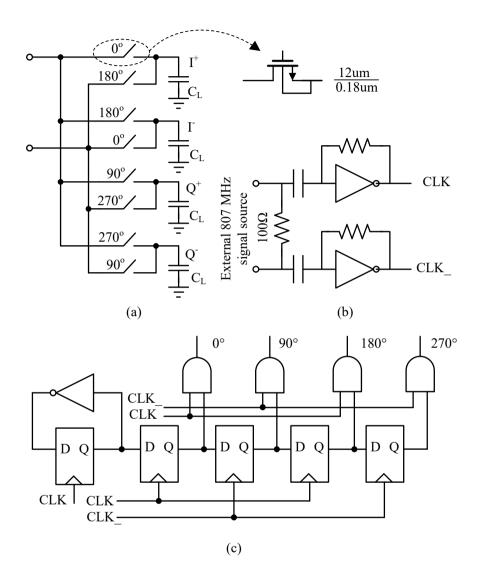

|    |       | 3.3.2 25% duty cycle quadrature passive mixer and    |     |

|    |       | clock generator                                      | 42  |

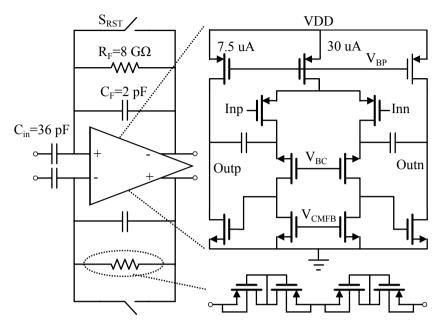

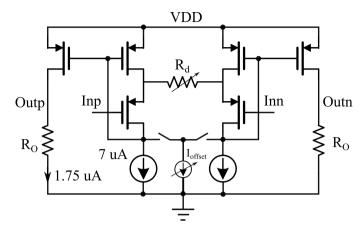

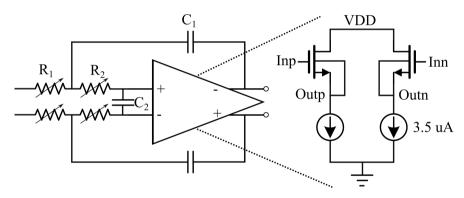

|    |       | 3.3.3 Band-pass low-noise amplifier                  | 42  |

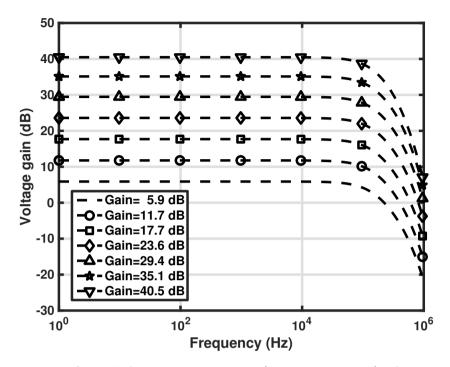

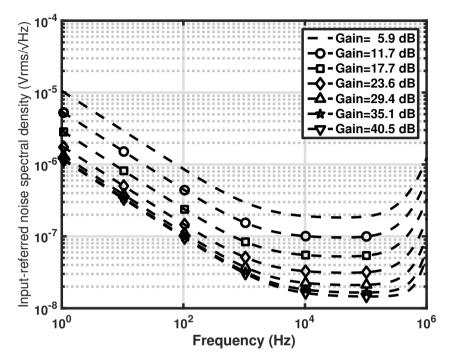

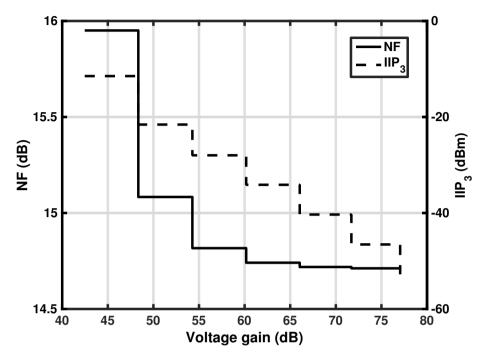

|    | 3.4   | Measurement results                                  | 45  |

|    | 3.5   | Conclusions                                          | 50  |

| 4  | Pha   | ase-domain ADCs                                      | 53  |

|    | 4.1   | Introduction                                         | 53  |

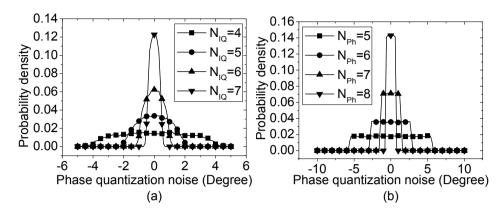

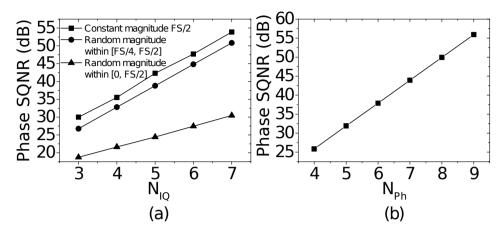

|    | 4.2   | Phase SQNR of IQ ADC and PhADC                       | 54  |

|    |       | 4.2.1 IQ ADC                                         | 54  |

|    |       | 4.2.2 PhADC                                          | 58  |

|    | 4.3   | PhADC and IQ ADC comparison                          | 62  |

|    | 4.4   | A charge-redistribution PhADC                        | 65  |

|    |       | 4.4.1 Conversion algorithm and system architecture . | 66  |

|    |       | 4.4.2 Circuit design                                 | 68  |

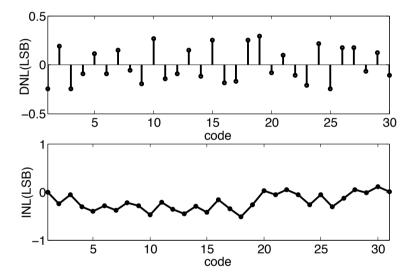

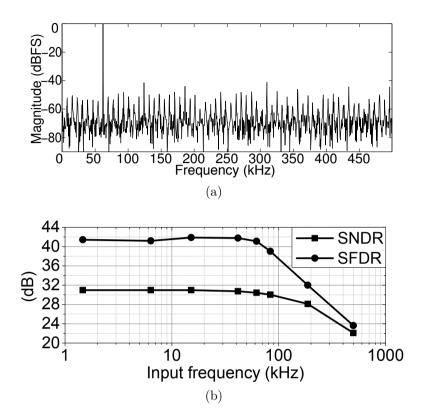

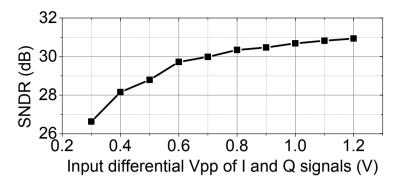

|    |       | 4.4.3 Measurement results                            | 71  |

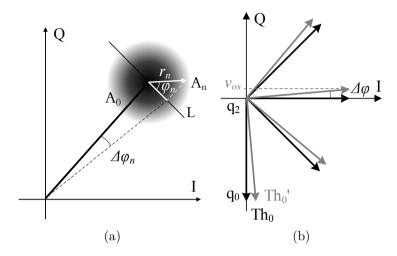

|    | 4.5   | Phase nonidealities of the PhADC                     | 75  |

|    |       | 4.5.1 Input noise                                    | 75  |

|    |       | 4.5.2 Comparator offsets                             | 79  |

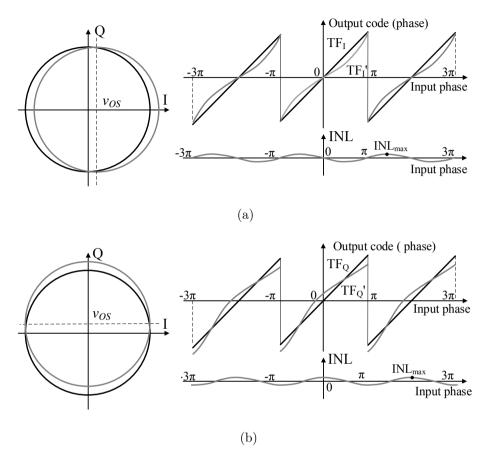

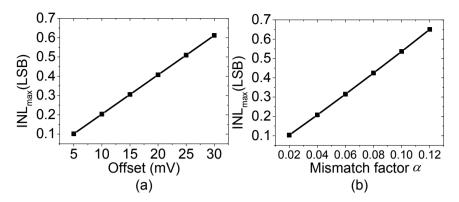

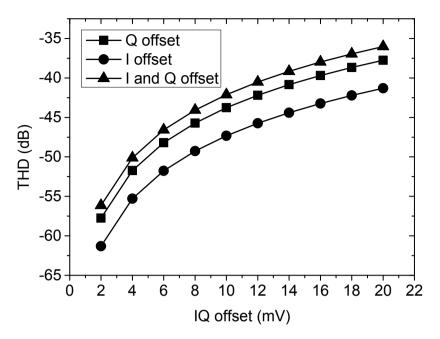

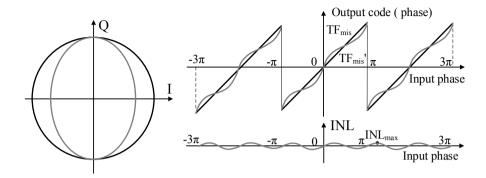

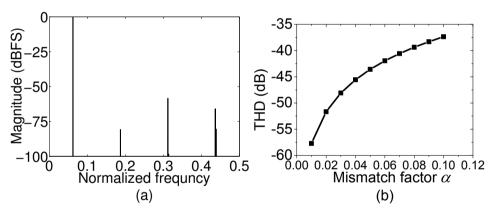

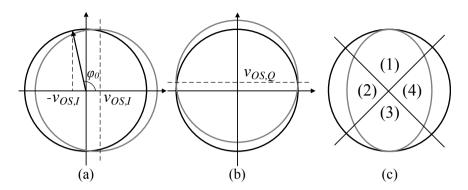

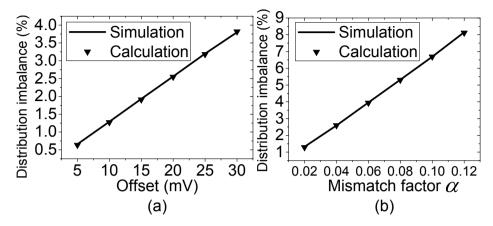

|    |       | 4.5.3 IQ offsets and IQ amplitude mismatch           | 80  |

|    |       | 4.5.4 IQ offsets and IQ amplitude mismatch detection | 86  |

|    | 4.6   | Conclusions                                          | 87  |

| 5  |       | 102 MHz receiver for IEEE 802.15.6 WBAN stan-        |     |

|    | dar   |                                                      | 91  |

|    | 5.1   | Introduction                                         | 91  |

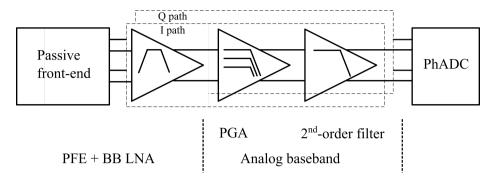

|    | 5.2   | System implementation                                | 91  |

|    | 5.3   | System performance                                   | 94  |

|    | 5.4   | Conclusions                                          | 100 |

| 6  |       | nclusions and future work                            | 103 |

|    | 6.1   | General conclusions                                  | 103 |

|    | 6.2   | Original contributions                               | 105 |

|    | 6.3   | Recommendations for future work                      | 106 |

| Re | efere | nces                                                 | 107 |

| CONTENTS             | xi  |

|----------------------|-----|

| Acknowledgements     | 115 |

| List of Publications | 117 |

| About the Author     | 119 |

## Chapter 1

## Introduction

The markets of wearable and implantable healthcare, fitness monitors and Internet of Things have been growing tremendously recently. Short-range radios are widely employed in these applications to connect various devices. Form factor and battery life are critical for these applications. Since the radio is often one of the most power-hungry blocks in small sensing nodes, improving the energy efficiency of the radio is of significant interest for both academic and industry communities. Reducing the power consumption of the radios can be challenging, however, as with every electronic system there is always a trade-off between power consumption and performance parameters of interest, which should be wisely dealt with to improve the energy efficiency of the radios. A low-power short-range receiver usually requires very loose specifications of sensitivity, frequency selectivity and data rate, which could be exploited in the pursuit of low overall power consumption. This principle has led to a number of low power architectural and circuit techniques that are briefly summarized below.

Owing to the low data rate requirement, simple amplitude modulation schemes such as on-off keying (OOK) and amplitude shift keying (ASK) can be used for the low-power receiver. These signals can be demodulated by an energy/envelope detector [1], a superregenerative receiver [2–4], or an uncertain-IF receiver [5], all of which are extremely low power thanks to the absence of an accurate but power hungry frequency reference. One important challenge of the OOK/ASK low power receivers is their poor interference robustness. Several techniques such as "2-tone architecture" [6], "transmitted ref-

erence + shifted limiter" [7], and "dual-IF multi-stage N-path architecture" [8] have been proposed to enhance the interference resilience. Nevertheless, the low spectral efficiency of the OOK and ASK modulation schemes and the low data rate of the above receivers often limit their applications to a wake-up receiver, rather than the main data receiver of a receiving system. The modulation schemes employed for the main communication link are usually frequency shift keying (FSK) or phase shift keying (PSK), such as gaussian minimum shift keving (GMSK), gaussian frequency shift keving (GFSK), differential quadrature phase shift keying (DQPSK) and Offset-QPSK [9-11]. A number of efforts have been made to improve the energy efficiency of the receivers for these modulation schemes. The power consumption of the PLL and its buffers can be significantly reduced by employing an off-chip high-quality bulk acoustic wave (BAW) resonator [12], an optimum frequency translation plan (e.g., sliding-IF downconversion in [13, 14]), low-power all-digital PLL [15] and the sub-sampling technique [16, 17]. In order to achieve a compact and efficient receiver front-end, the functionalities of a low-noise amplifier (LNA), a mixer and a voltage-controlled oscillator (VCO) can be merged together as one unit and its bias current can even be shared with baseband stages [18]. Another approach to save the power of the front-end is replacing the active LNA with a passive amplification network such as a step-up transformer [19, 20] or an LC resonant matching network [21]. Also, the phase-only modulation property of the FSK/PSK signals can be utilized to implement a phase-domain analog-to-digital converter (PhADC) [20, 22] or a PLL-based receiver [23, 24]. Both the PhADC-based receiver and the PLL-based receiver simplify the standard Cartesian analog signal conditioning, exhibiting impressive energy efficiency.

However, an interesting degree of freedom that has not been fully exploited for a low-power receiver is the antenna impedance. This dissertation explores the possibility of reducing the power consumption of the receiver by utilizing this freedom. Also, the phase-only-modulation property of the FSK/PSK signals is further exercised.

1.1. MOTIVATION 3

#### 1.1 Motivation

#### 1.1.1 Non-50 $\Omega$ antenna impedance

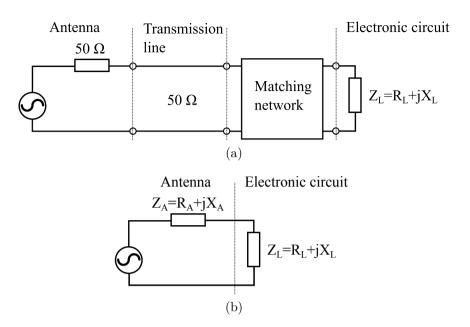

During the design process of a wireless receiver system, the antenna and electronic circuit designers sometimes are operating independently from each other and considered to belong to separate disciplines. Both designers agree upon a common characteristic impedance of the antenna-electronics interface and subsequently optimize their part of the receiver system. The electronic circuit often requires an impedance transformation network while the antenna usually is directly matched to the characteristic impedance of a transmission line to avoid propagation effects at the interface, as shown in Fig. 1.1(a). Traditionally, this characteristic impedance is commonly assumed to be 50  $\Omega$  and the interface is impedance matched  $(50\Omega-50\Omega \text{ matching})$ . However, it's important to note that  $50 \Omega$  is only a traditional value originally meant to offer a reasonable compromise between loss and power-handling capability for a coaxial cable with an air dielectric [25]. Also, if the length L between the antenna and the electronic circuit is electrically short  $(L<\lambda/10, \lambda \text{ being the wavelength})$ , then the propagation effects in the interface can be neglected as the voltage and current can be considered constant along the connection [26], and hence there is no fundamental reason to use a transmission line in the interface. This, for example, may be the case for integrated circuits (ICs) with on-chip antennas [27] and ICs that are close enough to an off-chip antenna [28–30], especially at low frequencies (e.g.,  $\lambda$  is as large as 300 mm at 1 GHz in the air). For the electrically-short interface, if the maximum power delivery is not the objective of interest, the impedance matching is no longer necessary. This opens up the possibility to directly match the antenna to the electronic circuitry as illustrated in Fig. 1.1(b). The freedom of antenna impedance could and should be fully exercised to optimize the performance of interest for a given application, rather than simply complying with the comfortable 50  $\Omega$  standard.

The reader may wonder if the above principle applies to a wireless system with more practical constraints imposed by blocks such as band-selection filters and transmitters. We make the following observations. (1) The band-selection filter is usually an off-chip component interposed between an antenna and a receiver IC, and is typically

Figure 1.1: (a) Conventional 50  $\Omega$  antenna-electronics interface. (b) Electrically short antenna-electronics interface with a non-50  $\Omega$  antenna impedance.

designed for a standard 50  $\Omega$  termination. If the input or output termination deviates from 50  $\Omega$ , then the passband and stopband characteristics of the filter may exhibit loss and ripple [31]. Fortunately, for a single-band low-power short-range receiver, the off-chip band-selection filter can be omitted [24,32], due to the relaxed frequency selectivity of standards such as Bluetooth Low Energy. Furthermore, even in the presence of the on-chip band-selection filter, the above principle still holds for the interfaces of antenna-filter and filter-circuitry respectively, although they may require more overall compromises than the antenna-circuitry interface does. (2) In a modern wireless system, a stand-alone receiver rarely exists, and hence the transmitter must also be taken into account when selecting the antenna impedance. From the transmitter point of view, it appears that the antenna impedance should contain a negligible reactive part so that it maximally radiates the signal power [31]. However, in practice, the optimum load impedance for the maximum efficiency of the transmitter heavily depends on the specifications of maximum power, supply voltage, power amplifier (PA) topology, matching network and parasitics, thereby 1.1. MOTIVATION 5

being unnecessarily equal to 50  $\Omega$  or any other resistive value. Thus, there is no fundamental reason for keeping a 50  $\Omega$  antenna impedance.

In Section 1.2, we address the design challenges of a receiver based on the non-50  $\Omega$  antenna impedance, as well as our objectives.

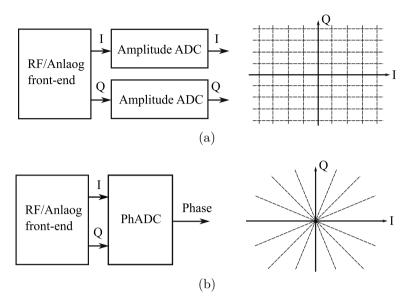

#### 1.1.2 Phase-only quantization and demodulation

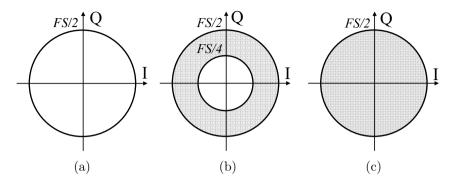

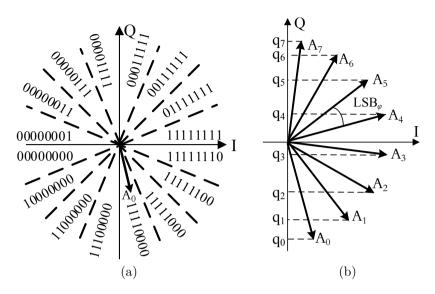

In a typical receiver system, downconverted FSK/PSK signals are commonly digitized by a pair of in-phase and quadrature (I and Q) amplitude ADCs (IQ ADC) before subsequent phase demodulation in the digital domain, as shown in Fig. 1.2(a). The complex IQ plane is uniformly segmented by amplitude into several discrete levels. Alternatively, modulation-specific quantization and demodulation approaches can be used by exploiting the unique properties of the modulation schemes at hand. The fact that in the FSK and PSK modulation schemes data information is encoded in the signal phase alone is utilized by a PhADC by only quantizing phase information as opposed to I and Q amplitude information, and hence the IQ plane is uniformly segmented by phase rather than amplitude, as shown in Fig. 1.2(b). Several benefits can be expected from the phase-only quantization. (1) While the IQ ADC needs subsequent digital demodulation, the PhADC embeds most of the demodulation process in the quantization, thereby saving the power and area otherwise needed for the demodulation. (2) Since phase is the only signal of interest, the power consumption of the PhADC can be considerably reduced with respect to that of the IQ ADC if they have the same energy efficiency.

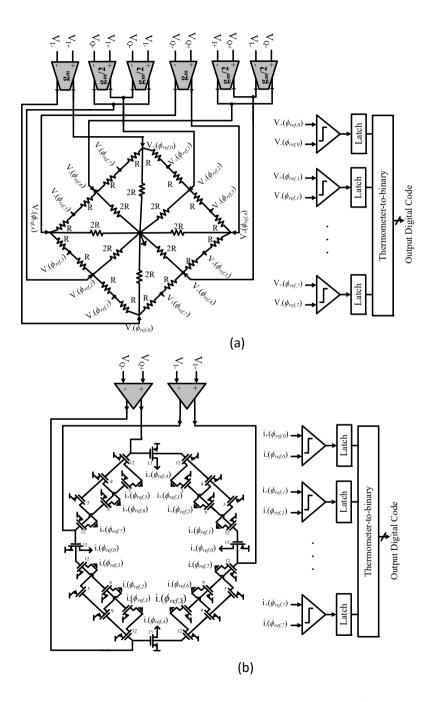

A number of analysis and silicon implementations of the PhADC have been reported. PhADC-based demodulators have proven to have bit-error-rate (BER) characteristics close to an ideal coherent GFSK demodulator [33]. PhADCs based on a zero-crossing (ZC) conversion algorithm have been realized in silicon by a resistor-bridge-based approach [34,35] as well as a current-mirror-based approach [20,22]. The benefits of robustness to circuit nonidealities and noise and large amplitude dynamic range of the resistor-bridge-based ZC PhADC has been addressed in [36]. It is also interesting to mention the polar quantizer proposed in [37,38]. The phase quantization path of the polar quantizer can be considered as a type of PhADC. Compared to

Figure 1.2: I and Q signals are digitized by (a) a pair of amplitude ADCs, and (b) a PhADC, respectively.

a traditional Cartesian quantizer, the polar quantizer can boost the signal to quantization noise ratio (SQNR) of a receiver.

In the following section, the limitations of the circuit topologies and analytical techniques presented in the above publications are examined, and hence the objectives of this dissertation can be addressed.

#### 1.2 Challenges and objectives

## 1.2.1 Active and passive receiver front-ends with non-50 $\Omega$ antenna impedances

This thesis explores the feasibility of using a non-50  $\Omega$  antenna impedance for both an active and a passive receiver front-end. For the former case, the focus is on the antenna impedance and the first stage of the active front-end, which often is an LNA. Several questions arise when the design process no longer begins from the 50  $\Omega$  impedance matching. First of all, the input of an antenna is a power quantity, while the quantity of interest from the LNA point of view is usually either voltage or current. So which choice of the antenna impedance maximizes

the voltage or current for a given antenna power? Second, with both freedom of the antenna impedance and the input impedance of the LNA, how do we begin the co-design? Moreover, apart from signal, noise is also of critical importance for the LNA. Can noise metrics (e.g., noise figure (NF) ) be optimized together with signal metrics (e.g., voltage or current gain) by co-designing the antenna and the LNA? These questions are answered in Chapter 2.

A passive front-end (PFE) (or mixer-first front-end) avoids active LNAs or low-noise transconductance amplifiers (LNTAs), and active mixers, and hence can potentially reduce the power consumption of a receiver. Although the PFE features high linearity, flexible frequency programability and baseband impedance upconversion [39–42], it suffers from a tight trade-off between power consumption and noise figure (NF). This is because the NF of a passive mixer is often improved by lowering the on resistance of the switches or increasing the number of non-overlapping phases [43], which are both directly paid by a larger power consumption of the local oscillator (LO) buffers. This tight trade-off might not always be affordable for a low-power short-range receiver with a power budget of only a few milliwatts or even below one milliwatt. A passive amplification network such as a step-up transformer [19, 20] or an LC resonant matching network [21] prior to the passive mixer can effectively relax the power-NF trade-off.

The passive network is often designed under the a constraint of a 50  $\Omega$  antenna impedance, or even 50  $\Omega$  impedance matching. The concept of a non-50  $\Omega$  antenna impedance is also exploited in the context of PFEs in this thesis. We consider the topology of a direct-conversion quadrature passive mixer in this study. Owing to the time-variant and bidirectional nature of the passive mixer, the input impedance of the mixer is strongly dependent on its source impedance. Also, both the signal and noise in the passive mixer experience frequency translation, which does not occur in the LNA. These two reasons make interfacing the antenna and the passive mixer very different from co-designing the antenna and the LNA. Consequently, the questions addressed for the active front-end still hold but need to be studied and answered differently, which are presented in Chapter 3.

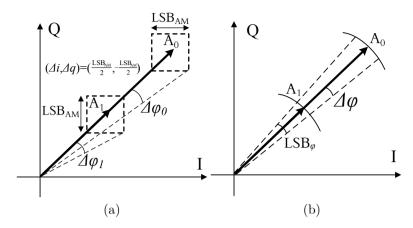

#### 1.2.2 Phase-domain ADC

As described in Section 1.1.2, a PhADC is a promising alternative to an IQ ADC for low power wireless receivers. However, there is a lack of thorough and accurate analysis of the fundamental benefits and limitations of the PhADC over the IQ ADC in the literature. The difficulty primarily arises from the fact that the two ADCs process signals in different domains, i.e., the phase and the amplitude domain, respectively. Thus, a connection between these two domains must be established to facilitate the comparison between the two ADCs. Also, the relationship between the amplitude and phase of the PhADC is necessary for the system analysis of a receiver using the PhADC, because amplitude is a more familiar quantity for analog circuitry. Finally, the influence of amplitude nonidealities on the phase quality of the PhADC needs to be quantified as well.

From an implementation perspective, the reported PhADCs [20, 22, 33, 35] have several limitations. The principle of the conversion algorithm employed in these PhADCs is to detect the zero-crossings of rotated I and Q projections, i.e., a zero-crossing algorithm. This algorithm relies on the accurate linear combinations of I and Q signals with various scaling factors, thereby limiting the efficiency and the simplicity of the hardware implementation. Besides, the amplitude nonidealities arising from the linear combination circuitry also degrade the performance of the zero-crossing PhADCs. For example, the 4 bit resistor-bridge-based zero-crossing PhADC in [35] needs at least two power-hungry fully differential chopped operational transconductance amplifier (OTAs) to convert I and Q voltages into currents, which are subsequently converted into several phase-rotated voltages with the aid of a resistor bridge. The nonlinearities and the noise of the OTAs as well as the mismatch and the noise of the resistor bridge can introduce significant errors to the phase signal. In [20,22], similar amplitude nonidealities also occur during the voltage to current conversion in the current-mirror-based PhADC. Furthermore, both the resistor-bridgebased and the current-mirror-based PhADCs operate in a flash-like fashion, thus consuming static power in either the resistor bridge or the current mirrors. The polar quantizer proposed in [37,38] uses a time-to-digital converter (TDC) to quantize the phase information. Though being a very interesting phase quantization technique, the proposed TDC is very power-hungry ( $\sim$ 7 mW), since it targets LTE applications and hence needs to operate at a speed of 40 MHz speed with a resolution of 12 bit.

In order to fulfill the potential of the PhADC mentioned in Section 1.1.2, we need to develop a new conversion algorithm which can avoid the above issues, and implement the algorithm in an efficient fashion. These are the objectives of Chapter 3.

#### 1.3 Thesis organization

The remainder of this thesis is organized as follows.

Chapter 2 first presents a co-design principle for electrically-short antenna-LNA interfaces. The principle is then verified by a design example of a 900 MHz LNA using an inductive antenna impedance.

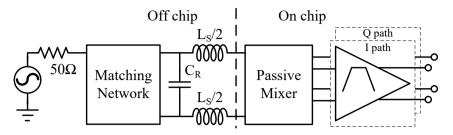

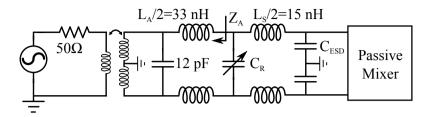

Chapter 3 presents a PFE using a non-50  $\Omega$  (inductive) antenna impedance. A passive network based on the inductive antenna impedance is proposed to provide a passive voltage gain in front of a passive mixer. Analytical methods for the desired signal transfer and noise behavior of the proposed PFE are also presented to facilitate the design. The proposed PFE together with a baseband low-noise amplifier are implemented to verify the voltage-boosting effect.

Chapter 4 deals with the analysis and design of a PhADC. Analytical methods to compare a PhADC with an IQ ADC are presented. The principal merits and drawbacks of the PhADC are then accurately formulated or addressed with the aid of several implementation examples of the PhADC and the IQ ADC. Moreover, a new conversion algorithm and a corresponding circuit implementation are proposed to improve the energy efficiency of the PhADC. Finally, the influence of amplitude nonidealities on the phase is quantified for the PhADC.

A system integration of the PFE and the PhADC is demonstrated in Chapter 5. The system aims to comply with the specifications of the 402-405 MHz band of the IEEE 802.15.6 WBAN standard.

Finally, a summary of the main contributions of this work, together with some recommendations for future work, are given in Chapter 6.

## Chapter 2

# Co-design of low-noise amplifiers and non-50 $\Omega$ antennas

#### 2.1 Introduction

By designing a proper interface between the antenna and the electronics, both disciplines share a common optimization target and can agree on a non- $50\Omega$  interface impedance to optimize the overall system performance for a specific application. The choice of interface impedance plays a crucial role in the performance optimization. In this chapter, a general co-design principle is addressed, followed by a co-design example of an LNA with an inductive antenna impedance to demonstrate the benefits of the proposed principle for low power receivers.

### 2.2 Co-design principle

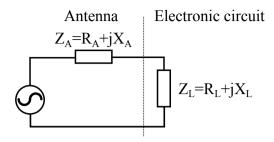

As addressed in Chapter 1, if an IC is directly connected to an off-chip antenna and the connection between them is electrically short, the antenna and the circuitry can be directly matched without any intermediate stages, as modeled by Fig. 2.1. An optimum choice of antenna impedance  $Z_{\rm A}$  and load impedance  $Z_{\rm L}$  allows us to increase the voltage or current at the antenna load for the same available power

Figure 2.1: Input impedance of the electronic circuitry is directly matched to that of a non-50 $\Omega$  antenna impedance.

Figure 2.2: Antenna load impedance equivalent models.

at the antenna.

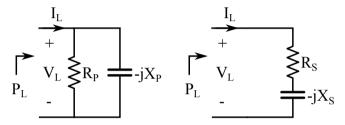

Optimizing the interface for maximum voltage or current is a matter of first optimizing the antenna load impedance. In many cases, the load for a given frequency range can be modeled as either a series or parallel combination of a resistance and a reactance (Fig. 2.2). Depending on preference and application, one might be more convenient to use than the other, but both provide the same characteristics. An antenna load impedance with a capacitive reactance is assumed hereafter, which holds for the majority of integrated circuits.

Without making any assumptions about the source, the power in the load can be expressed as:

$$P_L = \left(1 - \left|\Gamma\right|^2\right) P_{av} \tag{2.1}$$

where  $\Gamma = \left(Z_L - Z_A^*\right)/\left(Z_L + Z_A\right)$  is the power wave reflection coefficient [26],  $Z_A$  is the antenna impedance,  $Z_L$  is the antenna load impedance and  $P_{av}$  denotes the power available to the antenna. The root-mean-squared (RMS) current magnitude through the load then equals:

$$|I_L| = \sqrt{\frac{2\left(1 - |\Gamma|^2\right)P_{av}}{R_S}} \tag{2.2}$$

while the RMS voltage magnitude across the load is:

$$|V_L| = \sqrt{2\left(1 - |\Gamma|^2\right)P_{av}R_P} \tag{2.3}$$

In both cases, a conjugate matched interface  $(Z_A = Z_L^*)$  produces the maximum voltage and current at a given antenna load, which is the first condition to optimize the desired signal quantity. Although this condition relates the relative impedance between the antenna and the electronic circuit, the key point is that an additional increase in voltage or current can be achieved by correctly choosing at which impedance level conjugate matching occurs.

When assuming an ideal conjugate matched interface, the RMS voltage across the parallel load terminals is given by:

$$|V_L| = \sqrt{2P_{av}R_P} \tag{2.4}$$

The voltage across the load of the equivalent series impedance is calculated using the resistance parallel-to-series conversion equation:

$$R_P = \left(1 + Q^2\right) R_S \tag{2.5}$$

where  $Q=(X_S/R_S)=(R_P/X_P)$ . Note that this impedance conversion is only valid around the resonance frequency. The RMS voltage in terms of the series load is then expressed as:

$$|V_L| = \sqrt{2P_{av}R_S}\sqrt{1+Q^2} \tag{2.6}$$

Equation (2.6) indicates that the output voltage can be 'boosted' by increasing the Q-factor of the interface. It should be noted that this also requires a larger parallel load resistance R<sub>P</sub> due to the equivalence of (2.4) and (2.6). Hence, when the available power and antenna load are fixed, one cannot increase the load voltage to higher levels by means of antenna design. The designer therefore needs to design the electronic circuit for the largest R<sub>P</sub> possible and subsequently co-design the antenna impedance for conjugate matching. This conclusion is a key point that needs to be considered during the design procedure.

The RMS load current can similarly be found by writing:

$$|I_L| = \sqrt{\frac{2P_{av}}{R_S}} \tag{2.7}$$

and hence can only be maximized by minimizing R<sub>S</sub>. This is equivalent to the following expression in terms of the parallel load:

$$|I_L| = \sqrt{\frac{2P_{av}}{R_P}} \sqrt{1 + Q^2} \tag{2.8}$$

Thus, the maximum voltage and current at the interface is set only by the antenna load impedance and the available power. The series and parallel load representations are tools to help the designer to analyze and find the required impedance.

The antenna impedance  $(Z_A=R_A+jX_A)$  is found by determining the required ratio of the resistive and reactive part of the load impedance. When considering voltage to be the signal quantity to maximize and assuming a conjugate matched interface  $(X_A=X_S \text{ and } R_A=R_S)$ , Equation (2.6) can be rewritten as:

$$|V_L| = \sqrt{2P_{av}\left(\frac{R_A^2 + X_A^2}{R_A}\right)} \tag{2.9}$$

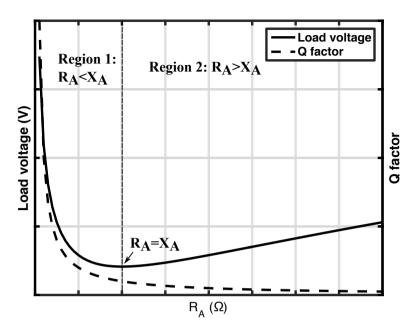

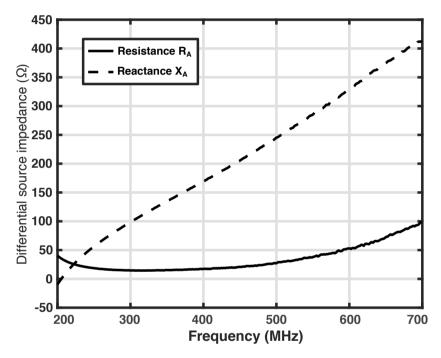

Equation (2.9) is plotted in Figure 2.3 together with the Q-factor and shows the antenna load voltage as a function of antenna resistance for a given  $P_{av}$  and non-zero  $X_A$ . Note that the voltage can be maximized by either decreasing or increasing  $R_A$  and is at its minimum when  $R_A=X_A$ . Two different regions therefore can be identified, i.e., Region 1 for  $R_A< X_A$  and Region 2 for  $R_A> X_A$ .

When assuming  $R_A \ll X_A$  in Region 1, (2.9) simplifies to

$$V_L|_{R_A \ll X_A} \approx \sqrt{2P_{av}} \frac{X_A}{\sqrt{R_A}}$$

(2.10)

In this region, the output voltage is passively boosted by the presence of the antenna reactance, which forms an LC resonator with the load. Significant improvement for large values of Q can be achieved at the expense of bandwidth. This property is exploited in [28], where the input voltage at the RF energy harvester is effectively increased

Figure 2.3: Antenna load voltage as a function of antenna resistance for non-zero antenna reactance.

using a high-Q loop antenna ( $Z_A=4.4+j328~\Omega$  at 868 MHz). The voltage boost improves the rectifier sensitivity, meaning that a wireless sensor node with an RF energy harvester can be operated at a larger distance from the RF energy source.

When assuming  $R_A \gg X_A$  in Region 2, (2.9) simplifies to

$$V_L|_{R_A \gg X_A} \approx \sqrt{2P_{av}R_A}$$

(2.11)

In this region, the antenna impedance can be considered to be purely resistive. The load voltage is simply determined by the resistive voltage division between the antenna and its load. But since the equivalent Thévenin antenna voltage itself depends on the antenna resistance by  $V_A = \sqrt{8P_{av}R_A}$  [44] ( $V_A$  is the peak value), the load voltage increases, although at a slower rate compared to Region 1. On the other hand, Region 2 has a fundamentally wideband characteristic, which can be exploited in the design of wideband LNA, where relatively large antenna resistances of 150  $\Omega$  [30] have been reported in the literature.

Figure 2.4: Interface model of an inductively degenerated CMOS LNA directly connected to an inductive antenna impedance including relevant noise sources.

# 2.3 A co-design example: a 900 MHz LNA with an inductive antenna impedance

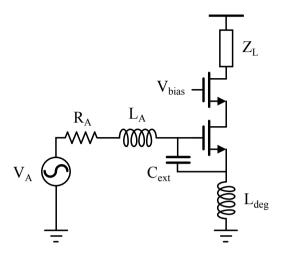

The co-design of any antenna-electronics interface starts by optimizing the antenna load impedance, which in this example is a 900 MHz narrowband LNA. The well-known inductively degenerated CMOS cascode LNA topology [45] is used as it provides an easy way of adjusting the LNA input impedance. The LNA is directly connected to an inductive antenna as depicted in Fig. 2.4. The information is sensed with a CMOS gate, meaning that voltage is the preferred signal quantity to maximize.

Along with the desired signal  $V_A$ , the antenna picks up noise from all points within its directivity radiation pattern and thus depends on how the antenna is directed towards its environment. However, at radio frequencies it is usually assumed that the random noise of an antenna is as low or lower than the thermal noise corresponding to room temperature [46]. The antenna noise can thus be modeled as  $\overline{V_{n,A}^2}=4kTR_A\Delta f$ , where  $k=1.38\cdot 10^{-23}$  J/K is Boltzmann's constant,  $T=300\,\mathrm{K}$ , and  $\Delta f$  denotes the unit bandwidth. Other relevant sources of noise are the channel noise of the transistor  $i_{n,d}^2=4kT\gamma g_m\Delta f$ , the gate

resistance  $\overline{v_{n,g}^2}$ =4kT $\gamma R_g \Delta f$  and the LNA load noise  $\overline{i_{n,L}^2}$ =4kT $\Delta f/R_L$ . Here,  $g_m$  denotes the transconductance of the MOS transistor,  $R_g$  is the transistor gate resistance and  $R_L$  is the equivalent thermal noise resistance of the LNA's load and subsequent stages. The coefficient  $\gamma$  is often between 2/3 and 2, depending on the transistor size and the technology.

The performance of the LNA is evaluated using the Noise Factor (F), which is a measure of how much noise is relatively added by the LNA compared to the noise generated by the source. It is worth to emphasize that the noise factor therefore is defined for a specific antenna resistance and thus can be improved by co-design. A larger antenna resistance for example generates more noise, but also equally scales the desired antenna voltage as  $V_A = \sqrt{8P_{av}R_A}$ . The input signal-to-noise ratio (SNR) therefore does not change. However, the noise of the LNA now appears relatively smaller compared to the antenna noise, resulting in a lower noise factor and therefore better SNR at the output.

For this particular LNA implementation, the interface impedance is defined as  $Z_{\rm int}=R_A+j\omega(L_A+L_{\rm deg})=R_A+jX_A$  as the total inductance in the interface is the sum of the antenna and the degeneration inductors. As the narrowband LNA operates in Region 1, the antenna load voltage is thus approximated by (2.10) for large values of Q. When assuming the interface to be at the resonance frequency with conjugate matching, the minimum noise factor for low and medium frequencies is approximated as:

$$F_{min} \approx 1 + \delta \frac{R_g}{R_A} + \underbrace{\frac{R_A}{X_A^2}}_{co-design} \underbrace{\left(\frac{\gamma}{g_m} + \frac{4}{g_m^2 R_L}\right)}_{LNA}$$

(2.12)

Notice that the 'LNA' term in (2.12) only depends on the LNA circuit parameters and can be minimized by increasing the MOS transistor's bias current and gate area. The 'co-design' term allows to reduce the noise factor without additional power consumption by using a high-Q impedance interface. By contrast, for an LNA with the same circuit topology but a 50  $\Omega$  power-matching interface,  $R_A$  and  $X_A$  cannot be selected freely, and hence the noise factor can only be reduced by sacrificing power. Reducing the power consumption is the main benefit offered by the proposed co-design principle. The input-

Figure 2.5: Simulated narrowband LNA noise figure for various interface impedances.

referred noise of  $R_g$  is suppressed by the interface gain due to the presence of the external capacitor  $C_{\rm ext}$ . This is indicated by  $\delta$ , which scales with  $1/Q^2$  when  $C_{\rm ext}\gg C_{\rm gs}$ .

The LNA is designed in AMS 0.18 um technology and its design parameters are kept constant during the following circuit simulations ( $g_m$ =366 uS,  $C_{gs}$ =4 fF,  $R_g$ =18  $\Omega$ ,  $R_L$ =10 k $\Omega$ ,  $\gamma$  = 1.1). The LNA input impedance is varied by tuning  $L_{deg}$  and  $C_{ext}$  while the antenna impedance is subsequently conjugate matched to the LNA input for each case. The inductive antenna impedance is modeled as an inductor  $L_A$  in series with a power port with resistance  $R_A$ . The difference in noise factor is thus only determined by the difference in interface impedance. As a proof of concept, the antenna impedance and matching components are considered lossless.

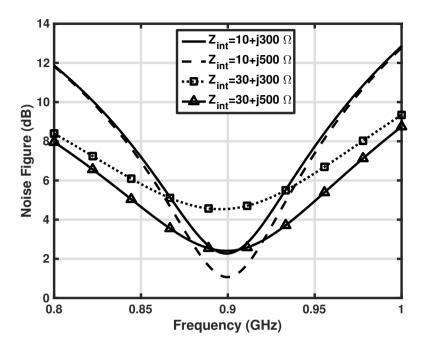

The impact of the 'co-design' term can be confirmed by the simulated noise figure (NF, in dB) for various interface impedances, as shown in Fig. 2.5. Note that, in order to clearly demonstrate the impact of the interface impedance  $Z_{\rm int}$ , some of  $Z_{\rm int}$  in Fig. 2.5 have a

2.4. CONCLUSIONS 19

big reactance and hence require an impractical value of  $L_{deg}$  (e.g., 50 nH). In practice, the feasibility of the required  $L_{deg}$  and other design constraints may result in interface impedances that are different from those in Fig. 2.5. (2.12) and Fig. 2.5 suggest that  $R_A$  should be as low and X<sub>A</sub> as high as possible to reduce NF. In practice however, this will cause the antenna radiation efficiency to drop considerably when the antenna conduction loss resistance becomes comparable to R<sub>A</sub> [44]. In this case, a minimum R<sub>A</sub> should be selected during the optimization process. The LNA input however, can be designed for maximum parallel resistance (i.e., purely capacitive input impedance) and therefore would increase the load voltage by 6 dB when keeping R<sub>A</sub> fixed at the minimum value [30]. It is important to point out that a conjugate matched interface in theory would increase the voltage even further, but in this case would require a purely inductive antenna with infinitely small antenna radiation resistance and conduction loss resistance, which of course is not realizable.

## 2.4 Conclusions

In this chapter, the feasibility of using a non-50  $\Omega$  antenna impedance for an active receiver front-end is studied. A general co-design principle is first presented for electrically-short antenna-electronics interfaces. It is argued that power transfer is not the only design objective in these interfaces, but that the impedances of antenna and load need to be optimized for either voltage or current, depending on which is more favorable to measure with the electronics.

The first condition is to conjugate match the antenna-electronics interface as this maximizes both the voltage and current at the load. The second condition is to determine at which impedance level conjugate matching should occur in order to further increase the load voltage or current. This is demonstrated with a co-design example of an inductive antenna impedance and an LNA. A passive voltage gain can be achieved by using the proposed principle, and hence NF can be reduced without sacrificing power consumption. These are useful properties that can be applied to low power receivers.

## Chapter 3

# Passive receiver front-ends with non-50 $\Omega$ antennas

### 3.1 Introduction

As described in Chapter 2, an inductive antenna impedance together with a resonant interface proves beneficial for increasing the passive voltage gain into an active low-noise amplifier (LNA), and hence reducing its noise figure (NF) as well. This chapter explores the feasibility of incorporating an inductive antenna impedance in a passive receiver front-end to obtain the same voltage-boosting effect.

For the study of a passive front-end (PFE), we consider the topology of a direct-conversion quadrature passive mixer. Owing to the time-variant and bidirectional nature of a passive mixer, interfacing an inductive antenna impedance and a passive mixer proves critical and challenging. Moreover, the frequency-dependent impedances preceding the mixer complicate the analysis of voltage gain and noise of the entire front-end. This chapter proposes an interfacing technique to improve the passive voltage gain as well as NF of the front-end, which is discussed in Section 3.2. Also, the analytical methods for the voltage gain and noise behavior of the proposed topology is presented to facilitate the design.

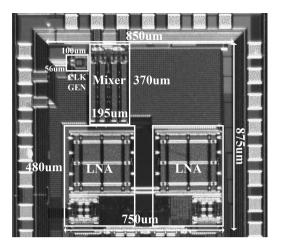

The proposed PFE together with a baseband LNA is implemented in 0.18  $\mu m$  CMOS technology to verify the voltage-boosting effect. The circuit implementation details are described in Section 3.3, while the measurement results of the design are presented and compared to

prior art in Section 3.4.

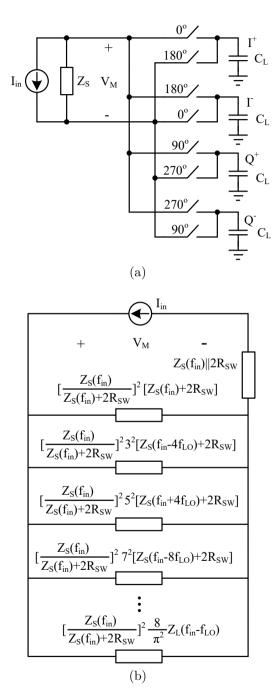

## 3.2 A passive front-end with an inductive antenna impedance

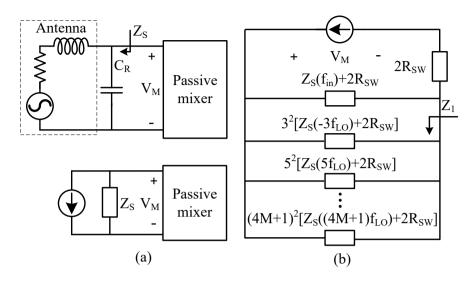

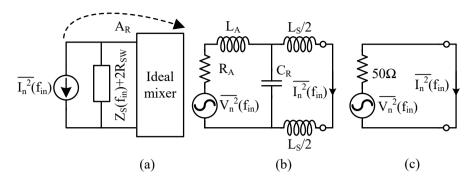

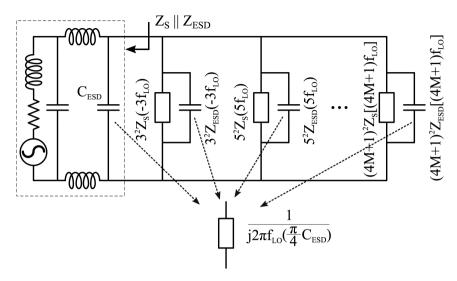

In this study, a 25% duty cycle (as opposed to 50%) quadrature passive mixer is used in the PFE due to its superior voltage gain, NF and linearity [47]. A 25% duty cycle quadrature passive mixer with an arbitrary source impedance, as shown in Fig. 3.1(a), can be modeled by the circuitry in Fig. 3.1(b) in the vicinity of switching frequency  $f_{LO}$  [19].  $I_{in}$  and  $Z_{S}$  represent the Norton equivalent of the source.  $C_{L}$  is the baseband capacitor,  $Z_{L}$  is its impedance,  $R_{SW}$  is the onresistance of the switches, and  $f_{in}$  is the input RF frequency. This model is utilized to develop analytical methods for our proposed PFE in this section and subsequent sections.

Given an inductive antenna impedance, the simplest approach to extract the maximum voltage is loading the antenna with a resonating capacitance, which usually consists of the intrinsic capacitive input impedance of most circuits (e.g., an energy harvester or an LNA) and an extra capacitor [28, 48]. Considering a quadrature passive mixer as the load of the inductive antenna in Fig. 3.2(a), owing to its bidirectional and time-variant nature, the mixer presents rather different input properties from most linear time-invariant circuits, thereby significantly degrading the voltage gain at the interface. This can be explained with the aid of the model in Fig. 3.1(b) as follows. First, the complexity of the mixer input impedance demands a few assumptions and conditions before more insight can be given: (1) The inductive antenna is resonant with a capacitor  $C_R$  at  $f_{LO}$ , and hence  $Z_S(f_{LO})$ is a relatively high impedance. (2) If we assume  $R_{SW} \ll Z_S(f_{LO})$ ,  $(1+2R_{SW}/Z_S(f_{LO})) = 1$  and  $Z_S(f_{in})||2R_{SW}=2R_{SW}$ . (3) Baseband capacitor C<sub>L</sub> presents an infinite impedance at DC. After transforming the The venin equivalent into its Norton counterpart as illustrated in Fig. 3.2(a), a simplified model can be given, as shown in Fig. 3.2(b). Z<sub>1</sub> is the parallel combination of  $(4M+1)^2[Z_S((4M+1)f_{LO})+2R_{SW}]$   $(M\neq 0)$ , where 4M+1 is the harmonic index. In order to maximize the input voltage of the mixer  $V_M$ ,  $Z_1$  must be sufficiently greater than  $Z_S(f_{LO})$ . While the bandpass-shaping  $Z_S(f)$  presents a large value at  $f_{LO}$ , the

Figure 3.1: (a) A 25% duty cycle quadrature passive mixer and (b) its equivalent model in the vicinity of switching frequency  $f_{LO}$  [19].

Figure 3.2: (a) A front-end consisting of a passive amplification network and a subsequent passive mixer (b) Equivalent circuit of the front-end at  $f_{\rm LO}$ .

impedance decreases rapidly as the frequency moves away from  $f_{LO}$  (i.e., as |M| increases).  $Z_S((4M+1)f_{LO})+2R_{SW}$  is therefore dominated by the  $2R_{SW}$  for large value of |M|. Thus, the overall effect of the parallel impedances results in a rather low quality factor complex  $Z_1$ , thereby considerably reducing the voltage gain at the interface.

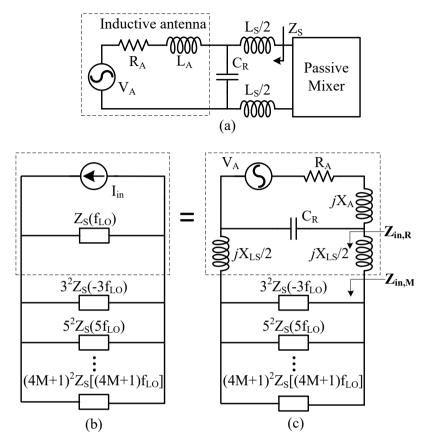

The proposed PFE is shown in Fig. 3.3(a). A series inductance is inserted between the inductive antenna and the mixer to boost the source impedance at harmonics of  $f_{LO}$ , thereby presenting a large impedance at the mixer input and maintaining the voltage-boosting effect offered by the antenna and  $C_R$ . To explain this more quantitatively, the voltage gain from the antenna to the baseband output of the mixer is analyzed in this section. Furthermore, the noise behavior of the proposed PFE is also analyzed, revealing an improved NF.

### 3.2.1 Voltage gain

We first make the following assumptions:

1. The inductive antenna impedance is resonant with  $C_R$  at  $f_{LO}$ , their impedances at  $f_{LO}$  being  $R_A+jX_A$  and  $-jX_A$ , respectively.

Figure 3.3: (a) Proposed PFE, (b) its equivalent model at  $f_{LO}$  with a Norton source, and (c) a physical source.

The quality factor of the antenna is  $Q_A=X_A/R_A$ .

- 2.  $R_{SW}$  is assumed to be zero for now, so  $(1+2R_{SW}/Z_S(f_{LO}))=1$  and  $Z_S(f_{in})||2R_{SW}=0$ . Also, the voltage gain from the mixer input to the differential baseband output is simply  $\sqrt{2}\pi/4$  due to the absence of the on-resistance [19]. Thus, the analysis of the voltage gain from the antenna to the baseband boils down to that of the voltage amplification at the mixer input, which is determined by the input impedance of the mixer near  $f_{LO}$ .

- 3. We focus on the voltage gain of the zero-IF product.  $f_{\rm in}$  is therefore assumed to be equal to  $f_{\rm LO}.$

#### 4. Baseband capacitor C<sub>L</sub> presents an infinite impedance at DC.

Under these assumptions, the model in Fig. 3.1(b) can be simplified into the one shown in Fig. 3.3(b). Furthermore,  $I_{\rm in}$  and  $Z_{\rm S}(f_{\rm LO})$  are transformed back into their physical model to facilitate analysis, as shown in Fig 3.3(c). The source impedance at  $f_{\rm LO}$  and its harmonics can be expressed as:

$$Z_S(Nf_{LO}) = (\frac{X_A}{Q_A} + jNX_A)||(-j\frac{X_A}{N}) + jNX_{LS},$$

(3.1)

where N is the harmonics index, and  $X_{LS}$  is the impedance magnitude of  $L_S$  at  $f_{LO}$ . The impedance of this  $R_A$ - $L_A$ - $C_R$  resonant network becomes dominated by  $C_R$  as |N| increases, thus the first term in (3.1) can be approximated as  $-jX_A/N$  for |N| greater or equal to 3. This also suggests that  $Q_A$  has little impact on  $Z_S(Nf_{LO})$  for |N| greater or equal to 3. Furthermore, we can define the input impedance of the mixer at  $f_{LO}$  as:

$$Z_{in,M} = \frac{1}{\sum_{M=-\infty}^{\infty} \frac{1}{(4M+1)^2 Z_S[(4M+1)f_{LO}]}}, (M \neq 0),$$

(3.2)

which is a parallel combination of impedances, as shown in Fig. 3.3(c). Note that the harmonics index N in (3.1) is now replaced by 4M+1.  $Z_{\rm in,R}$  is the series combination of  $Z_{\rm in,M}$  and  $jX_{\rm LS}.$  For large values of |4M+1|, impedance term  $(4M+1)^2Z_{\rm S}[(4M+1)f_{\rm LO}]$  can be approximated as:

$$(4M+1)^2 Z_S[(4M+1)f_{LO}] \approx -j(4M+1)X_A + j(4M+1)^3 X_{LS},$$

(3.3)

which increases approximately proportionally to  $(4M+1)^3$ . In contrast, in the absence of  $L_S$ , (3.3) is only proportional to (4M+1). More importantly, with  $R_{SW}$  taken into account, (3.3) can be rewritten as:

$$(4M+1)^2 Z_S[(4M+1)f_{LO}] \approx -j(4M+1)X_A + (4M+1)^2 2R_{SW},$$

(3.4)

indicating that the impedance becomes resistive as |4M+1| increases. Consequently, the total effect presented by the mixer is a low quality

factor impedance. The above observation exhibits the main benefit of  $L_S$ , i.e., boosting the source impedance at  $f_{L0}$  harmonics and hence increasing the mixer input impedance at  $f_{L0}$ .

$Z_{\rm in,M}$  can be approximated by a few impedance terms for small values of |4M+1|. We use only the terms of M=-1 and M=1 to approximate the input impedance for developing insight, then more terms will be taken into account to provide more precise results. We thus have:

$$Z_{in,M} \approx 3^{2} Z_{S}(-3f_{LO}) || 5^{2} Z_{S}(5f_{LO})$$

$$= -j 11.43 X_{A} \frac{(1 - 8\alpha)(26\alpha - 1)}{1 - 69\alpha}, \tag{3.5}$$

where  $\alpha = X_{LS}/X_A$  is also the inductance ratio of  $L_S$  and  $L_A$ . We make the following observations here:

- 1. With improper values of  $X_A$  and  $X_{LS}$ , one of the parallel impedances in Fig. 3.3(c) could be zero (or very small). To avoid this,  $3^2Z_S(-3f_{LO})$  should be capacitive, i.e.,  $X_{LS}>0.125X_A$ . In such a condition, terms  $3^2Z_S(-3f_{LO})$ ,  $7^2Z_S(-7f_{LO})$ ... are all capacitive with their magnitudes increasing with harmonic index |4M+1|, while terms  $5^2Z_S(5f_{LO})$ ,  $9^2Z_S(9f_{LO})$ ... are all inductive with their magnitudes increasing with |4M+1|, and the total impedance  $Z_{in,M}$  is capacitive.

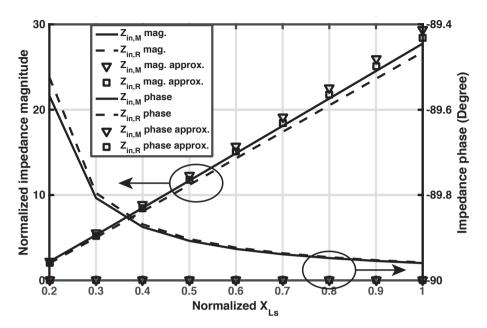

- 2.  $Z_{in,M}$  increases proportionally to  $\alpha$  as indicated by (3.5). This can be further illustrated by the precisely calculated relationship shown in Fig. 3.4, with all of the parallel impedances shown in Fig. 3.3(c) taken into account. Also, due to the high quality nature of the source impedance, the mixer input impedance is mainly capacitive. The approximated  $Z_{in,M}$  and  $Z_{in,R}$  using Equation (3.5) are plotted together with the precisely-calculated counterparts of Fig. 3.3(c) in Fig. 3.4 as well, suggesting a good approximation accuracy of Equation (3.5).

As the combined capacitive impedance of  $C_R$  and  $Z_{in,R}$  must be resonant with  $L_A$ , the question arises how the total desired capacitive impedance should be partitioned between  $Z_{in,R}$  and the impedance of  $C_R$ , i.e.,  $Z_{CR}$ =-j $X_{CR}$ . Since  $Z_{in,R}$  is strongly dependent on the value of  $L_S$ , it is desirable to make  $Z_{in,R}$  dominate the total impedance,

Figure 3.4: Precisely-calculated (Equation (3.2)) and approximated (Equation (3.5))  $Z_{in,M}$ , as well as  $Z_{in,R}$ , as a function of  $X_{LS}$ , with all the magnitudes normalized to  $X_A$ . These results are approximately the same for different values of quality factor  $Q_A$ , though  $Q_A=10$  ( $R_A=10$   $\Omega$ ,  $X_A=100$   $\Omega$ , at 403.5 MHz) has been taken as an example. This is because  $Z_S(Nf_{LO})$  has little dependence on  $Q_A$  as addressed by Eq. (3.1), and hence so do  $Z_{in,M}$  and  $Z_{in,R}$ .

thereby fully utilizing the effect of  $L_{\rm S}$ . However, the following example shows that the strong dependence of  $Z_{\rm in,M}$  upon  $Z_{\rm S}$  renders this infeasible. Suppose  $X_{\rm CR}$  is much greater than  $X_{\rm A}$ , e.g.,  $X_{\rm CR}{=}10X_{\rm A}$ , and  $L_{\rm S}{=}0.2L_{\rm A}$ . We repeat (3.1) and (3.5), resulting in the following impedances:

$$Z_{in,R} \approx 3^2 Z_S(-3f_{LO})||5^2 Z_S(5f_{LO}) + j0.2X_A$$

=  $-X_A(3.5 - 48.2j),$  (3.6)

$$Z_{CR}||Z_{in,R} = (0.1 - 8.4j)X_A. (3.7)$$

(3.6) suggests that  $Z_{in,R}$  is a complex high impedance (magnitude is around 5 times  $X_{CR}$ ), rather than a purely capacitive low impedance (magnitude is much smaller than  $X_{CR}$ ) as we wished.  $Z_{CR}||Z_{in,R}||$  is

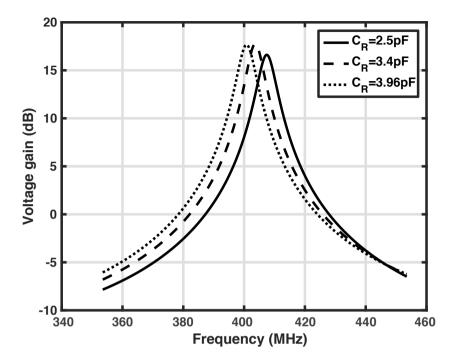

Figure 3.5: Voltage transfer function from the antenna source to the mixer input (voltage gain) in the vicinity of  $f_{LO}$ . Resonant frequency offset can be compensated for by tuning  $C_R$ . We assume the following simulation settings hereafter unless otherwise noted:  $R_A\!=\!10$   $\Omega,~X_A\!=\!100$   $\Omega$  ( $L_A\!=\!39.6$  nH),  $X_{LS}\!=\!0.5$   $X_A,~C_R\!=\!3.4$  pF,  $C_L\!=\!50$  pF,  $f_{LO}\!=\!403.5$  MHz, with ideal non-overlapping 25% duty-cycle quadrature signals, and the switch can switch instantaneously between on and off states with a on-resistance of  $R_{SW}\!=\!10$   $\Omega.$

therefore dominated by  $X_{CR}$  as shown by (3.7), yielding an impedance much higher than the required value of  $-jX_A$  for resonance at  $f_{LO}$ .

The above example suggests that  $-jX_{CR}$  should be chosen around the desired resonance impedance  $-jX_A$ , and  $L_S$  should be sufficient to make  $Z_{in,R}$  much greater than  $-jX_{CR}$ . A practical method to determine the component values is as follows. (1) Choose a sufficient  $L_S$  value according to Fig. 3.4. For example,  $L_S$ =0.5 $L_A$  offers a  $|Z_{in,R}|$  of 11.2 $X_A$ . (2) Reduce  $C_R$  to compensate for the resonance frequency shift, as illustrated by Fig. 3.5.

Having developed a good understanding of the mixer's impedance at the switching frequency, we now formulate the voltage conversion gain.  $Z_{CR}||Z_{in,R}$  should be designed to resonate with the antenna impedance  $R_A+jX_A$ , as discussed above. Since  $Z_{CR}||Z_{in,R}$  is a capacitive load with a negligible resistive part if  $R_{SW}$  is assumed to be zero, the resonant voltage across  $C_R$  is:

$$V_R = Q_A V_A. (3.8)$$

Considering the impedance ratio of  $jX_{LS}$  and  $Z_{in,M}$ , we get the voltage at the mixer's input:

$$V_{in,M} = \frac{Z_{in,M}}{Z_{in,M} + jX_{LS}} V_R.$$

(3.9)

As indicated by Fig. 3.4,  $Z_{in,M}$  is much greater than  $jX_{LS}$ , i.e., the ratio  $Z_{in,M}/(Z_{in,M}+jX_{LS})$  only varies from 1.1 to 1.04 if  $\alpha$  varies from 0.2 to 1. So the voltage drop across  $L_S$  is negligible. The voltage gain from mixer input to mixer output  $V_{OUT}$  is  $\sqrt{2}\pi/4$ , assuming Rsw=0 [19], and hence the conversion gain from  $V_A$  to  $V_{OUT}$  is:

$$G = \frac{V_{OUT}}{V_A} = Q_A \frac{\sqrt{2}\pi}{4}.$$

(3.10)

Although voltage is a more familiar quantity, the input of an antenna is actually a power quantity. The antenna input power can be transformed into a Thevenin equivalent peak voltage as [28]:

$$V_A = \sqrt{8R_A P_{av}},\tag{3.11}$$

where  $P_{av}$  is the available power of the antenna. Substituting (3.11) into (3.10) and expressing  $Q_A$  as  $X_A/R_A$ , we get the mixer's output peak voltage as a function of the input power:

$$V_{OUT} = \sqrt{8P_{av}} \frac{X_A}{\sqrt{R_A}} \frac{\sqrt{2}\pi}{4}.$$

(3.12)

The effect of  $R_A$  on  $V_{OUT}$  is a point of interest. For a given power  $P_{av}$ , although reducing  $R_A$  decreases  $V_A$ ,  $Q_A$  is increased to a greater extent, thereby increasing  $V_{OUT}$ . It is also instructive to contrast (3.12) with the same quantity of a PFE with the same passive mixer but with a standard 50  $\Omega$  antenna impedance (50  $\Omega$ -based counterpart). Assuming  $R_{SW}=0$ , the voltage at the input of the mixer can

be calculated with the aid of the model shown in Fig. 3.1(b), yielding  $V_{\rm in,M}=8V_A/\pi^2$ . Incorporating a voltage gain of  $\sqrt{2}\pi/4$  from the input of the mixer to its output and (3.11), the output peak voltage is:

$$V_{OUT} = \sqrt{8 \cdot 50 P_{av}} \frac{2\sqrt{2}}{\pi}.$$

(3.13)

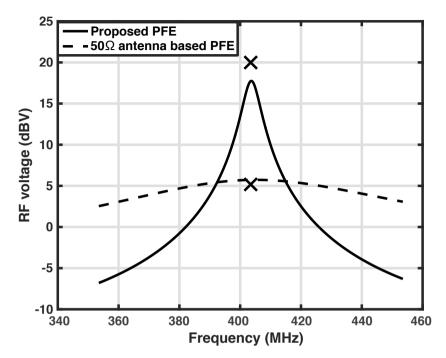

The contrast between (3.12) and (3.13) summarizes the benefits of the proposed PFE: (1) using an inductive antenna impedance, two extra degrees of freedom, i.e., R<sub>A</sub> and X<sub>A</sub> are introduced to increase V<sub>OUT</sub> for a given antenna available power; (2) the intermediate inductance L<sub>S</sub> increases the input impedance of the mixer considerably, thereby well maintaining the passive voltage gain offered by the passive network, i.e., Q<sub>A</sub>. Considering a PFE with an antenna impedance of (10+j100)  $\Omega$ , L<sub>S</sub>=0.5L<sub>A</sub> and R<sub>SW</sub>=10  $\Omega$ , Fig. 3.6 demonstrates that the PFE offers 12 dB higher peak RF voltage than its 50  $\Omega$ -based counterpart does for the same antenna available power. Note that the simulated 12 dB is smaller than the 14.8 dB difference between the calculated RF voltages using Equation (3.12) and (3.13) (excluding the conversion gain of  $\sqrt{2}\pi/4$  from the switch input to switch output for both), which are marked as "X" in Fig. 3.6. This discrepancy primarily arises from the presence of the 10  $\Omega$  switch resistance. We elaborate on the effect of the switch resistance in the following section.

#### 3.2.2 Effects of switch on-resistance

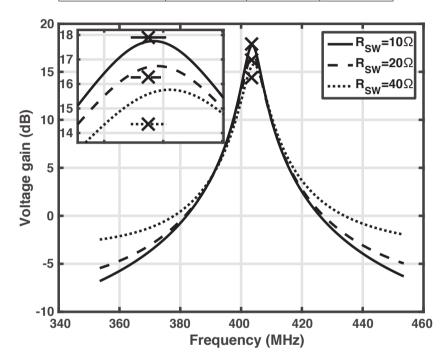

If  $R_{SW}$  is assumed to be zero,  $Z_{in,M}$  is almost capacitive with a very high quality factor as shown by Fig. 3.4. The presence of the on-resistance gives rise to the addition of a resistive part to each of the parallel impedances shown in Fig. 3.3(c) and Equation (3.2), thereby reducing the quality factor of  $Z_{in,M}$ . Consequently, the RF voltage gain offered by the passive network is reduced due to the limited quality factor of  $Z_{in,M}$ . Considering  $R_A$ =10  $\Omega$ ,  $L_A$ =39.6 nH ( $X_A$ =100  $\Omega$  at 403.5 MHz),  $L_S$ =0.5 $L_A$  and  $L_S$ =3.4 pF (to resonate at 403.5 MHz as indicated by Fig. 3.5), the calculated  $L_{in,M}$  using Equation (3.2) and the resulting  $L_{in,R}$  and  $L_{in,R}$  are shown in Table 3.1 for several  $L_S$  values. The quality factor of the resonance impedance  $L_S$  decreases with increasing  $L_S$ , thereby reducing the passive voltage gain, as shown by the simulation results depicted in Fig. 3.7. Note that, as  $L_S$

Figure 3.6: RF voltage at the mixer input of the proposed PFE and its 50  $\Omega$ -based counterpart for a given antenna available power.  $P_{av}=10.98$  dBm. The approximated RF voltages using Equation (3.12) and (3.13) (excluding the conversion gain of  $\sqrt{2}\pi/4$  from the switch input to switch output for both) are marked by "X".

increases, the discrepancy between the simulated gain and calculated gain shown in Fig. 3.7 increases, suggesting the model of Fig. 3.3(c) becomes less accurate. This is because the source models (dashed blocks) in Fig. 3.3(b) and (c) ignore the impedance term  $Z_{\rm S}(f_{\rm in})||2R_{\rm SW}$  (of the original model shown in Fig. 3.1(b)) due to the assumption of  $R_{\rm SW}{=}0~\Omega,$  and this impedance term becomes more pronounced as  $R_{\rm SW}$  increases, thereby causing the discrepancy. Nevertheless, the model shown in Fig. 3.3(c) incorporates the physical model of the passive network and hence is easier than the mathematical model (shown in Fig. 3.1(b)) to develop design insight.

This impact of  $R_{SW}$  can be compensated for by increasing the quality factor of each parallel element in Fig. 3.3(c), i.e., increasing  $L_S$ . The conversion gain from the input of the mixer to its output is also reduced because of the voltage drop over the switch [19]. However,

Table 3.1: Calculated  $Z_{in,M}$ ,  $Z_{in,R}$  and  $Z_{in,R}||Z_{CR}$  at LO frequency (403.5 MHz) as a function of  $R_{SW}$ .

| $R_{SW}(\Omega)$                    | 10        | 20       | 40       |

|-------------------------------------|-----------|----------|----------|

| $Z_{\mathrm{in,M}}(\Omega)$         | 303-j1027 | 559-j905 | 909-j590 |

| $Z_{in,R}(\Omega)$                  | 303-j976  | 559-j854 | 909-j539 |

| $Z_{\rm in,R}  Z_{\rm CR}(\Omega) $ | 3-j105    | 6-j106   | 10-j109  |

Figure 3.7: The effect of  $R_{SW}$  on the peak RF gain of the proposed PFE. The calculated peak gains using the model shown in Fig. 3.3(c) and the impedances in Table 3.1 are marked by "X" and the corresponding line styles.

this effect is negligible for the proposed front-end since  $Z_S$  and  $Z_{in,M}$  are much greater than  $R_{SW}$  in a proper design.

## 3.2.3 Bandwidth

For the same  $R_{SW}$  and load capacitance  $C_L$ , the proposed front-end presents a narrower bandwidth with respect to its counterpart based

on a 50  $\Omega$  antenna impedance. We consider the model in Fig. 3.1(b) for comparing the two topologies. For frequencies further away from  $f_{LO}$ , all of the parallel terms  $(4M+1)^2[Z_S(f_{in}+4Mf_{LO})+2R_{SW}]$  can be omitted because  $Z_L(f_{in}-f_{LO})$  dominates. We also assume  $2R_{SW}\ll Z_S(f_{in})$ . Thus, in order to compare the input voltage of the mixer in the two topologies, we now only need to compare the equivalent Norton source  $I_{in}(f)$ . While  $I_{in}(f)$  is independent of frequency for the case of a 50  $\Omega$  antenna,  $I_{in}(f)$  of the proposed topology experiences a third-order ( $L_A$ ,  $C_R$  and  $L_S$ ) filtering when the physical model in Fig. 3.3(a) is transformed into its Norton counterpart. The proposed topology therefore offers more suppression at frequencies further away from  $f_{LO}$  than the 50  $\Omega$ -based counterpart does. In other words, apart from the upconverted filtering effect of  $C_L$ , the bandwidth of the proposed topology is also narrowed by the passive network. The difference addressed above is also illustrated by the simulation results shown in Fig 3.6.

## 3.2.4 Noise analysis

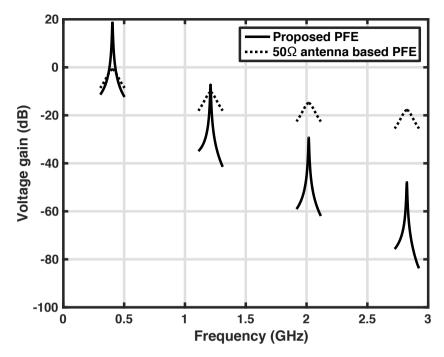

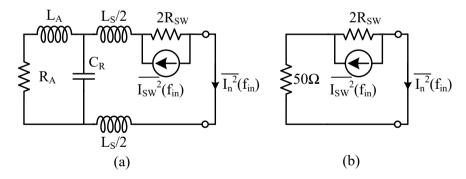

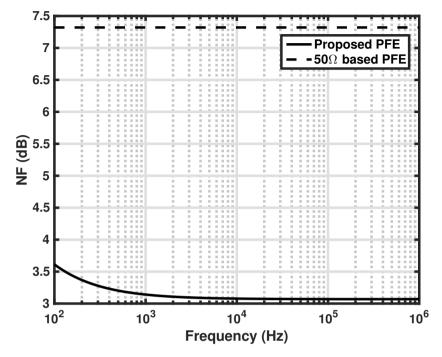

Noise folding is the main noise degradation mechanism for a passive mixer. The proposed PFE presents interesting reduction of the noise folding effect. We analyze the noise behavior of the proposed PFE with respect to a 50  $\Omega$  based PFE. The improvement is demonstrated using a simple and qualitative approach, avoiding exhaustive analysis.

We consider the model shown in Fig. 3.8(a) for noise analysis. The input noise source and the source impedance are represented in the form of a Norton equivalent, and the switch resistance is merged with the source impedance. For an input noise current around  $f_{LO}$ , assume its transimpedance gain to baseband output is  $A_R$ . We also have that the noise around the Nth harmonic of  $f_{LO}$  (N is an odd integer) folds down with a gain related to  $A_R$ , i.e.,  $A_R/N$  [19,21]. The relative contribution of the noise folding effect (i.e., NF) can be analyzed by finding the Norton equivalent noise current  $\overline{I_n^2}(f_{in})$  around the Nth harmonic of  $f_{LO}$ . We use the circuitry in Fig. 3.8(b) and (c) to do so for the proposed topology and its  $50\Omega$ -based counterpart, respectively. Let's consider a noise voltage source around the Nth harmonic of  $f_{LO}$  (|N| > 1),  $\overline{V_n^2}(f_{in})$ . The short-circuit noise current and hence the value of the Norton noise current source  $\overline{I_n^2}(f_{in})$  in Fig. 3.8(c) is simply  $\overline{V_n^2}(f_{in})/50^2$ . In contrast, the  $R_A$ - $L_A$ - $C_R$ - $L_S$  network in Fig. 3.8 (b)

Figure 3.8: (a) Representing the input noise and switch noise as a Norton equivalent. (b) Circuitry for finding the Norton noise current source  $\overline{I_n^2}(f_{in})$  of the proposed PFE, and (c) its 50  $\Omega$ -based counterpart.

provides third-order filtering, and L<sub>S</sub> has a high impedance, so  $\overline{I_n^2}(f_{in})$  in Fig. 3.8 (b) is less than the one found in (c), and more importantly decreases with N. Thus, the proposed PFE significantly reduces the noise folding with respect to its 50  $\Omega$ -based counterpart, as further evidenced by the simulation results in Fig. 3.9.

The above noise analysis technique applies to switch thermal noise as well, as illustrated in Fig. 3.10.  $\overline{I_n^2}(f_{in})$  in Fig. 3.10(b) is a frequency independent current which is determined by the ratio between  $R_{SW}$  and 50  $\Omega$ . In contrast, since the source impedance in Fig. 3.10(a) increases with frequency, and is much greater than 50  $\Omega$ ,  $\overline{I_n^2}(f_{in})$  in Fig. 3.10(a) is much less than that in Fig. 3.10(b) and decreases with frequency. Hence, the thermal noise of the switch resistance can also be significantly suppressed by the proposed network in front of the mixer. This allows us to use small size switches to reduce the driving power of clock signals while retaining sufficient NF. The NF comparison of the two topologies is depicted in Fig. 3.11. Due to the reduction of noise folding, the proposed topology improves NF significantly (around 4.2 dB in the example of Fig. 3.11).

Although flicker noise contributes much less than thermal noise does in both PFEs, as shown in Fig 3.11, it appears that the flicker noise behavior of the proposed PFE is more pronounced than that of its 50  $\Omega$ -based counterpart. This could be understood with the aid of two popular explanations for the flicker noise mechanism of a passive mixer [49–51] as follows. The slowly varying gate-referred flicker

Figure 3.9: Desired signal transfer from  $f_{LO}$  to baseband and unwanted foldings from  $3f_{LO}$ ,  $5f_{LO}$  and  $7f_{LO}$  to baseband for the proposed PFE and its  $50~\Omega$ -based counterpart.

Figure 3.10: Circuitry for finding the Norton noise current source  $\overline{I_n^2}(f_{in})$  of the switch thermal noise for (a) the proposed PFE, and (b) its 50  $\Omega$ -based counterpart.

noise randomly modulates the commutation instant which is ideally located at the zero crossings of the LO. This modulation results in a train of noise pulses which add to the ideal square-wave commu-

Figure 3.11: NF comparison of the proposed PFE and a 50  $\Omega$ -based PFE. The switch is implemented by a realistic MOSFET with a  $R_{SW}$  around 50  $\Omega$ . The driving clock is considered to be noiseless.

tation waveform, and as a consequence, flicker noise appears at the output [49, 50]. Thus, the output flicker noise is proportional to the amount of input RF current to the passive mixer. As described in Section 3.2.1, for the same output capacitance, the proposed PFE delivers more output voltage than its 50  $\Omega$ -based counterpart, indicating that the former also has larger noise current at the input of the switches than the latter, thus more output flicker noise. Another explanation of the flicker noise mechanism is presented in [51], where the current due to the capacitive coupling of the large LO voltage to the drain nodes of the switches is said to be responsible for transferring the switch flicker noise to the output. In the proposed PFE, owing to the high impedance presented by the passive network at the drain nodes of the switches, the large LO voltage produces considerable voltage fluctuations at the drain nodes. These voltage fluctuations give rise to a non-zero-mean current in the channel of the switch, and hence the flicker noise of the switch manifests itself at the output. This effect is

Figure 3.12: System diagram of the proposed PFE and a baseband LNA.

much less pronounced in the 50  $\Omega$ -based counterpart because 50  $\Omega$  is a very small wideband impedance in comparison with the impedance of the proposed passive network. Since the flicker noise of the mixer does not dominate the noise performance of the proposed PFE, we rely on the above two qualitative explanations to develop insight in the design process, thereby avoiding exhaustive analysis.

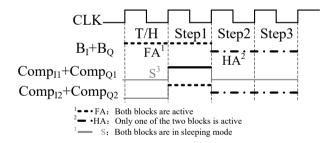

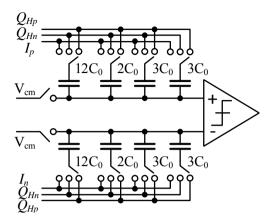

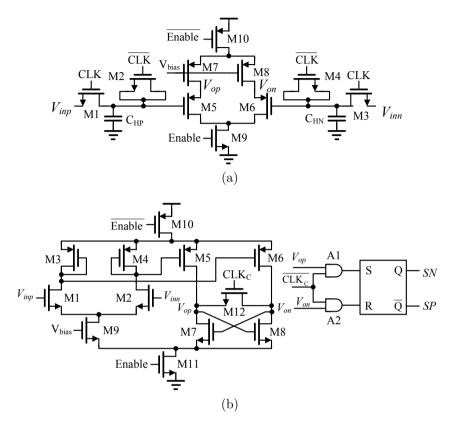

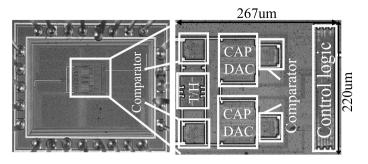

## 3.3 Passive front-end implementation