# Cryogenic-Aware Forward Body Biasing in Bulk CMOS

Overwater, Ramon W.J.; Babaie, Masoud; Sebastiano, Fabio

10.1109/LED.2023.3337441

**Publication date**

**Document Version** Final published version

Published in **IEEE Electron Device Letters**

Citation (APA)

Overwater, R. W. J., Babaie, M., & Sebastiano, F. (2023). Cryogenic-Aware Forward Body Biasing in Bulk CMOS. *IEEE Electron Device Letters*, *45*(2), 152-155. https://doi.org/10.1109/LED.2023.3337441

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Cryogenic-Aware Forward Body Biasing in Bulk CMOS

Ramon W. J. Overwater<sup>®</sup>, Masoud Babaie<sup>®</sup>, Senior Member, IEEE, and Fabio Sebastiano<sup>®</sup>, Senior Member, IEEE

Abstract—Cryogenic CMOS (cryo-CMOS) are often hindered by the cryogenic threshold-voltage increase. To mitigate such an increase, a forward body biasing (FBB) technique in bulk CMOS is proposed, which can operate up to the nominal supply without problematic leakage currents, thanks to the larger diode turn-on voltage at cryogenic temperatures. As a result, traditional circuits, such as pass-gates, can operate down to 4.2 K, and their performance is augmented, e.g., digital circuits speeding up by 1.62x or lowering their energy per transition and energy-delay product by 4.24x and 2.33x, respectively. Unlike back biasing in FD-SOI, here all FBB voltages remain within the supplies, hence enabling on-chip and device-specific biasing. The proposed FBB technique thus represents a valuable design tool for bulk cryo-CMOS circuits.

Index Terms—Cryo-CMOS, body biasing, bulk CMOS.

#### I. INTRODUCTION

POR several low-temperature applications, such as quantum computing, space exploration, and cryogenic computing, CMOS electronics operating at cryogenic temperatures (cryo-CMOS) have been proposed as an enabling technology [1], [2], [3], [4]. The development of the high-performance, low-power circuits required in these applications favors its unrivaled VLSI capability combined with improved device performance at cryogenic temperatures, e.g., the increased carrier mobility [5], the lower thermal noise [6], the steeper subthreshold slope (SS) [5], the reduced metal resistances and the higher quality factor of passives [7]. Despite these advantages, the significant increase in threshold voltage  $V_{th}$ (up to 180 mV at 4.2 K [8]) constitutes a big obstacle for circuit design, for instance, heavily hindering the increase in drive current induced by the enhanced mobility, and limiting the allowed voltage swing in commonly adopted circuits, such as sample-and-hold [9], [10]. Designers can counteract the increased  $V_{th}$  using more complex circuits, inevitably costing performance and/or power.

Manuscript received 8 November 2023; revised 21 November 2023; accepted 26 November 2023. Date of publication 29 November 2023; date of current version 29 January 2024. This work was supported by Intel. The review of this letter was arranged by Editor K. J. Kuhn. (Corresponding author: Ramon W. J. Overwater.)

Ramon W. J. Overwater and Fabio Sebastiano are with the Department of Quantum and Computing Engineering and QuTech, TU Delft, 2628 CD Delft, The Netherlands (e-mail: r.w.j.overwater@tudelft.nl).

Masoud Babaie is with the Department of Microelectronics and QuTech, TU Delft, 2628 CD Delft, The Netherlands.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2023.3337441.

Digital Object Identifier 10.1109/LED.2023.3337441

To alleviate these setbacks, the MOS channel doping could be optimized for cryogenic operation, thus precluding wide-temperature operation and adding fabrication costs. Adopting an FD-SOI technology in combination with back-biasing to tune the  $V_{th}$  can drastically improve cryogenic performance [11]. However, in addition to the higher cost of FD-SOI with respect to bulk CMOS, tuning the  $V_{th}$  back to its room-temperature value requires biasing the back gate well beyond the process nominal supply due to the low body factor in FD-SOI technologies, e.g., requiring beyond 2 V for the back gate to compensate the  $V_{th}$  shift for a body-factor of 0.085 V/V [11], [12], [13]. As a consequence, either high-voltage on-chip generators would be required, increasing power consumption and complexity, or the back-bias voltages need to be delivered from off-chip. As an alternative, we propose using cryogenic-aware forward body biasing (FBB) in bulk CMOS. As the body factor in bulk CMOS is significantly larger, the required body bias voltage is lower [14]. However, a large body-source voltage could turn on the source-bulk diodes, leading to massive unwanted leakage currents. While this is a known hard limit at room temperature, the diode turn-on voltage increases beyond the supply rails at cryogenic temperatures [15], [16], thus potentially preventing the leakage. Recent work [17] has already shown an improvement in reliability down to 80 K and FBB voltages only up to 0.5 V. However, the proposed technique demonstrates, for the first time, the full potential of FBB for cryogenic low-power and high-performance bulk CMOS designs by presenting its experimental characterization and validation for both devices and circuits.

## II. CRYOGENIC-AWARE FBB CHARACTERIZATION

A 40-nm LP triple-well CMOS test chip has been fabricated, comprising both standard- and low- $V_{th}$  (SVT/LVT) transistors, and ring oscillators (ROs) to test the performance of digital circuits. All 384 transistors are connected in parallel and share the Kelvin-connected source and drain connections, but their gates are individually switchable to  $V_g$  or  $V_s$  by a thick-oxide switch. They have been characterized with Keysight 2636B SMUs and their threshold is extracted using the maximum  $g_m$  method at  $V_{DS} = 50$  mV [18]. Each RO consists of N = 1025 inverters and an enabling thick-oxide switch in series. Of the 144 ROs, 116 have varying widths and minimum length (40 nm). The others have minimum width (120 nm) and lengths between 45 nm and 120 nm. The oscillators' output frequency is measured with a Rigol DSA815 spectrum analyzer, while simultaneously measuring their supply and body bias currents using the SMUs. The transition time of

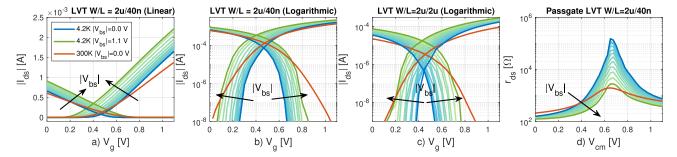

Fig. 1. DC measurements of LVT NMOS/PMOS devices at 300 K (red line) and 4.2 K (green to blue lines). For the 4.2-K results, the body-biasing  $|V_{bs}|$  is swept from 0 V to 1.1 V in steps of 0.1 V (shades). To improve readability, the leakage is subtracted. The NMOS source is grounded, and the PMOS source is connected to  $V_{dd}=1.1$  V. (a-b)  $I_{ds}/V_g$  at  $|V_{ds}|=1.1$  V for  $W/L=2\mu m/40$ nm in linear and semi-logarithmic scale. (c)  $W/L=2\mu m/2\mu m$  in semi-logarithmic scale. (d) Small-signal resistance of the pass gate vs. the voltage applied on the drain/source, obtained by numerically combining in parallel the individually measured NMOS and PMOS resistance of (a-b).

a single stage  $t_d = 1/(2Nf)$  is computed from the frequency, and is combined with the total RO power  $(P = V_{dd} \cdot I)$  to obtain the energy per transition (EPT =  $P \cdot t_d$ ) and energy-delay product (EDP =  $P \cdot t_d^2$ ). The 4.2-K data was obtained by submerging the chip into liquid helium inside a dewar using a dipstick.

#### A. Transistor Static Characteristics

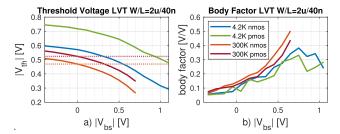

Figure 1a and b show the  $I_{ds}/V_g$  curves of a single minimum-length NMOS and PMOS device. To improve the readability of Fig. 1, the leakage current of all parallel transistors with  $V_{gs} = 0$  V is subtracted in the plots. As expected and highlighted in Fig. 2a, the  $V_{th}$  increases when cooling down. FBB can reduce the 4.2-K  $V_{th}$  even below its roomtemperature value, although it is less effective for the PMOS due to its larger  $V_{th}$  shift [8]. The body-factor,  $\eta = \partial V_{th}/\partial V_{bs}$ in Fig. 2b, only depends on  $V_{bs}$  and the doping level, but it is approximately independent of temperature. A similar invariance was found for longer devices ( $L = 2\mu m$ ). This indicates that a relatively high room-temperature body-factor is a good predictor of the suitability of the proposed technique for a given technology. For longer devices, however, the thresholds remain higher (Fig. 1c) due to the reduced DIBL effect and the ratio between the bulk diode leakage and drain current will be larger. The transistor  $|I_{ds}|$  leakage at 4.2 K is lower than room temperature (see Fig. 1b and c) due to the steeper SS even for full FBB  $|V_{bs}| = V_{dd}$ , i.e., the N-well (P-well) to  $V_{ss}$  ( $V_{dd}$ ), while the maximum current at  $V_{gs} = V_{dd}$  is always higher at 4.2 K thanks to the higher mobility (see Fig. 1a).

#### B. Pass Gates

Pass gates, i.e., switches consisting of a PMOS and an NMOS in parallel, are problematic at cryogenic temperatures, as they exhibit high resistance around mid-rail due to the steeper SS and higher  $V_{th}$  [10]. Fig. 1d shows that with FBB, the pass-gate resistance is returned to levels similar to 300 K, thus proving its restored functionality. At 4.2 K, the curves are shifted to the right compared to 300 K, confirming that the NMOS threshold is less affected by cooling than the PMOS.

## C. Ring Oscillators

In cryogenic digital circuits, FBB brings the opportunity to significantly reduce the dynamic power by simultaneously reducing both the  $V_{th}$  and  $V_{dd}$ . In addition, the steep SS

Fig. 2. (a) Threshold voltage at 4.2 K and 300 K of both an NMOS and PMOS LVT  $W/L = 2\mu \text{m}/40\text{nm}$  device at  $|V_{ds}| = 50$  mV when applying body biasing. The dashed line indicates the 300-K threshold without body biasing. (b) The extracted body factor. At 300 K,  $|V_{bs}|$  is limited to 0.7 V due to the bulk diodes turning on.

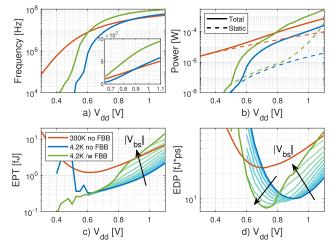

Fig. 3. Measured ring oscillator. (a) Frequency (inset in linear scale), (b) power, (c) energy per transition (EPT), (d) and energy-delay product (EDP). The RO consist of 1025 drive-1 LVT inverters and is measured at 300 K (red lines) and 4.2 K (blue to green lines). For 4.2 K,  $|V_{bs}|$  increases from 0 V (blue) to  $V_{dd}$  (green) in steps of 0.1 V (shades).

at cryogenic temperature mitigates the leakage induced by this lower  $V_{th}$ . A second improvement is the logic speed-up induced by the increased mobility at cryogenic temperature compared to room temperature. While older technologies achieve > 1.6× speed-up when cooled down, the speed-up for modern technologies is limited by the increased  $V_{th}$  constraining the drive current [10]. FBB should alleviate this limitation, thus bringing back the traditional speed-up. The logic performance is assessed by characterizing a ring oscillator with standard drive-1 (D1) LVT inverters (Fig. 3). For these measurements, we focus mostly on full FBB ( $|V_{bs}| = V_{dd}$ )

TABLE I

A SUMMARY OF THE IMPORTANT QUANTITATIVE METRICS FOR THE RO

| $T$ $V_{dd}$ FBB | [K]<br>[V]                      | 300<br>1.1<br>No | 4.2<br>1.1<br>No | 4.2<br>0.9<br>No | 4.2<br>1.1<br>Full | 4.2<br>0.725<br>Full |

|------------------|---------------------------------|------------------|------------------|------------------|--------------------|----------------------|

| f                | [MHz]                           | 50.8             | 58.7             | 34.0             | 95.0               | 32.2                 |

| $\tilde{P}$      | $[\mu W]$                       | 724              | 265              | 50.4             | 2844               | 34.2                 |

| EPT              | [fJ]                            | 6.95             | 2.20             | 0.723            | 14.6               | 0.518                |

| EDP              | $[\mathrm{fJ}\cdot\mathrm{ps}]$ | 57.7             | 18.0             | 10.1             | 64.4               | 7.74                 |

as this is a very practical case not requiring any additional biasing/supply voltage other than  $V_{dd}$  and  $V_{ss}$ . However, it is important to note that  $V_{dd}$  is now being swept. In Fig. 3a, the RO frequency shows a speed-up of 1.16× when cooling down, which increases to 1.87× when applying full FBB, thus aligning with the expectations based on [10]. The plot also clearly shows that FBB lowers the minimum  $V_{dd}$  at which the oscillator still works. Figure 3b shows two interesting findings for the power consumed by the ROs. First, a large reduction in static power is induced by the lower leakage at 4.2 K, which significantly increases with FBB. Second, the power consumption with FBB has a step-like increase above  $V_{dd} = 0.8$  V. Since this also corresponds to an increase of the EPT and EDP (Fig. 3c,d), the power increases more than the frequency. This is likely due to the lower  $V_{th}$  causing an increase in the inverter short-circuit current when both NMOS and PMOS conduct. Next, Fig. 3c shows that the EPT does not benefit from FBB. This is expected as the EPT is limited by  $CV_{dd}^2$  when neglecting the short-circuit current. FBB does however increase the frequency, causing the minimum EDP in Fig. 3d to lower from 10.1 fJ·ps without FBB to 7.7 fJ·ps with FBB. While this is similar to the results for 28-nm FD-SOI [11], the proposed technique avoids the backbias voltages exceeding 4 V in prior works. An interesting difference appears in Fig. 3d above and below  $V_{dd} = 0.9 \text{ V}$ when applying FBB. Above 0.9 V, FBB increases the EDP, while it lowers it below 0.9 V. This is mainly attributed to the optimal  $V_{dd}$  point shifting to lower  $V_{dd}$  for increasing FBB. A summary of the RO results mentioned above is shown in Table I.

#### D. Bulk Diode Leakage

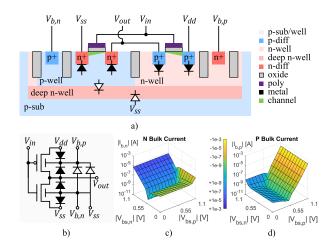

Although FBB forces parasitic diodes in forward conduction (Fig. 4a,b), the diode built-in voltage  $V_{bi} = E_g - k_B T/q$ .  $\ln \left[ (N_C N_V) / (N_A^- N_D^+) \right]$  increases well beyond 1.1 V due to the increase in the bandgap  $E_g$  and lower  $k_BT/q$  at cryogenic temperatures [19]. This, in combination with the steeper Fermi function, which requires the applied voltage to be closer to  $V_{bi}$  before conduction starts, makes the leakage via the body terminals negligible at 4.2 K. To verify this, Fig. 4c,d show the combined bulk leakage of the 144 1025-stage on-chip ring oscillators for various FBB voltages at  $V_{dd} = 1.1$  V. If the well-to-well leakage were dominant (white diodes in Fig. 4a,b), the N and P bulk currents should be similar. However, since the NMOS and PMOS body current shows a dominant exponential dependence on their respective body voltage, the leakage is mainly attributed to the source/drain-to-well diodes (black diodes in Fig. 4a,b). Interestingly, the leakage changes sign for FBB around mid-supply and shows dependence on the opposite FBB voltage. This may be due to the gate leakage being affected by the FBB-tuned threshold. Normalizing the bulk current at full FBB for

Fig. 4. (a) Simplified cross-section of a body-biased inverter in a triple-well process; the well-to-well diodes and drain/source-to-well diodes are drawn in white and black, respectively. (b) Inverter schematic. (c) NMOS and (d) PMOS body currents for all 144 ROs for  $V_{dd} = 1.1 \text{ V}$  at 4.2K.

1.1 V supply to the total combined transistor widths results in 64.1 pA/ $\mu$ m (1.32 nA/ $\mu$ m) for NMOS (PMOS). This difference is ascribed to the difference in doping. Using those factors and the sizing of the D1 LVT RO and  $V_{dd}=1.1$ V, results in a bulk leakage power of 632.6 nW at 1.1 V, which is negligible as it is almost 5000 times lower than the total power (2844  $\mu$ W). Even for much lower dynamic power, e.g. lower activity factor or longer devices, the bulk leakage would be negligible. Still, it might be preferable to switch the body voltage for inactive circuits. Additionally, at a lower supply, leakage will further decrease due to the exponential dependence on the bias voltages.

#### E. Proposed Cryogenic Design Guidelines

Based on our results, we suggest adopting cryogenic-aware FBB to LVT devices from a bulk CMOS technology with sufficiently high room-temperature body-factor. For pass-gates and high-performance or low-power digital, we suggest applying full FBB. High-performance digital circuits should remain at nominal supply, however, lowering the supply in low-power digital circuits contributes to reducing the EDP. For the LVT D1 RO in our specific technology, this means that for low-power designs the supply should be lowered to 0.725 V with full FBB, yielding an EPT / EDP reduction of  $4.24 \times$  / 2.33×, while only reducing speed by 1.82× compared to  $V_{dd} = 1.1 \text{ V}$  without FBB at 4.2 K. For high-performance designs, at  $V_{dd} = 1.1 \text{ V}$  applying full FBB results in a frequency increase of 1.62× with an EDP comparable to 300 K. Here, the leakage increases mainly due to the short circuit current, the bulk leakage power is only 0.02% of the total power.

#### III. CONCLUSION

The presented experimental validation shows that FBB can be applied in bulk cryo-CMOS devices and circuits with negligible leakage, even with full FBB, i.e., the N-well (P-well) to  $V_{ss}$  ( $V_{dd}$ ). The proposed cryogenic-aware FBB technique can compensate for the cryogenic  $V_{th}$  shift without requiring beyond-supply voltages, thus enabling the operation of circuit topologies otherwise unusable at cryogenic temperatures, such as pass gates. In digital circuits, applying FBB can increase the speed of high-performance circuits by  $1.62\times$  or reduce the EPT by  $4.24\times$  and the EDP by  $2.32\times$  for low-power circuits.

#### REFERENCES

- [1] J. C. Bardin, E. Jeffrey, E. Lucero, T. Huang, S. Das, D. T. Sank, O. Naaman, A. E. Megrant, R. Barends, T. White, M. Giustina, K. J. Satzinger, K. Arya, P. Roushan, B. Chiaro, J. Kelly, Z. Chen, B. Burkett, Y. Chen, A. Dunsworth, A. Fowler, B. Foxen, C. Gidney, R. Graff, P. Klimov, J. Mutus, M. J. McEwen, M. Neeley, C. J. Neill, C. Quintana, A. Vainsencher, H. Neven, and J. Martinis, "Design and characterization of a 28-nm bulk-CMOS cryogenic quantum controller dissipating less than 2 mW at 3 K," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3043–3060, Nov. 2019, doi: 10.1109/JSSC.2019.2937234.

- [2] J. Park, S. Subramanian, L. Lampert, T. Mladenov, I. Klotchkov, D. J. Kurian, E. Juarez-Hernandez, B. P. Esparza, S. R. Kale, S. P. Premaratne, T. F. Watson, S. Suzuki, M. Rahman, J. B. Timbadiya, S. Soni, and S. Pellerano, "A fully integrated cryo-CMOS SoC for state manipulation, readout, and high-speed gate pulsing of spin qubits," *IEEE J. Solid-State Circuits*, vol. 56, no. 11, pp. 3289–3306, Nov. 2021, doi: 10.1109/JSSC.2021.3115988.

- [3] B. Patra, R. M. Incandela, J. P. G. van Dijk, H. A. R. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, "Cryo-CMOS circuits and systems for quantum computing applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 1, pp. 309–321, Jan. 2018, doi: 10.1109/JSSC.2017.2737549.

- [4] J. Anders, M. Babaie, J. C. Bardin, I. Bashir, G. Billiot, E. Blokhina, S. Bonen, E. Charbon, J. Chiaverini, I. L. Chuang, C. Degenhardt, D. Englund, L. Geck, L. Le Guevel, D. Ham, R. Han, M. I. Ibrahim, D. Krüger, K. M. Lei, A. Morel, D. Nielinger, G. Pillonnet, J. M. Sage, F. Sebastiano, R. B. Staszewski, J. Stuart, A. Vladimirescu, P. Vliex, and S. P. Voinigescu, "CMOS integrated circuits for the quantum information sciences," *IEEE Trans. Quantum Eng.*, vol. 4, pp. 1–30, Jul. 2023, doi: 10.1109/TQE.2023.3290593.

- [5] A. Beckers, F. Jazaeri, and C. Enz, "Characterization and modeling of 28-nm bulk CMOS technology down to 4.2 K," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 1007–1018, Mar. 2018, doi: 10.1109/JEDS.2018.2817458.

- [6] A. H. Coskun and J. C. Bardin, "Cryogenic small-signal and noise performance of 32nm SOI CMOS," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2014, pp. 1–4, doi: 10.1109/MWSYM.2014.6848614.

- [7] B. Patra, M. Mehrpoo, A. Ruffino, F. Sebastiano, E. Charbon, and M. Babaie, "Characterization and analysis of on-chip microwave passive components at cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 448–456, Apr. 2020, doi: 10.1109/JEDS.2020.2986722.

- [8] P. A. 'T Hart, M. Babaie, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and modeling of mismatch in cryo-CMOS," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 263–273, Feb. 2020, doi: 10.1109/JEDS.2020.2976546.

- [9] G. Kiene, R. W. J. Overwater, A. Catania, A. G. Sreenivasulu, P. Bruschi, E. Charbon, M. Babaie, and F. Sebastiano, "A 1-GS/s 6–8-b cryo-CMOS SAR ADC for quantum computing," *IEEE J. Solid-State Circuits*, vol. 58, no. 7, pp. 2016–2027, Feb. 2023, doi: 10.1109/JSSC.2023.3237603.

- [10] J. van Dijk, P. Hart, G. Kiene, R. Overwater, P. Padalia, J. van Staveren, M. Babaie, A. Vladimirescu, E. Charbon, and F. Sebastiano, "Cryo-CMOS for analog/mixed-signal circuits and systems," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Mar. 2020, pp. 1–8, doi: 10.1109/CICC48029.2020.9075882.

- [11] H. Bohuslavskyi, S. Barraud, V. Barral, M. Cassé, L. Le Guevel, L. Hutin, B. Bertrand, A. Crippa, X. Jehl, G. Pillonnet, A. G. M. Jansen, F. Arnaud, P. Galy, R. Maurand, S. De Franceschi, M. Sanquer, and M. Vinet, "Cryogenic characterization of 28-nm FD-SOI ring oscillators with energy efficiency optimization," *IEEE Trans. Electron Devices*, vol. 65, no. 9, pp. 3682–3688, Sep. 2018, doi: 10.1109/TED.2018.2859636.

- [12] P. Flatresse, B. Giraud, J.-P. Noel, B. Pelloux-Prayer, F. Giner, D.-K. Arora, F. Arnaud, N. Planes, J. Le Coz, O. Thomas, S. Engels, G. Cesana, R. Wilson, and P. Urard, "Ultra-wide body-bias range LDPC decoder in 28nm UTBB FDSOI technology," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 424–425, doi: 10.1109/ISSCC.2013.6487798.

- [13] B. Cardoso Paz, M. Cassé, C. Theodorou, G. Ghibaudo, T. Kammler, L. Pirro, M. Vinet, S. de Franceschi, T. Meunier, and F. Gaillard, "Performance and low-frequency noise of 22-nm FDSOI down to 4.2 K for cryogenic applications," *IEEE Trans. Electron Devices*, vol. 67, no. 11, pp. 4563–4567, Nov. 2020, doi: 10.1109/TED.2020. 3021999.

- [14] A. Hokazono, S. Balasubramanian, K. Ishimaru, H. Ishiuchi, C. Hu, and T.-J.-K. Liu, "Forward body biasing as a bulk-Si CMOS technology scaling strategy," *IEEE Trans. Electron Devices*, vol. 55, no. 10, pp. 2657–2664, Oct. 2008, doi: 10.1109/TED.2008. 2003029.

- [15] P. A. T Hart, M. Babaie, A. Vladimirescu, and F. Sebastiano, "Characterization and modeling of self-heating in nanometer bulk-CMOS at cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 891–901, Oct. 2021, doi: 10.1109/JEDS.2021. 3116975.

- [16] P. A. I. Hart, T. Huizinga, M. Babaie, A. Vladimirescu, and F. Sebastiano, "Integrated cryo-CMOS temperature sensors for quantum control ICs," in *Proc. IEEE 15th Workshop Low Temp. Electron. (WOLTE)*, Jun. 2022, pp. 1–4, doi: 10.1109/wolte55422.2022.9882600.

- [17] H. You, J. An, K. Nam, B. Kang, J. Park, N. Lee, S. Lee, and R.-H. Baek, "Forward body bias technique in DRAM peripheral transistor at cryogenic temperature for quantum computing applications," in *Proc. 7th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Mar. 2023, pp. 1–3, doi: 10.1109/EDTM55494.2023.10102979.

- [18] A. Ortiz-Conde, F. J. García-Sánchez, J. Muci, A. T. Barrios, J. J. Liou, and C.-S. Ho, "Revisiting MOSFET threshold voltage extraction methods," *Microelectron. Rel.*, vol. 53, no. 1, pp. 90–104, Jan. 2013, doi: 10.1016/j.microrel.2012.09.015.

- [19] Y. P. Varshni, "Temperature dependence of the energy gap in semi-conductors," *Physica*, vol. 34, no. 1, pp. 149–154, Jan. 1967, doi: 10.1016/0031-8914(67)90062-6.