### A Single-Supply Balun-First Three-Way mm-Wave Doherty PA

Kumaran, Anil; Pashaeifar, Masoud; Alexanderson, Mats; de Vreede, Leonardus Cornelis Nicolaas; Alavi, Morteza Ś.

DOI

10.1109/TMTT.2024.3365697

**Publication date** 2024

**Document Version** Final published version

Published in

IEEE Transactions on Microwave Theory and Techniques

Citation (APA)

Kumaran, A., Pashaeifar, M., Alexanderson, M., de Vreede, L. C. N., & Alavi, M. S. (2024). A Single-Supply Balun-First Three-Way mm-Wave Doherty PA. *IEEE Transactions on Microwave Theory and Techniques*, 72(5), 2757-2772. https://doi.org/10.1109/TMTT.2024.3365697

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Single-Supply Balun-First Three-Way mm-Wave Doherty PA

Anil Kumar Kumaran<sup>®</sup>, *Graduate Student Member, IEEE*,

Masoud Pashaeifar<sup>®</sup>, *Graduate Student Member, IEEE*, Mats Alexanderson<sup>®</sup>, *Member, IEEE*,

Leonardus Cornelis Nicolaas de Vreede<sup>®</sup>, *Senior Member, IEEE*, and Morteza S. Alavi<sup>®</sup>, *Member, IEEE*

Abstract—This article introduces a single-supply balun-first three-way parallel Doherty power amplifier (PA) tailored for millimeter-wave (mm-wave) fifth-generation (5G) applications. It incorporates a bandwidth enhancement technique that widens the operational frequency range, enhances broadband power back-off (PBO) efficiency, and reduces impedance mismatch between differential PAs. Realized in 40-nm CMOS bulk technology with a core area of 0.77 mm<sup>2</sup>, the prototype delivers a saturated power/peak gain surpassing 20 dBm/16 dB, and it demonstrates a drain efficiency (DE) exceeding 15%/22%/33% at 9.5 dB/6 dB/0 dB PBO across a 24-30 GHz band. The proposed mm-wave PA achieves EVM/ACLR values of -24.3 dB/-30.1 dBc for a 1-GHz 64-QAM OFDM signal, operating at an average output power (Pout) of 9.4 dBm with an average DE of 15%. For a 50-MHz 1024-QAM OFDM signal, it achieves an average Pout/DE of 8.6 dBm/12% with EVM/ACLR of -30 dB/-36.3 dBc.

Index Terms—Compact, Doherty, lumped components, millimeter wave, Norton transformation, power amplifier (PA), three-stage.

#### I. INTRODUCTION

THE millimeter-wave (mm-wave) spectrum finds application in various emerging fields like radar sensors and fifth-generation (5G) cellular networks. In the context of 5G networks, advanced techniques like phased arrays and spectrally efficient complex modulation are employed for multi-Gbit/s data transmission and low-latency line-of-sight links [1], [2], [3], [4]. As Table I outlines, exploiting higher-order modulation schemes such as quadrature-amplitude modulations (QAMs) and orthogonal frequency-division multiplexing (OFDM) presents uncompromising challenges due to their high peak-to-average power ratios (PAPRs). These

Manuscript received 15 September 2023; revised 14 December 2023 and 5 February 2024; accepted 7 February 2024. Date of publication 27 February 2024; date of current version 7 May 2024. This work was supported in part by the Dutch Government [Topconsortium voor Kennis en Innovatie (TKI)] and in part by the Open-Research Grant through Huawei Sweden. This article is an expanded version from the IEEE RFIC Symposium, San Diego, CA, USA, June 11–12, 2023. (Corresponding author: Anil Kumar Kumaran.)

Anil Kumar Kumaran, Masoud Pashaeifar, Leonardus Cornelis Nicolaas de Vreede, and Morteza S. Alavi are with the Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: a.k.kumaran@tudelft.nl; M.Pashaeifar@tudelft.nl; l.c.n.devreede@tudelft.nl; S.M.Alavi@tudelft.nl).

Mats Alexanderson is with Huawei Technologies Sweden AB, 412 50 Gothenburg, Sweden (e-mail: mats.alexanderson@huawei.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TMTT.2024.3365697.

Digital Object Identifier 10.1109/TMTT.2024.3365697

TABLE I

5G SYSTEM REQUIREMENTS [5], [6]

| PAPR for various modulations (Filter roll-off factor = 0.25) |      |        |        |      |        |        |  |

|--------------------------------------------------------------|------|--------|--------|------|--------|--------|--|

| Modulation                                                   | QPSK | 16 QAM | 64 QAM | QPSK | 16 QAM | 64 QAM |  |

|                                                              | SC   | SC     | SC     | OFDM | OFDM   | OFDM   |  |

| PAPR (dB)                                                    | 5    | 6.9    | 7.1    | 9.7  | 10.4   | 11     |  |

| 3GPP minimum EVM requirement |       |      |        |        |         |  |  |

|------------------------------|-------|------|--------|--------|---------|--|--|

| Modulation                   | BPSK  | QPSK | 16 QAM | 64 QAM | 256 QAM |  |  |

| Required EVM (dB)            | -10.5 | -15  | -18    | -21.9  | -29.1   |  |  |

| 5G 28/39 GHz application scenarios and estimated requirements |         |              |              |          |  |  |  |

|---------------------------------------------------------------|---------|--------------|--------------|----------|--|--|--|

| Scenario                                                      | Handset | Access point | Base station | Backhaul |  |  |  |

| EIRP <sub>avg</sub> (dBm)                                     | 30      | 45           | 55           | 60       |  |  |  |

| N <sub>ant</sub>                                              | 4-6     | 32           | 64           | 256      |  |  |  |

| Pavg/PA (dBm)                                                 | 11-15   | 12           | 16           | 9        |  |  |  |

| $P_{peak}$ /PA (dBm) (PAPR = 12 dB)                           | 23-27   | 24           | 28           | 21       |  |  |  |

| Average Efficiency (%)                                        | 20      | 20           | 20           | 20       |  |  |  |

| DC power (W)                                                  | 0.4-0.6 | 2.5          | 12           | 10       |  |  |  |

challenges place stringent demands on power amplifiers (PAs), requiring considerations for output power (Pout), average efficiency, error vector magnitude (EVM) for in-band linearity, and adjacent channel leakage ratios (ACLRs) for out-of-band spectral purity [5], [6]. Likewise, the push for high integration, cost-effectiveness, compact size, and efficiency drives the exploration of nanoscale CMOS technologies for 5G mm-wave transmitters (TXs). However, limited supply voltage and maximum oscillation frequency ( $f_{\text{max}}$ ) pose difficulties in meeting the power specifications of 5G TXs. The average and peak power requirements for various 5G scenarios are detailed in Table I.

For instance, under certain assumptions, the backhaul link budget necessitates an average/peak TX power exceeding 9/21 dBm. These assumptions include a 12 dB PAPR, 5 dB antenna gain, 2 dB connection loss between PA and antenna, and a 16×16 phased-array antenna configuration to counteract free space path loss at mm-wave frequencies. The PAs play a crucial role in determining Pout, average efficiency (which impacts thermal management) and overall reliability of the TX system. Additionally, these mm-wave 5G front-ends need to offer substantial power gain to relax design constraints for the preceding upconversion stages [5], [7].

While recent mm-wave linear PA designs have addressed EVM and ACLR requirements of 5G systems, achieving high average efficiency remains largely unresolved [8], [9], [10], [11], [12], [13], [14], [15]. To overcome the average efficiency

0018-9480 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

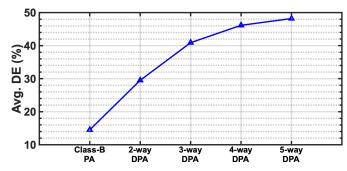

Fig. 1. OFDM signal's average DE with PAPR = 11.6 dB for Class B and N-way Doherty PAs.

and Pout issues in TXs, techniques like outphasing [16], [17], [18], [19], load-modulated balanced amplifiers (LMBAs) [20], [21], and *N*-way Doherty architectures [22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [32], [33], [34], [35], [36] have been explored. Outphasing PA demands significant baseband resources for generating outphasing signals and extensive digital predistortion (DPD). LMBA supports wideband modulation, but its power combiner introduces substantial die area, resulting in high insertion loss and reduced peak efficiency.

Among the various *N*-way Doherty configurations, a two-way Doherty PA is often realized [22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [32], [33]. Nonetheless, this configuration does not completely tackle the issue of enhancing average efficiency for signals with high PAPRs, approximately 12 dB. Additionally, generating more than 21 dBm Pout utilizing only two power devices using CMOS technology is challenging. *N*-way Doherty architectures also tend to be inherently narrowband due to the quarter-wave transmission line (TLs) impedance inverter utilized for load modulation. Besides, their bandwidth decreases as the order of Doherty architecture increases.

The average drain efficiency (DE), as shown in Fig. 1, is calculated by combining the probability distribution function (pdf) of the orthogonal frequency division multiplexing (OFDM) signal with the DE of the PA. The graph displays the average DE for different PA architectures: ideal class B, two-, three-, four-, and five-way Doherty, all for an OFDM signal with a PAPR of 11.6 dB. Notably, the average DE has no substantial enhancement beyond the three-way Doherty architecture. Consequently, considering practical constraints and losses in an N-way combiner at mm-wave frequencies, thorough analysis indicates that the three-way Doherty PA stands out as a strong candidate. Its performance at 12 dB PAPR is comparable to four-/five-way Doherty architectures while featuring a more compact combiner and reduced design complexity [37]. Recently implemented three-way [35], [36] and four-way [34] architectures are also narrowband, particularly at deep PAPR levels. Furthermore, they commonly rely on two supply voltages in cascode PA structure and complex power management systems in their front-end stages to achieve the required power gain and radiated power. Thus, realizing a compact mm-wavefront-end with high average efficiency across a wide frequency range, using a single supply while adhering to the tight element-to-element  $\lambda/2$  lattice spacing requirement of phased arrays remains a significant challenge.

An alternative approach has recently been realized that features a compact single-supply three-stage mm-wave threeway Doherty PA that employs a technique to enhance bandwidth (EBW) for broader operational frequency coverage [38]. This article elaborates on its architecture analysis, circuit-level design considerations, and extensive measurement results, organized as follows: Section II delves into the analysis of different three-way Doherty topologies, focusing on their operational bandwidth. Enhanced bandwidth (EBW) technique is detailed in Section III. Following the design methodology presented in Section IV, a compact power combiner comprising three identical balanced-to-unbalanced (balun) transformers, an inductor, and three capacitors is synthesized. Section V provides insights into the circuit implementation of the proposed Doherty PA prototype fabricated using the 40 nm bulk CMOS technology. Experimental results are discussed in Section VI, and the article concludes in Section VII.

#### II. THREE-WAY DOHERTY VARIANTS

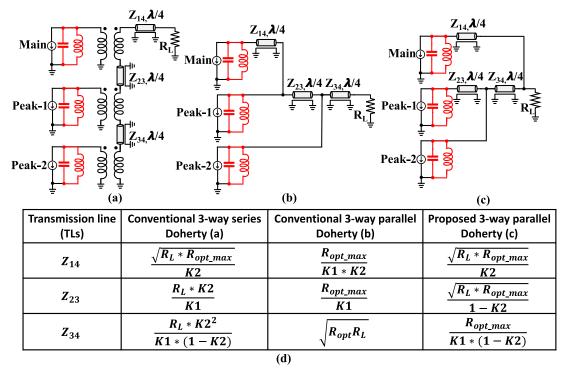

The three-way Doherty architecture can be deployed in a series configuration or a parallel configuration. Various iterations of the three-way Doherty architecture are illustrated in Fig. 2. The design equation for the proposed three-way Doherty structure is detailed in [37]. An inductor is employed to counteract the parasitic drain-source capacitance of the PA, as indicated by the red color in all three schematics.

The key advantages of the proposed three-way parallel Doherty combiner are as follows.

- 1) Among the different configurations, the three-way series Doherty configuration exhibits superior performance in terms of DE and Pout across the frequency spectrum (as shown in Fig. 3). However, this configuration necessitates three transformers for the main, peak-1, and -2 devices. In contrast, the parallel Doherty configuration only requires a balun for differential operation. Using three transformers in the series configuration leads to significant DE and Pout degradation compared to the parallel Doherty setup.

- 2) Traditional parallel Doherty demands the current of the main device to increase linearly with the input RF voltage up to the first back-off point and then to maintain a constant level up to full power. Executing this feature is challenging in analog PAs and can lead to nonlinearity issues [39].

- 3) During deep power back-off (PBO), the proposed combiner operates with only the main PA active, establishing a direct signal path between the main PA output and the overall Doherty PA output. This results in minimal power loss. The OFF-state impedance of the peak-1 PA primarily influences the efficiency of the proposed combiner.

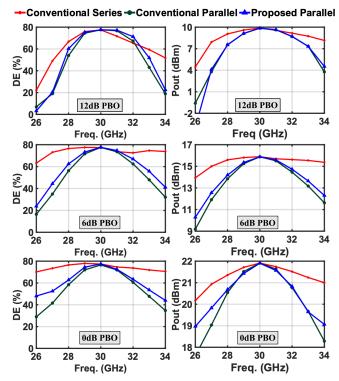

The symmetrical Doherty configuration offers the advantage of employing the same chain for the main, peak-1, and -2. Consequently, the proposed parallel Doherty architecture is designed symmetrically (with K1 = 0.5 and K2 = 0.33). However, Fig. 3 highlights that the proposed three-way Doherty configuration has limitations regarding its operational bandwidth.

Fig. 2. (a) Conventional three-way series Doherty, (b) conventional three-way parallel Doherty, (c) proposed three-way parallel Doherty [38], and (d) equations for calculating characteristic impedance  $(Z_0)$  of each TL for each design.

Fig. 3. DE and Pout across frequency at 12/6/0 dB PBO for K1 = 0.5 and K2 = 0.25

#### III. BANDWIDTH ANALYSIS

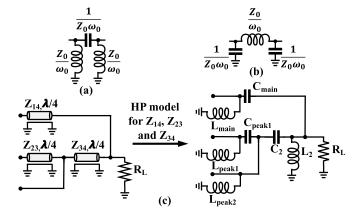

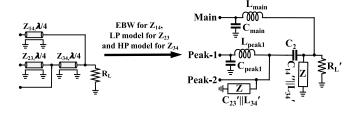

Due to its impractical size for on-chip implementation at mm-wave frequencies, the TL can be substituted with either a high-pass (HP) configuration [depicted in Fig. 4(a)] or a low-pass (LP) counterpart [illustrated in Fig. 4(b)] using lumped

Fig. 4. (a) HP lumped element model, (b) LP lumped element model, and (c) proposed three-way parallel Doherty using lumped elements.

element models. The HP model is chosen because it incorporates shunt inductors acting as a dc feed and provides inherent transformation into a differential circuit. Upon replacing each of the TL components ( $Z_{14}$ ,  $Z_{23}$ , and  $Z_{34}$ ) with the HP model, the parallel elements are consolidated, resulting in the schematic depicted in Fig. 4(c). The values of the inductor and capacitor in the lumped element model are computed based on the characteristic impedance ( $Z_0$ ) of the TL [refer Fig. 4(a) and (b)].  $Z_{14}$ ,  $Z_{23}$ , and  $Z_{34}$  correspond to  $Z_0$  of each respective TL.

#### A. Bandwidth Enhancement Technique

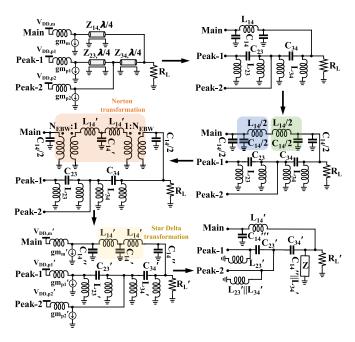

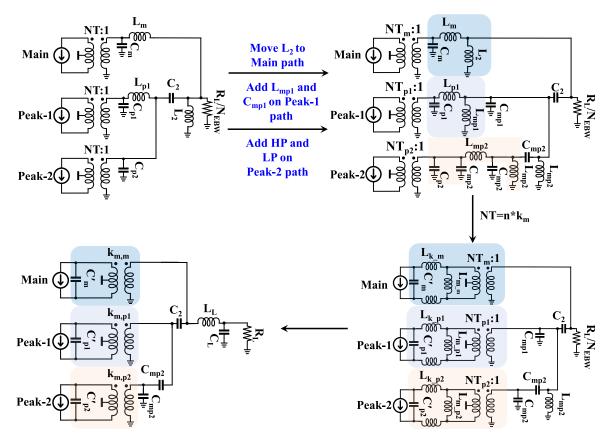

Fig. 5 depicts a step-by-step design procedure for the proposed EBW onto the suggested three-way parallel Doherty network. This technique is applied to the main PA's path,

Fig. 5. Proposed compact EWB technique on a three-way Doherty combiner.

which experiences the most prominent power losses. The process starts by substituting the  $Z_{14}$  TL with its LP lumped element equivalents. Subsequently, the capacitors and the inductor within the main path are divided, accompanied by a Norton transformation [40]. This transformation then leads to replacing the obtained transformer with the following adjustments: reducing the main supply source ( $V_{\rm DD}$ ) by  $N_{\rm EBW}$ , increasing the transconductance of the power device ( $g_{\rm m}$ ) by  $N_{\rm EBW}$ , augmenting capacitors by  $N_{\rm EBW}^2$ , and decreasing inductors and impedance seen at the drain node by  $N_{\rm EBW}^2$ , as shown in (1). Finally, a more compact three-way combiner configuration is achieved through the utilization of a star-to-delta transformation

$$V'_{DD} = \frac{V_{DD}}{N_{EBW}}$$

$$gm' = gm \times N_{EBW}$$

$$C' = C \times N_{EBW}^{2}$$

$$L' = \frac{L}{N_{EBW}^{2}}$$

$$R' = \frac{R}{N_{EBW}^{2}}.$$

(1)

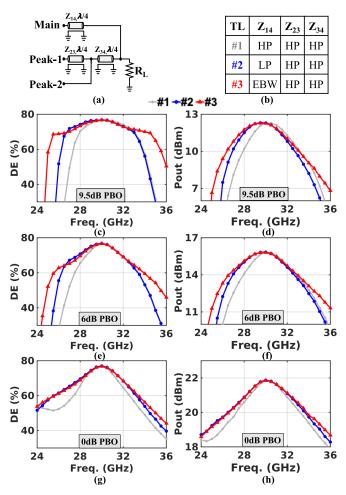

Fig. 6 displays three versions of the concept. In version 1, the HP model is applied to all the TLs alongside the lumped element equivalence illustrated in Fig. 4(c). Version 2 employs the LP model, replacing the  $Z_{14}$  TL. In version 3, the EBW technique is employed on the  $Z_{14}$  TL, incorporating the final lumped-element circuit shown in Fig. 5. Each version is simulated using an ideal current source and ideal components with an infinite quality factor (QF). Fig. 6 reveals that version 3 exhibits enhanced bandwidth for DE, particularly noticeable at deep PBO levels. Considering a QF of 15 for the inductors and 25 for capacitors, all three cases are simulated [37], [41]. Fig. 7 presents the enhancement in DE and  $P_{\text{out}}$  at 0/6/9.5 dB

Fig. 6. (a) Three-way Doherty structure, (b) variations in the three-way Doherty architecture, (c) DE versus frequency at 9.5 dB PBO, (d) Pout versus frequency at 9.5 dB PBO, (e) DE versus frequency at 6 dB PBO, (f) Pout versus frequency at 6 dB PBO, (g) DE versus frequency at 0 dB PBO, and (h) Pout versus frequency at 0 dB PBO using the ideal inductor and capacitor.

PBO levels across the bandwidth for the proposed three-way Doherty structure integrated with EBW.

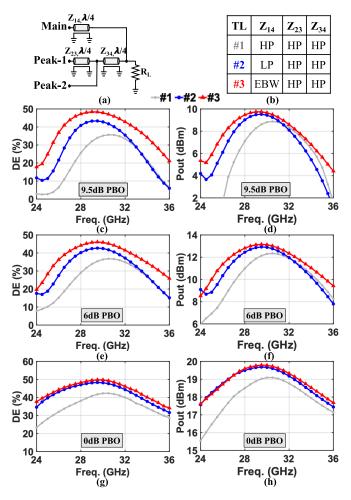

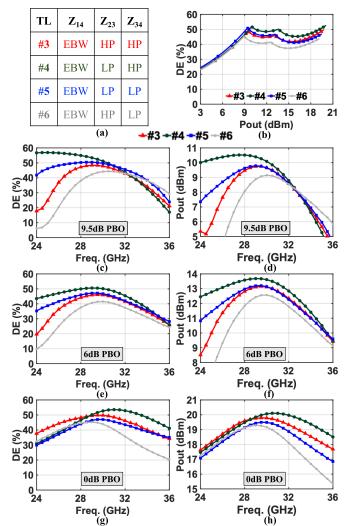

Variations in the three-way Doherty architecture can be achieved by alternating between the LP and HP models for the  $Z_{23}$  and  $Z_{34}$  TLs, as illustrated in Fig. 8(a). All simulations are carried out with an ideal PA model and a QF of 25/15 for the capacitors and inductors. The results indicate that alternative 4 in Fig. 8(a) outperforms its counterparts across frequencies at 9.5/6/0 dB PBO. The observed improvement in performance can be comprehended through an analysis of the HP and LP models of the TLs. Discrepancies in Pouts, as shown in Figs. 7 and 8, stem from variations in passive losses, given that the HP model of the TL incorporates two inductors compared to the LP model, thereby increasing passive losses.

#### B. Analysis of HP and LP Models of RLs

Fig. 9(a)–(d) presents the magnitude and phase profiles of  $S_{21}$  for the LP and HP lumped element models [as illustrated in Fig. 4(a) and (b)] of the TL over various characteristic impedance ( $Z_0$ ) settings spanning the frequency range of 24–36 GHz. After applying the EBW technique, the new value of the inductors and capacitors can be calculated using (1).

Fig. 7. (a) Three-way Doherty structure, (b) variations in the three-way Doherty architecture, (c) DE versus frequency at 9.5 dB PBO, (d) Pout versus frequency at 9.5 dB PBO, (e) DE versus frequency at 6 dB PBO, (f) Pout versus frequency at 6 dB PBO, (g) DE versus frequency at 0 dB PBO, and (h) Pout versus frequency at 0 dB PBO using QF of 25/15 for capacitors and inductors.

Then,  $Z_0$  EBW in Fig. 9(a)–(d) can be calculated.  $Z_0$  and  $Z_0$ EBW can be related as  $Z_0$  EBW =  $Z_0/N_{\rm EBW}^2$ . Additionally, Fig. 9(e) exhibits the variations in magnitude and phase of TL's  $S_{21}$  within the frequency range of 24–36 GHz, relative to different  $Z_0$  values. These visualizations reveal a noteworthy trend: as  $Z_0$  of the TL decreases, phase variation diminishes, while the reverse is observed for magnitude variation. Furthermore, the LP model of the TL exhibits lower phase and magnitude variations compared to the HP model. In Fig. 9(f), the phase variation of  $S_{21}$  is presented against frequency, examining cases where lumped element models of the TLs (with  $Z_0 = 50 \Omega$ ) are arranged in distinct configurations, such as HP-LP, LP-HP, HP-HP, and LP-LP. This analysis suggests that both HP-LP and LP-HP configurations exhibit relatively flat phase responses across frequencies when contrasted with the other configurations.

Among all considered versions, version 4 (depicted in Fig. 10) demonstrates superior performance in terms of bandwidth. This feature can be attributed to its integration of two LP models for the TLs and the application of EBW, which consequently reduces  $Z_0$  of each TL. Furthermore, version

Fig. 8. (a) Variations in the three-way Doherty architecture, (b) DE versus Pout, (c) DE across frequency at 9.5 dB PBO, (d) Pout across frequency at 9.5 dB PBO, (e) DE versus frequency at 6 dB PBO, (f) Pout across frequency at 6 dB PBO, (g) DE across frequency at 0 dB PBO, and (h) Pout across frequency at 0 dB PBO using QF of 25/15 for capacitors and inductors.

4 incorporates a hybrid of LP and HP circuits within the peak PAs, leading to diminished phase variation in the equivalent passive network when compared to version 5. The adjacency of an LP structure to the active power devices contributes to the absorption of parasitic drain–source capacitance. Additionally, the utilization of EBW results in reduced inductor values, facilitating smoother layout implementation and less susceptibility to QF influences. Finally, the proposed three-way Doherty architecture resembles an inverted two-way Doherty PA [26], enhancing its operational bandwidth.

## IV. PROPOSED BALUN-FIRST THREE-WAY DOHERTY POWER COMBINER

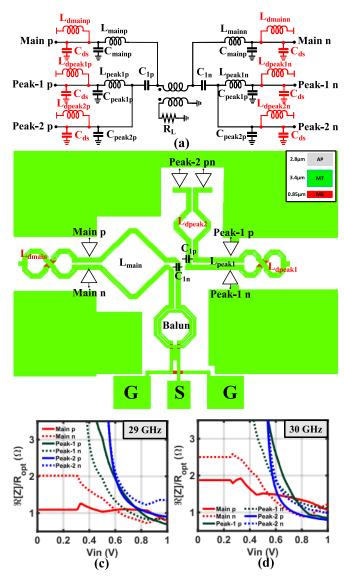

Mm-wave PA implementations commonly adopt push-pull PAs to enhance stability and increase Pout. Moreover, these push-pull PAs typically integrate a balun transformer at their end, catering to single-ended antenna configurations. Fig. 11(a) displays the schematic of version 4, presented in a push-pull configuration, while its corresponding layout is

Fig. 9. Magnitude of TL for different characteristic impedance for (a) LP, (b) HP, phase of TL for different characteristic impedance for (c) LP, (d) HP, (e) magnitude variation and phase variation versus characteristic impedance of TL across the frequency 24-36 GHz, and (f) phase variation of S<sub>21</sub> of the cascaded lumped element models of the TLs with  $Z_0 = 50 \Omega$  versus frequency.

Fig. 10. Version 4 schematics, which uses EBW for Z<sub>14</sub>, LP for Z<sub>23</sub>, and  $\overline{\text{HP}}$  for  $Z_{34}$ .

realized in 40 nm bulk CMOS, as depicted in Fig. 11(b). Fig. 11(c) and (d) reveals that push-pull PAs encounter varied impedances, particularly during PBO, due to unintended coupling among traces within the layout. Furthermore, the final circuit in Fig. 11(a) necessitates extra RF chokes to provide dc voltages to the main, peak-1, and -2 PAs, adding to the circuit's intricacy. These challenges can be addressed by splitting the output balun into three separate baluns and strategically relocating them to the drain terminals of the respective PAs [42].

#### A. Design Methodology

Fig. 12 outlines the stepwise progression involved in the design of a balun-first three-way Doherty combiner. The balun's turn ratio (NT) is derived using (2), where n signifies the ratio between secondary inductance  $(L_s)$  and primary

Fig. 11. Version 4 push-pull (a) schematic, (b) layout, and (c) normalized impedance of main, peak-1 and -2 PA versus input voltage (Vin) at 29 GHz, and (d) 30 GHz.

inductance  $L_p$   $(n = ((L_s/L_p))^{1/2})$ , and  $k_m$  represents the balun's coupling factor

$$NT = n \times k_m. \tag{2}$$

First,  $L_2$  is repositioned to the main path, followed by the relocation of  $C_m$ ,  $L_m$ , and  $L_2$  to the drain side of the main PA through the following equation:

$$L_{k m} = L_m \times NT_m^2 \tag{3}$$

$$L_{k_{-m}} = L_m \times NT_m^2$$

$$L_{m_{-m}} = L_2 \times NT_m^2$$

(3)

$$C_m' = \frac{C_m}{NT_m^2}. (5)$$

The main balun's design parameters  $(L_{p_{-}m}, L_{s_{-}m}, \text{ and } k_{m,m})$ are then computed using (6)–(8) [43]. NT<sub>m</sub> can be flexibly chosen, making n equal to 1. Consequently, the primary and secondary inductances can match sizewise, resulting in a single-turn balun. This type exhibits higher self-resonance than

Fig. 12. Procedure to design the proposed balun-first three-way Doherty.

multiturn baluns. NT<sub>m</sub> and  $k_{m,m}$  within the range of 0.6–0.7 is easier to implement in the layout at mm-wave. Next, practical balun transformers with  $L_{p_m}$ ,  $L_{s_m}$ , and  $k_{m,m}$  replace the ideal transformer, magnetizing inductance  $(L_m)$ , and leakage inductance  $(L_k)$  in the main path

$$L_{k_{-}m} = (1 - k_{m,m}^2) \times L_{s_{-}m} \tag{6}$$

$$L_{m\_m} = k_{m.m}^2 \times L_{s\_m} \tag{7}$$

$$n \times k_{m m} = NT_m. \tag{8}$$

Subsequently,  $L_{mp1}/C_{mp1}$  are introduced to the peak-1 path.  $C_{p1}$ ,  $L_{p1}$ , and  $L_{mp1}$  are also shifted to the drain side of the peak-1 PA using (3)–(5). The peak-1 balun is fashioned similar to the main balun employing (6)–(8). The LP/HP models of the TL are then incorporated into the peak-2 path. Analogous to the main and peak-1 PA paths,  $C_{p2}$ ,  $C_{mp2}$ , and  $L_{mp2}$  can be relocated to the drain side of the peak-2 PA using (3)–(5). The ideal transformer in the peak-2 PA path is replaced with practical balun transformers bearing  $L_{p_p2}$ ,  $L_{s_p2}$ , and  $k_{m,p2}$ .

Finally, using the following equations, an L-match  $(L_L \text{ and } C_L)$  is harnessed to convert  $R_L/N_{\rm EBW}$  to  $R_L$ . The L-match proves advantageous by incorporating pad capacitance into  $C_L$ , and the trace connecting the Doherty output and pad is utilized for  $L_L$  design, thereby minimizing additional component losses in comparison to a C-match (refer to the following equations):

$$\Re\{Z_L'\} = \frac{R_L}{N_{\text{EBW}}} = \frac{R_L}{1 + \omega^2 C_L^2 R_L^2} \tag{9}$$

$$\Im\{Z_L'\} = 0 \implies L_L = \frac{C_L R_L^2}{1 + \omega^2 C_I^2 R_I^2}.$$

(10)

The final circuit depicted in Fig. 12 features a compact network, incorporating only one inductor, four capacitors, and three baluns. The baluns' turn ratio (NT),  $C_{mp1}$ , and  $L_{mp2}$  are design parameters adaptable to achieve optimized values for layout synthesis. In this regard,  $C_{mp1}$  and  $L_{mp2}$  are selected to resonate at the desired operational frequency (30 GHz).  $C'_m$ ,  $C'_{p1}$ , and  $C'_{p2}$  can be used to absorb the parasitic drain—source capacitance  $(C_{ds})$  of the main, peak-1, and -2 PA.

In summary, with a specified Pout, supply voltage, and load, a balun-first three-way Doherty with bandwidth enhancement can be designed using the equations outlined in Fig. 2(d), coupled with the closed-loop equations above. These equations furnish initial values for the design parameters. Ultimately, the balun-first three-way Doherty configuration is realized within the available technology and optimized through electromagnetic (EM) simulations.

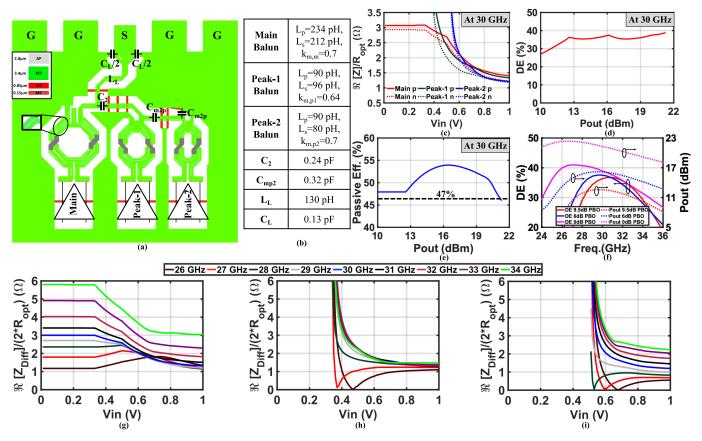

#### B. Layout and EM Simulation Results

The implementation of the proposed balun-first three-way Doherty layout is carried out using 40 nm CMOS bulk technology, as depicted in Fig. 13(a). This layout comprises three baluns, with coupling factors of 0.7, 0.64, and 0.7 assigned to the main, peak-1, and -2, respectively. The QF of the spiral/slab inductors is increased more than twofold using parallel slot lines of minimum width than utilizing one thick line of the required width, as shown in Fig. 13(a). The rationale

Fig. 13. (a) Layout of the proposed balun first three-way Doherty, (b) components' value, (c) impedance of main, peak-1 and -2 PA versus input voltage (Vin) at 30 GHz which is normalized to  $R_{\text{opt}}$ , (d) DE versus Pout at 30 GHz, (e) passive efficiency of the proposed balun first three-way Doherty combiner at 30 GHz, and (f) DE and Pout across frequency at 0/6/9.5 dB PBO, (g) impedance of main PA, (h) peak-1 PA, and (i) peak-2 PA versus input voltage (Vin) which is normalized to  $2 \times R_{\text{opt}}$ .

behind this choice lies in the signal's surface travel due to the skin effect, where splitting the lines increases the surface area, thereby reducing resistance and augmenting the QF [44]. This QF enhancement is particularly noticeable in slab and single-turn inductors/baluns, highlighting the preference for single-turn baluns in the proposed output network. Through optimization of component values based on the initial calculations presented in the preceding section, improved performance is achieved, and these updated values are displayed in Fig. 13(b).

All simulation results depicted in Fig. 13(c)–(f) are executed utilizing the EM model of the proposed output network [depicted in Fig. 13(a)] generated using momentum, capacitors possessing a QF of 25, and ideal PA models. In Fig. 13(c), the impedance encountered by the main, peak-1, and -2 push-pull PAs is illustrated when employing the EM model of the proposed balun-first technique, which is normalized to  $R_{\rm opt}$ . The mismatch in impedance experienced by the push-pull counterparts remains below 0.5. The relationship between DE and  $P_{\text{out}}$  exhibited in Fig. 13(d) confirms the desired threeway Doherty operation at 30 GHz. Furthermore, the proposed output network achieves a passive efficiency surpassing 47% at 30 GHz. Ultimately, the proposed three-way Doherty combiner demonstrates a DE exceeding 20%/25%/30% at PBO levels of 9.5/6/0 dB across the 27-34 GHz frequency band [as depicted in Fig. 13(f)]. Fig. 13(g)–(i) shows the normalized

impedance of the main, peak-1 and -2 PA versus input voltage across frequency.  $Z_{\rm Diff}$  is the differential impedance seen by the main, peak-1 and -2 PA. It is normalized to  $2 \times R_{\rm opt}$ , where  $R_{\rm opt}$  is the single-ended optimum impedance to achieve the required Pout.

#### V. CIRCUIT IMPLEMENTATION

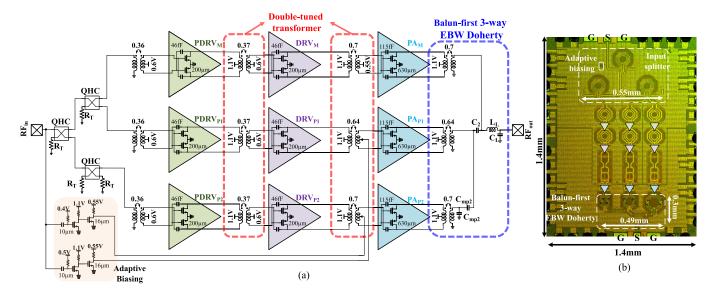

Fig. 14(a) illustrates a detailed diagram of the proposed PA configuration. The initial component is an input splitter [Fig. 15(a)] consisting of three quadrature hybrid couplers (QHCs). Subsequently, each branch, namely the main, peak-1, and -2 paths, includes an input balun [Fig. 15(b)], predriver (PDRV), interstage matching [Fig. 15(c)], driver (DRV), interstage matching [Fig. 15(d)], and the PA itself.

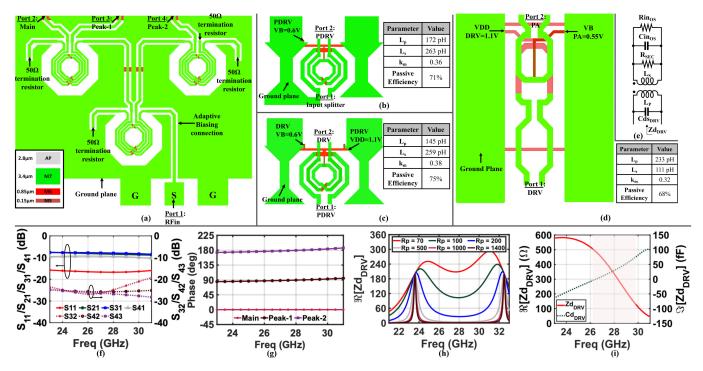

The arrangement of the input splitter, shown in Fig. 15(a), consists of three transformer-based single-ended QHCs [45] designed to generate phase shifts of 90° and 180°. The unused (port 5) and isolation ports are properly terminated at 50  $\Omega$ . The type of resistor used is P+ polyresistor without salicide. The S-parameters and phase response of the main, peak-1, and -2 paths are depicted in Fig. 15(f) and (g), utilizing an EM simulated model of the input splitter. Notably, the input matching ( $S_{11}$ ) exceeds -16 dB, and the isolation between the main and peak-1/peak-2 paths surpasses -21 dB within the 24–30 GHz frequency range, as indicated in Fig. 15(f).

Fig. 14. (a) Top-level and (b) die micrograph of the proposed PA.

The magnitude and phase characteristics of signals in these paths are presented in Fig. 15(f) and (g), with the phase difference remaining below  $5^{\circ}$  within the specified frequency band. Although using three QHCs improves  $S_{11}$  variations and phase differences compared to using two, there is a tradeoff with an increased insertion loss of 1.8 dB [46].

After the input splitter, a balun is utilized to transform the single-ended signal into a differential signal. This balun employs a double-tuned transformer approach [47], [48] to achieve wide-ranging matching, resulting in a passive efficiency of 71% [as shown in Fig. 15(b)]. Alternatively, it is possible to use a balun at the input in combination with a differential input splitter. However, this arrangement necessitates the inclusion of an interstage component for proper matching between the input splitter and PDRV, potentially leading to increased passive losses. In this scenario, the balun serves the dual purpose of converting the signal from single-ended to differential and providing interstage matching. The necessary power gain is achieved by integrating two additional stages, each employing a neutralized common-source transistor with 50 fingers and a width of 1 µm [refer to Fig. 14(a)]. A bias of 0.6 V is applied to PDRVs and DRVs. However, this architectural choice negatively impacts power-added efficiency (PAE). The interstage matching connecting PDRV and DRV utilizes a double-tuned transformer network [47], [48] to achieve wide matching, with its parameter values shown in Fig. 15(c). It provides a passive efficiency of 75%, calculated using the equation from [49].

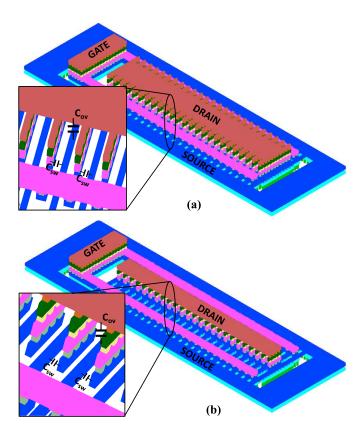

The PA utilizes common-source transistors and neutralization capacitors set at a bias of 0.55 V. To optimize the cut-off frequency ( $f_T$ ) and maximize the highest oscillation frequency ( $F_{\text{max}}$ ), the PA design incorporates seven unit cells, each consisting of 50 fingers with a width of 1.8 µm. Fig. 16(a) and (b) illustrates two variations of the unit cell layout within the PA. The second iteration reduces side wall capacitance ( $C_{sw}$ ) by eliminating metal one (m1) and contacts (CO) on both sides of the drain, as shown in Fig. 16(b). Additionally, the metal five (m5) trace is made thinner to reduce overlap capacitance ( $C_{ov}$ ). These modifications collectively minimize the parasitic drain–source capacitance ( $C_{ds}$ ). Version 2 accomplishes a  $C_{ds}$  of 57 fF, marking an enhancement compared to the 69 fF in version 1, while simultaneously improving  $F_{max}$ .

The intermediary stage connecting the DRV and PA employs a double-tuned transformer technique to achieve wideband matching. The schematic of this double-tuned transformer is depicted in Fig. 15(e), and the impedance experienced by the DRV ( $Zd_{DRV}$ ) is computed using (11), as shown at the bottom of the page, [50]. Notably,  $Cin_{OS}$  and  $Rin_{OS}$  correspond to the input capacitance and resistance of the PA, measured at approximately 250 fF and 6 k $\Omega$ , respectively. Additionally,  $R_{SEC}$  is the resistance in parallel with the PA, and  $Cds_{DRV}$  accounts for the parasitic drain–source capacitance of

$$Zd_{DRV} = \frac{-\omega \left(-\operatorname{Cin}_{OS} R_P T \omega^2 + j T \omega - L_P R_P\right)}{\left(j T R_P \operatorname{Cds}_{DRV} \operatorname{Cin}_{OS} \omega^4 + \operatorname{Cds}_{DRV} T \omega^3 + j (\operatorname{Cds}_{DRV} L_P + \operatorname{Cin}_{OS} L_S) R_p \omega^2 + L_S \omega - j R_p\right)}$$

where,

$$T = -L_P L_S + M^2$$

$$M = k_m \sqrt{L_P L_S}$$

$$R_P = R_{SEC} \|\operatorname{Rin}_{OS}$$

(11)

Fig. 15. (a) Layout of the input splitter, (b) input balun, (c) PDRV and DRV interstage matching transformer, (d) DRV and PA interstage matching transformers, (e) schematic of double-tuned interstage between DRV and PA, (f) S-parameters ( $S_{11}$ ,  $S_{21}$ ,  $S_{31}$ ,  $S_{41}$ ,  $S_{32}$ ,  $S_{42}$ , and  $S_{43}$ ) across frequency, (g) phase of main, peak-1 and -2 across frequency, (h) impedance plotted using (11) across frequency, and (i) impedance of the EM model across frequency.

Fig. 16. (a) Version 1 and (b) version 2 of the PA unit cell.

the DRV, respectively. M is the mutual inductance between the primary  $(L_p)$  and secondary  $(L_s)$  windings.

Fig. 15(h) visually illustrates the real part of impedance across varying frequencies as the parameter  $R_p$  changes. Most

importantly, higher  $R_p$  values result in a dip in the center frequency, thereby compromising the matching. Conversely, lower  $R_p$  values lead to a reduced voltage swing at the gate of the PA, preventing the PA from entering saturation. It is worth highlighting that the PA's substantial dimensions contribute to an increased  $Cin_{OS}$ , making wideband matching challenging. The layout of the interstage and specific component values are provided in Fig. 15(d). Fig. 15(i) employs the EM model of the interstage to present both the real and imaginary parts of the impedance observed by the DRV. Significantly, the interstage's 3 dB bandwidth is constrained to a mere 3 GHz, limiting the operational bandwidth despite the wideband capabilities of the output network.

An adaptive biasing circuit depicted in Fig. 14 is employed to implement Doherty load modulation. Adapted from [51], this circuit includes an envelope detector with an RF input and a turn-on voltage, placed as shown in Fig. 15(a). The specified turn-on voltage activates the peak PAs, set at 0.5 V and 0.4 V for peak-1 and -2 PAs, respectively. The adaptive biasing circuit offers a 3 dB bandwidth of 2.5 GHz.

#### VI. MEASUREMENT RESULTS

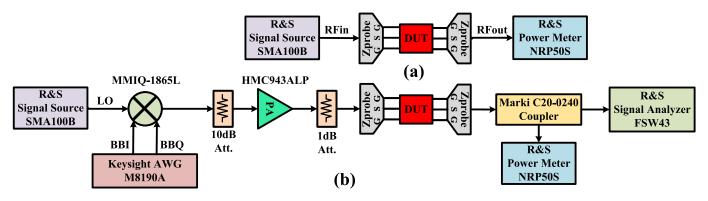

The proposed PA is fabricated in 40 nm bulk CMOS technology [Fig. 14(b)]. The core area of the proposed balunfirst three-way Doherty is  $1.4 \times 0.55$  mm<sup>2</sup>. All measurements are performed using a high-frequency probe station. The dc supplies, bias voltages, and turn-on voltage for adaptive biasing are wire-bonded directly to an FR4 printed circuit board (PCB). This work uses the 1.1 V supply voltage for the PAs, DRV, and PDRV amplifiers. Fig. 17(a) and (b) shows the continuous-wave (CW) and modulated measurement

Fig. 17. Simplified (a) continuous-wave and (b) modulation measurement setups.

Fig. 18. S-parameter measurement results of the proposed balun-first three-way Doherty PA.

setup. The insertion loss of the probes (Z-probe), cables, and directional couplers are measured and de-embedded.

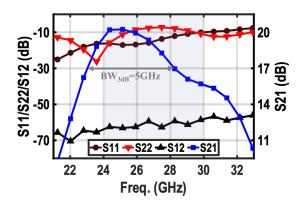

#### A. Continuous-Wave Measurement Results

The small-signal S-parameter performance is measured using the Keysight HP8753D vector network analyzer. As Fig. 18 demonstrates, the proposed PA achieves more than 5 GHz small-signal  $BW_{3\,\mathrm{dB}}$  where its  $S_{11}/S_{12}$  are less than -10/-50 dB over a 24–28 GHz band. At 26 GHz, PA's  $S_{22}$  is -8.5 dB, while its input matching is -16.8 dB. The PA offers 19.9 dB small-signal gain at 26 GHz.

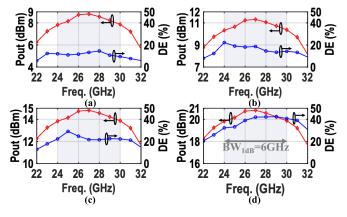

The large-signal CW measurement results are reported in Fig. 19 for various operational frequencies. At 25 GHz,  $P_{1\,dB}$  and  $P_{SAT}$  are 19.4 and 20.1 dBm, respectively. Its DE at  $P_{SAT}$ , 6 dB PBO, and 9.5 dB PBO are 33%, 25%, and 15%, respectively. Likewise, Fig. 19 indicates active load modulation only materializes over the 24–26 GHz band. So, the PBO efficiency enhancement bandwidth is 2 GHz. The efficiency at deep PBO is lower due to the smaller channel resistance of the device and finite QF of  $C_{ds}$ , especially of the main PA (refer to the Appendix). Note that the bandwidth is limited due to the high impedance transformation ratio required by the interstage between DRV and PA, as discussed in the earlier section. PAE is degraded since adaptive biasing is applied only to peak PAs and not the DRV and PDRV.

Fig. 20 shows  $P_{\text{out}}$  and DE across frequency at 12 dB PBO, 9.5 dB PBO, 6 dB PBO, and full power. It can be seen that the proposed PA achieves more than 20 dBm

Fig. 19. Measured gain, last-stage DE, and PAE versus Pout at various frequencies.

Fig. 20. Pout and DE across frequency at (a) 12 dB PBO, (b) 9.5 dB PBO, (c) 6 dB PBO, and (d) full power.

peak Pout and a DE of better than 10%/15%/22%/33% at 12 dB/9.5 dB/6 dB/0 dB across the 24–30 GHz band. The

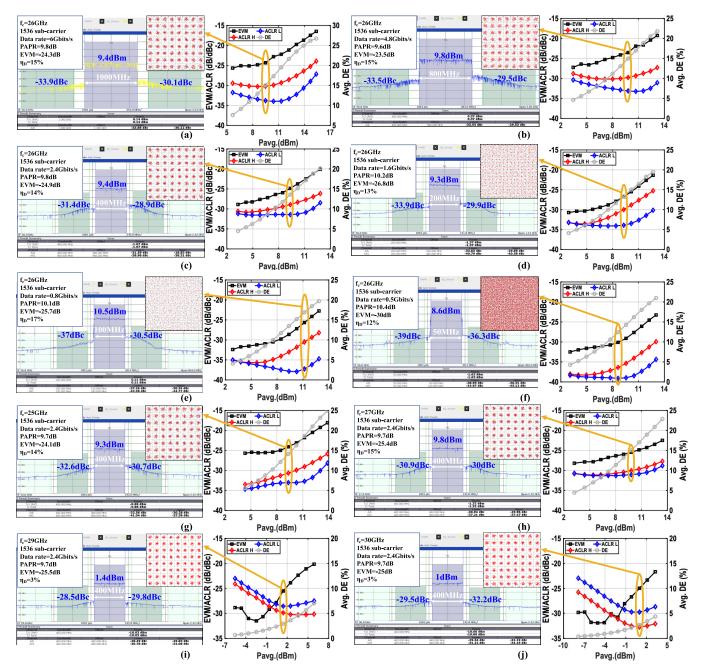

Fig. 21. (a) OFDM 1000 MHz 64-QAM, (b) OFDM 800 MHz 64-QAM, (c) OFDM 400 MHz 64-QAM, (d) OFDM 200 MHz 256-QAM, (e) OFDM 100 MHz 256-QAM, (f) OFDM 50 MHz 1024-QAM at 26 GHz, (g) OFDM 400 MHz 64-QAM at 25 GHz, (h) 27 GHz, (i) 29 GHz, and (j) 30 GHz measurement results.

PA achieves a 1 dB bandwidth of 6 GHz with respect to the  $P_{\rm sat}$ .

#### B. Modulated Signal Measurement Results

The PA dynamic performance is verified by wideband modulated signals such as "64-QAM OFDM," "256-QAM OFDM," and "1024-QAM OFDM" signals. As demonstrated in Fig. 17(b), the baseband I/Q modulated signals are generated with an arbitrary waveform generator (Keysight AWG M8190A) and upconverted using a Marki I/Q mixer (MMIQ-1865L). A directional coupler (Marki C20-0240) is employed at the output to provide the signal for an R&S FSW43 signal analyzer, while an R&S NRP50S measures the Pout.

Fig. 21(a) exhibits 9.4 dBm/15% average Pout/DE measured for a 6 Gb/s OFDM 64-QAM signal at 26 GHz with 9.8 dB PAPR. Its EVM/ACLR are -24.3 dB/-30.1 dBc, respectively. Similarly, the proposed PA achieves 9.8 dBm/15% average Pout/DE for a 4.8 Gb/s OFDM 64-QAM signal with EVM/ACLR of -23.5 dB/-29.5 dBc, respectively [Fig. 21(b)]. For a 1.6 and 0.8 Gb/s OFDM 256-QAM signal with 10.2 dB PAPR, the proposed PA achieves an EVM/ACLR of -26.8 dB/-29.9 dBc and -25.7 dB/-30.5 dBc [Fig. 21(d) and (e)]. The proposed PA is tested with 0.5 Gb/s OFDM 1024-QAM signal and results are shown in Fig. 21(f). Furthermore, the spectral purity and constellation of

|                                              |                             | 7.77            | W. 771           |               | D 1 10             |                    | ¥7.             |                    | ***           |

|----------------------------------------------|-----------------------------|-----------------|------------------|---------------|--------------------|--------------------|-----------------|--------------------|---------------|

| Specifications                               | This Work                   | Z.Ma            | X.Zhang          | Mortazavi     | Pashaeifar         | Huang              | Kim             | Mannem             | Wang          |

| ~ <b>P</b>                                   |                             | ISSCC'22 [36]   | RFIC'22 [35]     | JSSC'22 [34]  | JSSC'22 [33]       | ISSCC'21 [30]      |                 |                    | ISSCC'19 [25] |

|                                              | Balun-first                 | 3-way           | Coupled-inductor | Digital polar | 2-step impedance   | Continuous         | Parallel-series | Role-exchange      | Mixed-signal  |

| Architecture                                 | 3-way Parallel              | Parallel Series | based 3-way      | series 4-way  | inversion series   | Coupler            | Doherty         | Doherty            | Doherty       |

|                                              | Doherty PA                  | Doherty PA      | Doherty PA       | Doherty PA    | Doherty PA         | Doherty PA         | PA              | PA                 | PA            |

| PA structure                                 | 3-stage PAs                 | 2-stage PAs     | 2-stage PAs      | NA            | 2-stage PAs        | 2-stage PAs        | 2-stage PAs     | 2-stage PAs        | 2-stage PAs   |

| Technology                                   | 40 nm CMOS                  | 55 nm CMOS      | 45 nm SOI        | 40 nm CMOS    | 40 nm CMOS         | 45 nm SOI          | 28 nm CMOS      | 45 nm SOI          | 45 nm SOI     |

| Supply (V)                                   | 1.1                         | 2.4, 1.2+       | 1.8, 1           | 2 V, 1 V      | 1.8, 0.9           | 2, 1               | 0.9, 1.8        | 2, 1               | 2, 1          |

| Oper. Freq. (GHz)                            | 24-30                       | 28              | 38               | 29.5          | 24-32              | 26-60              | 27              | 26-60              | 27            |

| PBO Eff. Enh. BW (GHz)                       | 24-26                       | 28              | 38               | 29.5          | 24-28 <sup>a</sup> | 26-60 <sup>b</sup> | 27              | 26-60 <sup>b</sup> | 27            |

| Core Area (mm <sup>2</sup> )                 | 0.77                        | 0.54            | 1.4              | 1.1           | 0.37               | 0.62               | 0.16            | 0.67               | 0.37          |

| Gain (dB)                                    | 20 (26 GHz)                 | 16.1            | 15               | NA            | 17.4               | 15.5*              | 16.5            | 16*                | 19.1          |

| P <sub>sat</sub> (dBm)                       | 20.7 (26 GHz)               | 25.5            | 18.9             | 18.7          | 20.4               | 22                 | 18.8            | 22.6 (32 GHz)      | 23.3          |

| DE <sub>sat</sub> /PAE <sub>sat</sub> (%)    | 39/22.3 (26 GHz)            | 32.5/25.2       | 31*/23.3         | 36/24         | 46*/38.2           | NA/40.5            | 36*/30          | 46.7/41.9          | NA/40.1       |

| $DE_{6dB}/PAE_{6dB}$ (%)                     | 24.7/11.7 (26 GHz)          | 25.4/20.4       | 20*/17.1         | 33/15         | 39*/34             | NA/32.5            | 26*/22          | 35.1/31.5          | NA/33.1       |

| $DE_{9.5dB}/PAE_{9.5dB}$ (%)                 | 18.1/7 (26 GHz)             | 21*/17          | 17*/ 13.7        | 26*/10*       | 25*/20*            | NA/15*             | 17*/12*         | 22*/20*            | NA/20*        |

| $\mathbf{DE}_{12dB}/\mathbf{PAE}_{12dB}$ (%) | 11.7/4.2 (26 GHz)           | 18.2/14.2       | 15*/10*          | 22/10         | 10*/10*            | NA/10*             | 13*/10*         | 15*/11*            | NA/12*        |

| Modulation                                   | 64/64/64/256/1024           | 64              | 64               | 64            | 64                 | 64                 | 64              | 64 QAM             | 64            |

| Scheme                                       | QAM OFDM (26 GHz)           | QAM             | QAM OFDM         | QAM OFDM      | QAM OFDM           | QAM                | QAM OFDM        | (28 GHz)           | QAM           |

| Data rate (Gb/s)                             | 6/4.8/2.4/1.6/0.5           | 1.5#            | 0.6              | 1.8           | 2.4                | 3                  | 4.8             | 3                  | 6             |

| Modulation BW (MHz)                          | 1000/800/400/200/50         | 250             | 100              | 300           | 400                | 500                | 800             | 500                | 1000          |

| $EVM_{rms}$ (dB)                             | -24.3/-23.5/-24.9/-26.8/-30 | -25.2           | -25              | -27.58        | -24.5              | -25                | -25             | -24                | -25.3         |

| ACLR (dBc)                                   | -30.1/-29.5/-28.9/-29.9/-36 | -27             | -26.5*           | -27.5         | -28.2              | -28.8              | -25.9           | -28.8              | -29.6         |

| P <sub>avg</sub> (dBm)                       | 9.4/9.8/9.4/9.3/8.6         | 17.7            | 11.3             | 7.9           | 8.8                | 13.4               | 11.4            | 10.7               | 15.9          |

| PAE <sub>avg</sub> (%)                       | 15/15/14/13/12 (DE)         | 17.5            | 14.7             | 18            | 15                 | 24.8               | 18.1            | 14.5               | 29.1 (27.6++) |

| DPD                                          | No                          | No              | No               | Yes           | No                 | No                 | No              | No                 | No            |

TABLE II

PERFORMANCE SUMMARY AND COMPARISON TO DOHERTY mm-WAVE PAS

<sup>#</sup>limited by equipment. \*Graphically estimated. \*Nominal voltage of the technology. \*+Efficiency with digital circuits. \*a6dB PAE>29 %. \*b6dB PBO efficiency wrt class B PA>1.

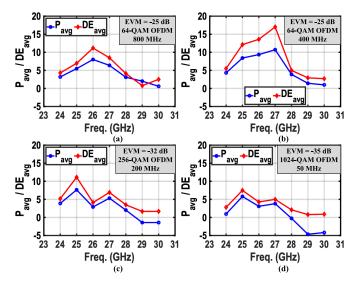

Fig. 22. Average power and DE for (a) OFDM 800 MHz 64-QAM, (b) OFDM 400 MHz 64-QAM, (c) OFDM 200 MHz 256-QAM, and (d) OFDM 50 MHz 1024-QAM across frequency to achieve certain EVM.

a 400 MHz OFDM 64-QAM signal is measured at 26, 25, 27, 29, and 30 GHz with EVM/ACLR of -24.9 dB/-28.9 dBc, -24.1 dB/-30.7 dBc, -25.4 dB/-30 dBc, -25.5 dB/-28.5 dBc, and -25 dB/-29.5 dBc which are illustrated in Fig. 21(c) and (g)-(j).

Fig. 22 illustrates the average  $P_{\rm out}$  and DE for an OFDM signal with different bandwidths (800/400/200/50 MHz) and modulation schemes (64/256/1024) within the 24–30 GHz frequency band, aiming to meet specific EVM requirements. To elaborate, considering the minimum EVM requirement for a 64-QAM signal as -21.9 dB (Table I) and providing a 3 dB margin, we present the average  $P_{\rm out}$ /DE for an EVM of -25 dB. The proposed PA achieves an average  $P_{\rm out}$ /DE performance surpassing 5.5 dBm/7% in the 24–27 GHz band, as shown in Fig. 22(a). Additionally, Fig. 22(b)–(d) exhibits

TABLE III

COMPARISON OF EFFICIENCY TO LINEAR mm-WAVE PAS

| Specifications                                             | This Work  | F.Wang<br>JSSC'21 [13] | M.Pashaeifar<br>MWCL'22 [14] | W.Zeng<br>ISSCC'23 [15] |  |

|------------------------------------------------------------|------------|------------------------|------------------------------|-------------------------|--|

| Technology                                                 | 40 nm CMOS | 45 nm SOI CMOS         | 40 nm CMOS                   | 28 nm CMOS              |  |

| Supply (V)                                                 | 1.1        | 2                      | 1                            | 1.8/0.9                 |  |

| Freq. (GHz)                                                | 26         | 28                     | 28                           | 28                      |  |

| Psat (dBm)                                                 | 20.7       | 20.4                   | 20.1                         | 20.3                    |  |

| DE <sub>sat</sub> /PAE <sub>sat</sub> (%)                  | 39/22.3    | 50*/45                 | 40.6/-                       | 34.7/33.6               |  |

| $DE_{6dB}/PAE_{6dB}$ (%)                                   | 24.7/11.7  | 26*/25*                | 19*/-                        | 15*/15*                 |  |

| $DE_{9.5dB}/PAE_{9.5dB}$ (%)                               | 18.1/7     | 16*/15*                | 11*/-                        | 8*/8*                   |  |

| <b>DE</b> <sub>12dB</sub> / <b>PAE</b> <sub>12dB</sub> (%) | 11.7/4.2   | 10*/9*                 | 7*/-                         | 5*/5*                   |  |

<sup>\*</sup>Graphically estimated.

corresponding results for OFDM signals with bandwidths of 400 MHz, utilizing 64-QAM, 200 MHz with 256-QAM and 50 MHz with 1024-QAM modulation schemes, respectively.

### C. Comparison With State-of-the-Art

The performance evaluation of the balun-first three-way Doherty PA is summarized in Table II and compared to that of previous designs. The results highlight that even with a supply voltage as low as 1.1 V, our compact singlesupply three-stage mm-wavefront-end achieves reasonable  $P_{\text{sat}}$ and power gain characteristics. Furthermore, its core area is the second best among three-/four-way Doherty PAs. Across the 24-30 GHz frequency range, the proposed PA delivers relatively high peak Pout, power gain, and efficiency, with respective values exceeding 20 dBm/16 dB/33%. Notably, at 12 dB/9.5 dB/6 dB PBO, the DE maintains superiority over 10%/15%/22% across the same frequency spectrum. The DE primarily drops at 6/9.5 dB PBO due to the lossy  $C_{\rm ds}$  of the main PA (see the Appendix) [52]. The lower DE/PAE at the deep PBO is not an inherent limitation of the proposed architecture. Enhancements can be made through improved design choices to reduce  $C_{ds}$  of the main PA, such

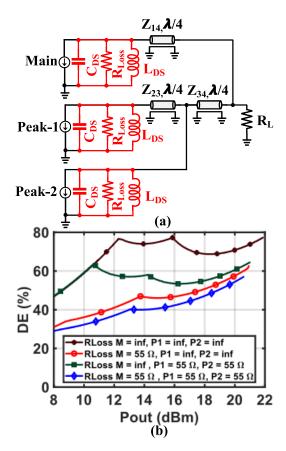

Fig. 23. (a) Proposed three-way parallel Doherty with  $R_{\rm Loss}$  and (b) DE versus Pout with  $R_{\rm loss}=55~\Omega/\infty$  for the main, peak-1 and -2 PA.

as: 1) utilizing advanced technology to reduce parasitics; 2) employing a higher voltage supply to reduce device size; and 3) implementing asymmetrical three-way Doherty.

It manages complex signals with a data rate of 4.8 Gb/s while demonstrating EVM/ACLR of -23.5 dB/-29.5 dBc, respectively. Notably, these achievements are attained without employing any DPD, which aligns with state-of-the-art standards.

Table III compares class B/AB PAs having a similar peak Pout and frequency of operation with our proposed three-way Doherty design. The table reveals that our proposed three-way Doherty surpasses the other three linear PAs in terms of DE at 9.5 dB PBO. Moreover, at 6-dB PBO compared to [14] and [15], our proposed PA exhibits better performance. However, the PAE is not as competitive compared to other models.

#### VII. CONCLUSION

A mm-wave three-way Doherty PA has been implemented that features an EBW to expand its operational bandwidth. A step-by-step design procedure for a balun-first configuration has been thoroughly explained. The proposed PA is fabricated using 40 nm CMOS technology, occupying a core area of 0.77 mm<sup>2</sup>. The realized front-end operating at 26 GHz demonstrates a power gain of 20 dB, a peak power of 20.7 dBm, and a DE of 39%/24.7%/18.1% at PBO levels of 0 dB/6 dB/9.5 dB. It attains an EVM and ACLR of -24.9 dB/-28.9 dBc for a 400 MHz 64-OFDM

signal with an average Pout of 9.4 dBm and a 14% average DE. For a 100 MHz 256-QAM OFDM signal, the proposed PA achieves EVM/ACLR of -25.7 dB/-30.5 dBc with an average Pout/DE of 10.5 dBm/17%. These results make it a promising choice for adoption in 5G mm-wave TXs.

#### **APPENDIX**

Fig. 23(a) illustrates the proposed three-way Doherty configuration, where  $C_{\rm ds}$  represents the drain-source capacitance of the device, and  $L_{\rm ds}$  is the inductor used for resonating out the  $C_{\rm ds}$ . In practical implementations, the device has a channel resistance and  $C_{\rm ds}$  possesses a finite QF. These can be represented by an  $R_{\rm Loss}$ , as depicted in Fig. 23(a), although ideally, it should be infinite.

Fig. 23(b) introduces  $R_{\text{Loss}}$  to all three PAs (main, peak-1, and -2). All other aspects of the simulation are considered ideal. The degradation in DE is less significant when  $R_{\text{Loss}} = 55~\Omega$  is added to all three PAs (blue curve) compared to when  $R_{\text{Loss}}$  is added only to the main PA (red curve). This emphasizes the dominant impact of the main PA's  $R_{\text{Loss}}$  on deep PBO efficiency compared to that of peak-1 and -2 PAs.

#### ACKNOWLEDGMENT

The authors would like to thank A. Akhnoukh, Z. Y. Chang, Dr. M. Spirito, C. De Martino, E. Shokrolahzade, Dr. Bueno, M. A. Montazerolghaem, G. D. Singh, and Dr. M. R. Beikmirza for their support and helpful discussions. They also thank IMEC Leuven for handling the tape-out.

#### REFERENCES

- E. G. Larsson, O. Edfors, F. Tufvesson, and T. L. Marzetta, "Massive MIMO for next generation wireless systems," *IEEE Commun. Mag.*, vol. 52, no. 2, pp. 186–195, Feb. 2014.

- [2] M. Shafi et al., "5G: A tutorial overview of standards, trials, challenges, deployment, and practice," *IEEE J. Sel. Areas Commun.*, vol. 35, no. 6, pp. 1201–1221, Jun. 2017.

- [3] I. Ahmed et al., "A survey on hybrid beamforming techniques in 5G: Architecture and system model perspectives," *IEEE Commun. Surveys Tuts.*, vol. 20, no. 4, pp. 3060–3097, 4th Quart., 2018.

- [4] T. Tuovinen, N. Tervo, and A. Pärssinen, "Analyzing 5G RF system performance and relation to link budget for directive MIMO," *IEEE Trans. Antennas Propag.*, vol. 65, no. 12, pp. 6636–6645, Dec. 2017.

- [5] P. M. Asbeck, N. Rostomyan, M. Özen, B. Rabet, and J. A. Jayamon, "Power amplifiers for mm-wave 5G applications: Technology comparisons and CMOS-SOI demonstration circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 7, pp. 3099–3109, Jul. 2019.

- [6] H. Wang, P. M. Asbeck, and C. Fager, "Millimeter-wave power amplifier integrated circuits for high dynamic range signals," *IEEE J. Microw.*, vol. 1, no. 1, pp. 299–316, Jan. 2021.

- [7] H. Hashemi, "Millimeter-wave power amplifiers & transmitters," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2017, pp. 1–8.

- [8] H.-T. Dabag, B. Hanafi, F. Golcuk, A. Agah, J. F. Buckwalter, and P. M. Asbeck, "Analysis and design of stacked-FET millimeter-wave power amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 4, pp. 1543–1556, Apr. 2013.

- [9] S. Shakib, M. Elkholy, J. Dunworth, V. Aparin, and K. Entesari, "2.7 A wideband 28 GHz power amplifier supporting 8×100 MHz carrier aggregation for 5G in 40nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 44–45.

- [10] W.-C. Huang, J.-L. Lin, Y.-H. Lin, and H. Wang, "A K-band power amplifier with 26-dBm output power and 34% PAE with novel inductance-based neutralization in 90-nm CMOS," in *Proc. IEEE Radio* Freq. Integr. Circuits Symp. (RFIC), Jun. 2018, pp. 228–231.

- [11] M. Vigilante and P. Reynaert, "A wideband class-AB power amplifier with 29–57-GHz AM–PM compensation in 0.9-V 28-nm bulk CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1288–1301, May 2018.

- [12] D. Manente, F. Padovan, D. Seebacher, M. Bassi, and A. Bevilac-qua, "A 28-GHz stacked power amplifier with 20.7-dBm output P1dB in 28-nm bulk CMOS," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 170–173, 2020.

- [13] F. Wang and H. Wang, "A broadband linear ultra-compact mm-wave power amplifier with distributed-balun output network: Analysis and design," *IEEE J. Solid-State Circuits*, vol. 56, no. 8, pp. 2308–2323, Aug. 2021.

- [14] M. Pashaeifar, L. C. N. de Vreede, and M. S. Alavi, "Load-modulation-based IMD3 cancellation for millimeter-wave class-B CMOS power amplifiers achieving EVM < 1.2%," *IEEE Microw. Wireless Compon. Lett.*, vol. 32, no. 6, pp. 716–719, Jun. 2022.

- [15] W. Zeng, L. Gao, N. Sun, H. Xu, Q. Xue, and X. Zhang, "25.2 A 19.7-to-43.8 GHz power amplifier with broadband linearization technique in 28nm bulk CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2023, pp. 372–374.

- [16] S. Li, T. Chi, H. T. Nguyen, T.-Y. Huang, and H. Wang, "A 28 GHz packaged Chireix transmitter with direct on-antenna outphasing load modulation achieving 56%/38% PA efficiency at Peak/6dB back-off output power," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 68–71.

- [17] B. Rabet and P. M. Asbeck, "A 28 GHz single-input linear Chireix (SILC) power amplifier in 130 nm SiGe technology," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1482–1490, Jun. 2020.

- [18] S. Li, M.-Y. Huang, D. Jung, T.-Y. Huang, and H. Wang, "A MM-wave current-mode inverse outphasing transmitter front-end: A circuit duality of conventional voltage-mode outphasing," *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1732–1744, Jun. 2021.

- [19] K. Ning, Y. Fang, N. Hosseinzadeh, and J. F. Buckwalter, "A 30-GHz CMOS SOI outphasing power amplifier with current mode combining for high backoff efficiency and constant envelope operation," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1411–1421, May 2020.

- [20] C. R. Chappidi, T. Sharma, Z. Liu, and K. Sengupta, "Load modulated balanced mm-Wave CMOS PA with integrated linearity enhancement for 5G applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Aug. 2020, pp. 1101–1104.

- [21] V. Qunaj and P. Reynaert, "A Ka-band Doherty-like LMBA for high-speed wireless communication in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3694–3703, Dec. 2021.

- [22] N. Rostomyan, M. Özen, and P. Asbeck, "28 GHz Doherty power amplifier in CMOS SOI with 28% back-off PAE," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 5, pp. 446–448, May 2018.

- [23] C. R. Chappidi, X. Wu, and K. Sengupta, "Simultaneously broadband and back-off efficient mm-Wave PAs: A multi-port network synthesis approach," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2543–2559, Sep. 2018.

- [24] Y.-C. Chen, Y.-H. Lin, J.-L. Lin, and H. Wang, "A Ka-band transformer-based Doherty power amplifier for multi-Gb/s application in 90-nm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 12, pp. 1134–1136, Dec. 2018.

- [25] F. Wang, T.-W. Li, S. Hu, and H. Wang, "A super-resolution mixed-signal Doherty power amplifier for simultaneous linearity and efficiency enhancement," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3421–3436, Dec. 2019.

- [26] S. Hu, F. Wang, and H. Wang, "A 28-/37-/39-GHz linear Doherty power amplifier in silicon for 5G applications," *IEEE J. Solid-State Circuits*, vol. 54, no. 6, pp. 1586–1599, Jun. 2019.

- [27] Z. Zong et al., "A 28-GHz SOI-CMOS Doherty power amplifier with a compact transformer-based output combiner," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 6, pp. 2795–2808, Jun. 2021.

- [28] N. S. Mannem, T.-Y. Huang, and H. Wang, "Broadband active load-modulation power amplification using coupled-line baluns: A multifrequency role-exchange coupler Doherty amplifier architecture," *IEEE J. Solid-State Circuits*, vol. 56, no. 10, pp. 3109–3122, Oct. 2021.

- [29] S. Kim, H.-C. Park, D. Kang, D. Minn, and S.-G. Yang, "A 24.5–29.5 GHz broadband parallel-to-series combined compact Doherty power amplifier in 28-nm bulk CMOS for 5G applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2021, pp. 171–174.

- [30] T.-Y. Huang, N. S. Mannem, S. Li, D. Jung, M.-Y. Huang, and H. Wang, "26.1 A 26-to-60 GHz continuous coupler-Doherty linear power amplifier for over-an-octave back-off efficiency enhancement," in *Proc. IEEE Int. Solid- State Circuits Conf. (ISSCC)*, Feb. 2021, pp. 354–356.

- [31] M. Pashaeifar, L. C. N. de Vreede, and M. S. Alavi, "A millimeter-wave mutual-coupling-resilient double-quadrature transmitter for 5G applications," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3784–3798, Dec. 2021.

- [32] F. Wang and H. Wang, "A high-power broadband multi-primary DAT-based Doherty power amplifier for mm-wave 5G applications," *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1668–1681, Jun. 2021.

- [33] M. Pashaeifar, L. C. N. de Vreede, and M. S. Alavi, "A millimeter-wave CMOS series-Doherty power amplifier with post-silicon interstage passive validation," *IEEE J. Solid-State Circuits*, vol. 57, no. 10, pp. 2999–3013, Oct. 2022.

- [34] M. Mortazavi, Y. Shen, D. Mul, L. C. N. de Vreede, M. Spirito, and M. Babaie, "A four-way series Doherty digital polar transmitter at mm-Wave frequencies," *IEEE J. Solid-State Circuits*, vol. 57, no. 3, pp. 803–817, Mar. 2022.

- [35] X. Zhang, S. Li, D. Huang, and T. Chi, "A 38GHz deep back-off efficiency enhancement PA with three-way Doherty network synthesis achieving 11.3dBm average output power and 14.7% average efficiency for 5G NR OFDM," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.* (RFIC), Jun. 2022, pp. 239–242.

- [36] Z. Ma, K. Ma, K. Wang, and F. Meng, "A 28 GHz compact 3-Way transformer-based parallel-series Doherty power amplifier with 20.4%/14.2% PAE at 6-/12-dB power back-off and 25.5dBm PSAT in 55nm bulk CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 65, Feb. 2022, pp. 320–322.

- [37] A. K. Kumaran, H. M. Nemati, L. C. N. De Vreede, and M. S. Alavi, "Compact N-way Doherty power combiners for mm-wave 5G transmitters," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2022, pp. 438–442.

- [38] A. K. Kumaran, M. Pashaeifar, H. M. Nemati, L. C. N. de Vreede, and M. S. Alavi, "A 26GHz balun-first three-way Doherty PA in 40nm CMOS with 20.7 dBm P<sub>sat</sub> and 20dB power gain," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2023, pp. 189–192.

- [39] W. C. E. Neo, J. Qureshi, M. J. Pelk, J. R. Gajadharsing, and L. C. N. de Vreede, "A mixed-signal approach towards linear and efficient N-way Doherty amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 5, pp. 866–879, May 2007.

- [40] V. Bhagavatula, M. Taghivand, and J. C. Rudell, "A compact 77% fractional bandwidth CMOS band-pass distributed amplifier with mirror-symmetric Norton transforms," *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1085–1093, May 2015.

- [41] S. Jeyaraman, V. N. R. Vanukuru, D. Nair, and A. Chakravorty, "Modeling of high-Q conical inductors and MOM capacitors for millimeter-wave applications," *IEEE Trans. Electron Devices*, vol. 67, no. 12, pp. 5646–5652, Dec. 2020.

- [42] D. Jung, H. Zhao, and H. Wang, "A CMOS highly linear Doherty power amplifier with multigated transistors," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 5, pp. 1883–1891, May 2019.

- [43] J. R. Long, "Monolithic transformers for silicon RF IC design," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1368–1382, Sep. 2000.

- [44] H. Gao et al., "A 48–61 GHz LNA in 40-nm CMOS with 3.6 dB minimum NF employing a metal slotting method," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 154–157.

- [45] R. C. Frye, S. Kapur, and R. C. Melville, "A 2-GHz quadrature hybrid implemented in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 550–555, Mar. 2003.

- [46] J. S. Park and H. Wang, "A transformer-based poly-phase network for ultra-broadband quadrature signal generation," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 12, pp. 4444–4457, Dec. 2015.

- [47] M. Vigilante and P. Reynaert, "On the design of wideband transformer-based fourth order matching networks for E-band receivers in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 52, no. 8, pp. 2071–2082, Aug. 2017.

- [48] V. Bhagavatula, T. Zhang, A. R. Suvarna, and J. C. Rudell, "An ultra-wideband IF millimeter-wave receiver with a 20 GHz channel bandwidth using gain-equalized transformers," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 323–331, Feb. 2016.

- [49] I. Aoki, S. D. Kee, D. B. Rutledge, and A. Hajimiri, "Distributed active transformer—A new power-combining and impedance-transformation technique," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 1, pp. 316–331, Jan. 2002.

- [50] A. K. Kumaran, "Linear and efficient power amplifier for WiFi," M.S. thesis, Dept. Microelectron., Delft Univ. Technol., Delft, The Netherlands, 2020. [Online]. Available: http://resolver.tudelft. nl/uuid:9370704d-a455-4a64-924e-ab428450327c

- [51] H. T. Nguyen, T. Chi, S. Li, and H. Wang, "A linear high-efficiency millimeter-wave CMOS Doherty radiator leveraging multi-feed onantenna active load modulation," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3587–3598, Dec. 2018.

- [52] G. D. Singh, H. M. Nemati, M. S. Alavi, and L. C. N. de Vreede, "An inverted Doherty power amplifier insensitive to load variation with an embedded impedance sensor in its output power-combining network," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 12, pp. 5194–5208, May 2023.

Anil Kumar Kumaran (Graduate Student Member, IEEE) received the B.Tech. degree in electronics and communication engineering from Amrita Viswa Vidhyapeetham, Coimbatore, India, in May 2015, and the M.Sc. degree in microelectronics from the Delft University of Technology, Delft, The Netherlands, in August 2020, where he is currently pursuing the Ph.D. degree at the ELCA Research Group.

Before joining his masters, he worked as an Onsite Validation Engineer at Texas Instruments, Bangalore, India. His research activity primarily focuses

on designing linear and efficient mm-wave transmitters for 5G cellular applications.

Masoud Pashaeifar (Graduate Student Member, IEEE) received the M.Sc. degree in circuits and systems from the University of Tehran, Tehran, Iran, in 2013. He is currently pursuing the Ph.D. degree at the Delft University of Technology, Delft, The Netherlands.

He was the Head of the Hardware Research Group, Bakhtar Communication Company, Tehran, from 2014 to 2018. He has been with Apple Inc., Munich, Germany, since September 2022. His current research interests include RF/mm-wave/sub-

THz transceivers.

Mr. Pashaeifar received the IEEE Solid-State Circuits Society Predoctoral Achievement Award for 2021–2022. He serves as a reviewer for IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC) and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS (TCAS-I).

Mats Alexanderson (Member, IEEE) was born in Fristad, Sweden. He received the M.Sc. degree in electrical engineering from the Chalmers University of Technology, Göteborg, Sweden, in 1994.

He has long experience in industry Research and Development and product development within micro- and millimeter-wave active and passive frontend systems for telecommunications, radar, and space research. He has worked for several companies as an employee and as a specialist consultant. His work experience spans from semiconductor device

modeling to MMIC design, module design, and integration, test, and verification, production test system design and support, and antenna design over to product 3-D design with integration of high-frequency electronics and mechanics. Since 2016, he has been with Huawei Sweden as a 5G/6G industry researcher with a focus on frontend hardware architectures, coherent LO distribution, reconfigurable reflective surfaces, and interaction between antenna and electronics for active arrays.

**Leonardus Cornelis Nicolaas de Vreede** (Senior Member, IEEE) received the Ph.D. degree (cum laude) from the Delft University of Technology, Delft, The Netherlands, in 1996.

In 1996, he was appointed as an Assistant Professor at the Delft University of Technology, working on the nonlinear distortion behavior of active devices. In 1999 and 2015, he was appointed as an Associate and a Full Professor at the Delft University of Technology, where he became responsible for the Electronic Research Laboratory (ERL/ELCA).

During that period, he worked on solutions for improved linearity and RF performance at the device, circuit, and system levels. He is the Co-Founder/Advisor of Anteverta-mw, Eindhoven, The Netherlands, a company specializing in RF device characterization. He has authored or coauthored more than 120 IEEE-refereed conference and journal papers and holds several patents. His current interests include RF measurement systems, RF technology optimization, and (digital-intensive) energy-efficient/wideband circuit/system concepts for wireless applications.

Dr. de Vreede was a co-recipient of the IEEE Microwave Prize in 2008, the Mentor of the Else Kooi Prize Awarded for his Ph.D. work in 2010, and the Mentor of the Dow Energy Dissertation Prize Awarded for his Ph.D. work in 2011. He was a recipient of the TUD Entrepreneurial Scientist Award 2015. He has co-guided several students who won (best) paper awards at the IEEE Bipolar/BicMOS Circuits and Technology Meeting (BCTM), Program for Research on Integrated Systems and Circuits (PRORISC), the IEEE Symposium on Gallium Arsenide Integrated Circuit (GaAs IC), the IEEE European Solid-State Device Research Conference (ESSDERC), IMS, RFIT, and RFIC.

Morteza S. Alavi (Member, IEEE) received the M.S.E.E. degree from the University of Tehran, Tehran, Iran, in 2006, and the Ph.D. degree in electrical engineering from the Delft University of Technology (TU-Delft), Delft, The Netherlands, in 2014.

He was the Co-Founder and the Chief Executive Officer (C.E.O.) of DitIQ B. V., Delft, a local company developing energy-efficient, wideband wireless transmitters for the next generation of the cellular network. Since 2016, he has been with the Electronic

Circuits and Architectures Research Group, TU-Delft, where he is currently a tenured Assistant Professor. He has authored or coauthored the book titled *Radio Frequency Digital-to-Analog Converter* (Elsevier, 2016). His current research interests include designing high-frequency and high-speed wireless/cellular communication and sensor systems and the field of wireline transceivers.

Dr. Alavi received the Best Paper Award from the 2011 IEEE International Symposium on Radio Frequency Integrated Technology and the Best Student Paper Award (Second Place) from the 2013 Radio Frequency Integrated Circuits Symposium. His Ph.D. student also received the Best Student Paper Award (First Place) from the 2017 R.F.I.C. Symposium in Honolulu, HI, USA. His research group recently received the 2021 Institute of Semiconductor Engineers President Best Paper Award from the International SoC Design Conference. One of his Ph.D. students also received the Platinum Award (First Place) from the 2021 Huawei Student Design Contest. He is also a co-recipient of the 2022 Best Paper Award of the honorable mentioned IEEE Brain and S.S.C.S. Joint Communities Paper.