#### Low power IC design characterization techniques under process variations

Zandrahimi, Mahroo

10.4233/uuid:4f46e987-87a6-4f66-afa7-de9eacb8dc29

**Publication date**

**Document Version** Final published version

Citation (APA)

Zandrahimi, M. (2018). Low power IC design characterization techniques under process variations. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:4f46e987-87a6-4f66afa7-de9eacb8dc29

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Low Power IC Design Characterization Techniques under Process Variations

# Low Power IC Design Characterization Techniques under Process Variations

### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft,

door

### Mahroo ZANDRAHIMI

Master of Science in Computer Architecture geboren te Birmingham, United Kingdom

Dit proefschrift is goedgekeurd door de promotoren:

Dr. Z. Al-Ars

#### Prof. dr. K.L.M. Bertels

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Dr. Z. Al-Ars, Technische Universiteit Delft, promotor Prof. dr. K.L.M. Bertels, Technische Universiteit Delft, promotor

Independent members:

Prof. dr. L. Koskinen,

Prof. dr. B. Nauta,

Dr. N.P. van der Meijs,

Prof. dr. L.C.N. de Vreede,

Dr. P. Debaud,

University of Turku, Finland

University of Twente, Netherlands

Technische Universiteit Delft

STMicroelectronics, France

*Keywords:* Adaptive voltage scaling, process variations, performance estimation,

process monitoring boxes, delay testing, transition fault testing, path

delay testing

This work is carried out under the BENEFIC project (CA505), a project labelled within the framework of CATRENE, the EUREKA cluster for Application and Technology Research in Europe on NanoElectronics.

#### Copyright © 2018 by M. Zandrahimi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed in the Netherlands

### **ACKNOWLEDGEMENTS**

I have encountered many good people over the years, who have all done their best to help me through this process of starting, working with, and finally, finishing this dissertation. Here, I would like to express my deepest gratitude. First and foremost, I would like to thank my supervisor and promotor, Dr. Zaid Al-Ars, who always believed in me, helped me gain my confidence and taught me many research skills and life lessons. I owe special thanks to him, since his careful supervision, helpful suggestions and generous support were really encouraging to me.

I would also like to express my deepest thanks to the head of QCE department, Prof. Koen Bertels, who gave me a sense of security and helped me every step of the way, Dr. Carmen G. Almudever, who treated me with the utmost kindness, Dr. Mottaqiallah Taouil who has always been so helpful and understanding, Ms. Lotte Ophey, my HR advisor, who heard my desperate cry for help at the time I were in need of emotional assistance. I would also like to thank the QCE staff, which include QCE secretaries Lidwina Tromp and Joyce van Velzen, as well as system administrator Erik for his administrative and technical assistance throughout. Finally, I would like to thank my fellow PhD students and friends, such as, Anh, Innocent, Hamid, Jintao, Lingling, Troya, Haji, Moritz, Imran, Shanshan, Nauman, Jian, Nader, and Ernst.

I met plenty of inspiring people throughout my stay in France to whom I will be eternally grateful. To name a few, Dr. Philippe Debaud who made me experience Many happy moments and made my work utterly enjoyable and I hope I will be so lucky to work with him again in the future. The next person I would like to mention is Armand Castillejo, who made my collaboration with STMicroelectronics in France possible and also made my stay there much more pleasant. Moreover, I take this opportunity to thank my colleagues, Matthieu Sautier, Mohamedarif Alarakhia, and Rachid Idrissi, members of DFT group in STMicroelectronics, as well as, Pierre Duclos from Synopsys, who were always helpful during my stay in STMicroelectronics.

I am also very grateful to Shermin and Stephan Danaie for their pure kindness and generously accepting me as a part of their family. Furthermore, I would like to express my appreciation to my friend Gerona who has always been there for me in the most desperate times of my life. Also, special thanks to my friends, Cédric, Clément, Frédéric, Annelise, David, and Audrey for their emotional support during my stay in Grenoble.

I am specially indebted to my life coach, Caroline Dessing, who helped me get back on my feet and start working towards achieving my goals. Next, Ilse Meezen, my yoga teacher, who has always selflessly devoted herself to me and encouraged me to find peace. viii Acknowledgements

I would also like to thank dear Panida who taught me how to be confident and stand up for myself. I am also highly obliged to my friends Alireza and Barbara; Alireza for always truly understanding me and Barbara for being the most selfless person I have ever encountered in my life. Without their assistance, I would have never had the courage to finish this thesis. Furthermore, special thanks to my friends, Parvaneh, Sara, Negin, Mohadeseh M, Mohadeseh S, Razieh, Vida, Sima, Sahar, Samira, Mona, Farideh, Arezu, Shirin and Bahareh, who have always supported me and comforted me in my time of need, even though we were far away from each other.

Last but certainly not least, my family who have always been the light of my life even when everything seemed dark. They never doubted me for a second and have been truly supportive during all stages of my life.

Mahroo Zandrahimi Delft, July 2018

## **SUMMARY**

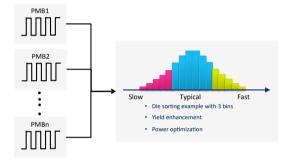

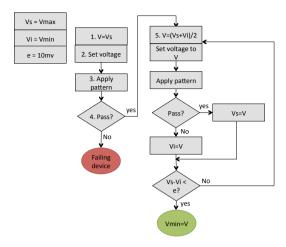

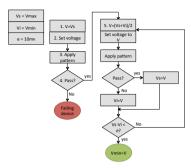

To overcome the increasing sensitivity to variability in nanoscale integrated circuits, operation parameters (e.g., supply voltage) are adapted in a customized way exclusively to each chip. AVS is a standard industrial technique which has been adopted widely to compensate for process, voltage, and temperature variations as well as power optimization of integrated circuits. For cost and complexity reasons, AVS techniques are usually implemented by means of on-chip performance monitors (so-called PMBs) allowing fast performance evaluation during production or run time. Such on-chip monitoring approaches estimate operation parameters either based on responses from performance monitors with no interaction with the circuit or by monitoring the actual critical paths of the circuit.

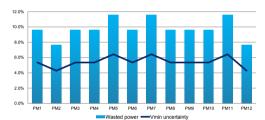

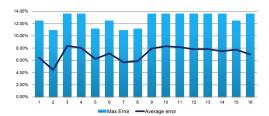

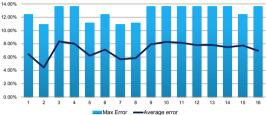

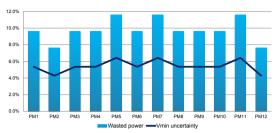

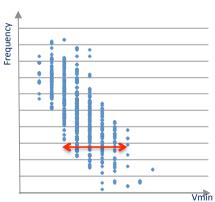

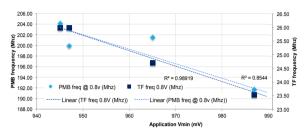

In this thesis, we focus on AVS techniques, which estimate operation parameters using responses from on-chip performance monitors with no interaction with the circuit during production. We discuss the challenges that these monitoring methodologies face with decreasing node sizes, in terms of accuracy and effectiveness. We show that the accuracy of these approaches is design dependent, and requires up to 15% added design margin. In addition, we show using silicon measurements of a nanometric FD-SOI device that the required design margin is above 10% of the clock cycle, which leads to significant waste of power.

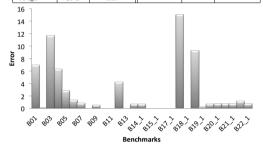

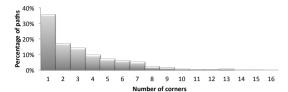

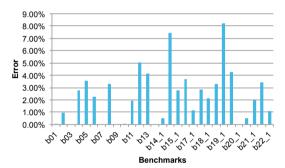

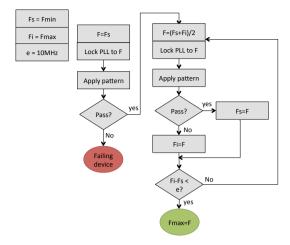

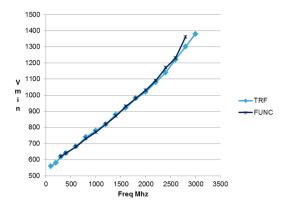

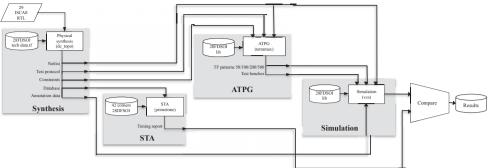

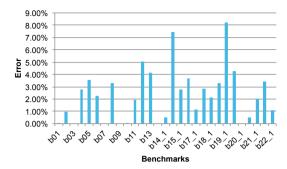

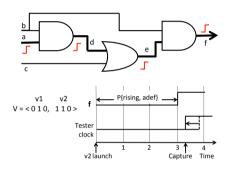

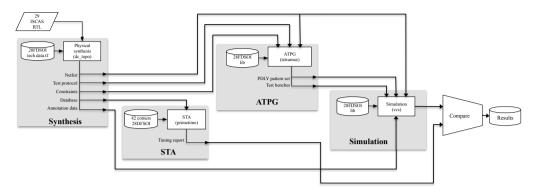

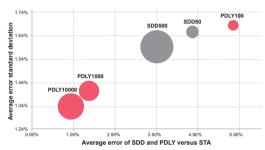

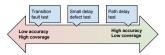

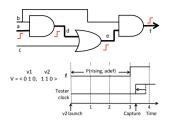

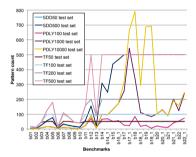

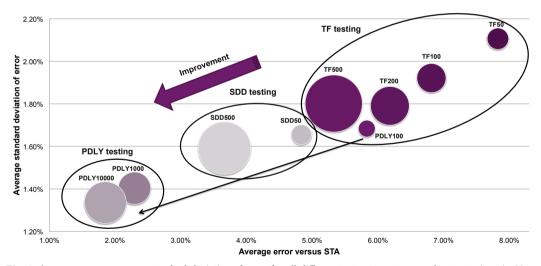

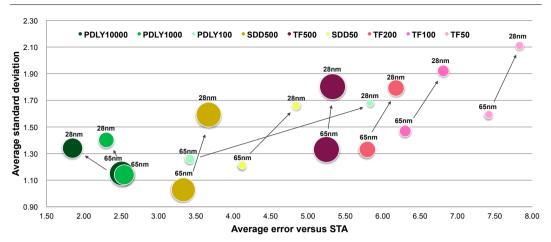

In this thesis, we introduce the new method of using delay test patterns including TF, SDD, and PDLY test patterns for application of AVS during IC production. The proposed method is able to eliminate the need for PMBs, while improving the accuracy of performance estimation. The basic requirement of using delay-based AVS is that there should be a reasonable correlation between the frequency the chip can attain while passing all delay test patterns and the actual frequency of the chip. Based on simulation results of ISCAS'99 benchmarks with a 28 nm FD-SOI library, using delay test patterns result in an error of 5.33% for TF testing, an error of 3.96% for SDD testing, and an error as low as 1.85% using PDLY testing. Accordingly, PDLY patterns have the capacity to achieve the lowest error in performance estimation, followed by SDD patterns and finally TF patterns. We performed the same analysis using a 65 nm technology node, which showed the same results.

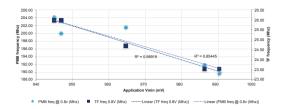

We also did two different silicon measurements on a 28 nm FD-SOI CPU to investigate the effectiveness of the TF-based approach. The results of the first case study on real silicon comparing the performance estimation using functional test patterns and the TF-based approach show a very close correlation between the two, which proves the effectiveness of the TF approach. The second case study compares the accuracy of voltage estimation using PMBs and the TF-based approach. The results show that the PMB approach can only account for 85% of the uncertainty in voltage measurements, which results in considerable power waste. In comparison, the TF-based approach can account for 99% of that uncertainty, thereby providing the ability to reducing that wasted power.

### SAMENVATTING

Om de toenemende gevoeligheid voor variatie in geïntegreerde schakelingen te voorkomen, worden bedrijfsparameters (bijv. voedingsspanning) op een specifieke manier exclusief voor elke chip aangepast. AVS is een standaard techniek die vaker wordt toegepast om proces-, spanning- en temperatuurvariaties te compenseren. Vanwege kostenen complexiteitsredenen worden AVS-technieken meestal geïmplementeerd door middel van on-chip prestatiemonitoren (PMB's genaamd) die snelle evaluatie van de prestaties mogelijk maken tijdens productie of gebruik. Dergelijke on-chip monitoring technieken berekenen de bedrijfsparameters op basis van responsen van de prestatiemonitoren of door het monitoren van de kritieke paden van het circuit. In dit proefschrift concentreren we ons op AVS-technieken, die de bedrijfsparameters berekenen met behulp van responsen van on-chip prestatiemonitoren zonder interactie met het circuit tijdens productie. We bespreken de uitdagingen die deze monitoringmethodologieën met zich meebrengen, in termen van nauwkeurigheid en effectiviteit. We laten zien dat de nauwkeurigheid van deze technieken afhankelijk is van het circuit en vereist een toegevoegde ontwerpmarge van ten minste 15%. Bovendien laten we met behulp van siliciummetingen van een nanometrisch FD-SOI chip zien dat de vereiste ontwerpmarge hoger is dan 10% van de klokperiode, wat leidt tot een aanzienlijke verspilling van energie. In dit proefschrift introduceren we de nieuwe methode voor het gebruik van delaytestpatronen inclusief TF-, SDD- en PDLY-testpatronen voor het uitvoeren van AVS tijdens IC-productie. De voorgestelde methode kan de behoefte aan PMB's elimineren, terwijl de nauwkeurigheid van de prestatiemeting wordt verbeterd. De basisvereiste voor het gebruik van op delay-testpatronen voor AVS is dat er een redelijke correlatie moet zijn tussen de frequentie die de chip kan bereiken tijdens testen en de werkelijke frequentie van de chip. Simulatie resultaten van ISCAS99 testcircuits met een 28 nm FD-SOI-bibliotheek laten zien dat het gebruik van delay-testpatronen maar kleine meetfouten veroorzaken, namelijk, 5,33% voor TF-testen, 3,96% voor SDD-testen en 1,85% voor PDLY-testen. We hebben dezelfde analyse uitgevoerd met behulp van een 65 nm technologie, dat dezelfde resultaten liet zien, wat aangeeft dat deze testgebaseerde benadering kan worden gebruikt voor verschillende technologieën. We hebben ook twee verschillende experimenten op silicium uitgevoerd op een 28 nm FD-SOI CPU om de effectiviteit van de op TF gebaseerde aanpak te onderzoeken. De resultaten van het eerste experiment, waarbij de prestatieberekening van functionele testpatronen vergeleken wordt met de TF gebaseerde aanpak, laten een zeer nauwe correlatie zien, wat de effectiviteit van de TF-aanpak aantoont. Het tweede experiment vergelijkt de nauwkeurigheid van spanningsberekening van PMB's met de op TF gebaseerde aanpak. De resultaten tonen aan dat de PMB-aanpak slechts 85% van de onzekerheid in spanningsmetingen kan identificeren, wat resulteert in aanzienlijk energieverspilling. Ter vergelijking: de op TF gebaseerde aanpak kan 99% van die onzekerheid identificeren, waardoor veel minder energieverspilling wordt veroorzaakt.

# **CONTENTS**

| Su | ımmary                                                         | ix               |  |  |

|----|----------------------------------------------------------------|------------------|--|--|

| Sa | menvatting                                                     | хi               |  |  |

| 1  | Introduction  1.1 Background and related work                  | 1<br>1<br>1<br>4 |  |  |

|    | 1.2 Motivation1.3 Our contribution1.4 Thesis organization      | 7<br>8<br>9      |  |  |

| 2  | Low power techniques for single and multicore systems          | 11               |  |  |

| 3  | AVS techniques using on-chip performance monitors              | 19               |  |  |

| 4  | TF-based AVS 2                                                 |                  |  |  |

| 5  | SDD-based and PDLY-based AVS                                   | 41               |  |  |

| 6  | Impact of Technology Scaling on Delay Testing for Low-Cost AVS | 51               |  |  |

| 7  | Summary and conclusions                                        | 65               |  |  |

| Li | st of Publications                                             | 69               |  |  |

| Cı | ırriculum Vitæ                                                 | 71               |  |  |

1

## INTRODUCTION

Power has been one of the primary design constraints and performance limiters in the semiconductor industry such that reducing power consumption can extend battery lifetime of portable systems, decrease cooling costs, as well as increase system reliability.

The continuous progress in microprocessors performance has been propelled mostly by technology scaling, which results in exponential growth both in transistor density and performance. However, as technology scaling enters the nanometer regime, CMOS devices are facing many problems such as increased leakage currents, large parameter variations, as well as low reliability and yield [1]. The inability to continue to lower the supply voltage halted the ability to increase the clock speed without increasing power dissipation. Therefore, in order to avoid encountering a stall in the future growth of computing performance, high performance microprocessors had to enter the multicore era [2]. However, the growth in the number of cores causes super-linear growth in non-core related area and power; accordingly, the power dissipation problem did not disappear with the shift towards the new multicore era [3, 4]. Therefore, in addition to a focus on multicore design and parallel processing, we need research and development focussed on much more power-efficient computing systems at various levels of abstraction.

In this chapter, Section 1.1 discusses the background and related work. This is followed by Section 1.2 which introduces the limitations of the state of the art industrial AVS methods, which is the reason of investigating new methods for AVS. Next, we define our contributions in Section 1.3. Finally, we describe the thesis organization in Section 1.4.

#### 1.1. BACKGROUND AND RELATED WORK

#### **1.1.1.** Low power techniques

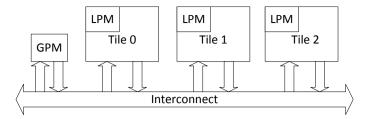

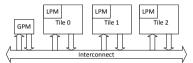

Figure 1.1 displays a system model that will be considered in this thesis. The model consists of a number of tiles (either a processor or memory), each of which contains a local power management (LPM) unit for local power optimizations. The model also contains a global power management (GPM) unit, which aims to reduce power considering all tiles and interactions among them. The figure also shows the interconnect, which is used for

2 1. Introduction

Figure 1.1: System model block diagram to classify power reduction techniques

the interaction among tiles and GPM. Notably, techniques used for LPM are applicable to both single and multicore systems. Based on Figure 1.1, power reduction techniques can be applied to either the tiles or the interconnects, whether inside or outside the cores.

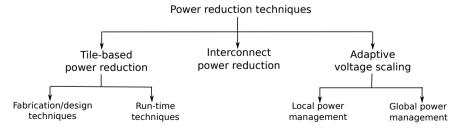

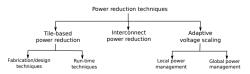

A high-level taxonomy of the power reduction techniques for both single and multicore systems is illustrated in Figure 1.2. Many techniques have been proposed to achieve power reduction at different levels of abstraction, some of which require modification of the process technology, achieving power reduction during fabrication/design stage. Others are run-time techniques that require architectural support, and in some cases, technology support as well. Based on Figure 1.2, there are different techniques which aim to reduce power either during fabrication/design or runtime in the tiles. Power consumption of single and multicore systems can also be reduced in the interconnects or through adaptive voltage scaling techniques in the local and global power management units to dynamically manage power during run-time [5, 6].

More detailed survey on low power techniques for single and multicore systems is given in Chapter 2.

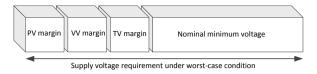

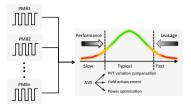

With the ongoing scaling of CMOS technologies, variations in process, supply voltage, and temperature (PVT) have become serious concern in integrated circuit design. Therefore, an individual safety margin for each variation source is added on the top of the supply voltage needed for the nominal case as depicted in Figure 1.3. However, this classical worst-case analysis is quite pessimistic and leads to wasting both system power and/or performance. To overcome this problem, various adaptive design strategies have been proposed. The basic idea is to adapt the supply voltage to the optimal value, based on the current operation conditions of the system so that power is saved; variations are compensated, while maintaining the desired performance.

Figure 1.2: Taxonomy of various methods for total power reduction

Figure 1.3: Schematic of the worst-case guard-banding approach (PV, VV, and TV stand for process, voltage, and temperature variations, respectively)

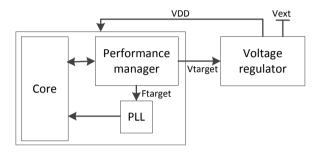

Figure 1.4: Architecture of an AVS system

Adaptive voltage scaling (AVS) systems are very efficient in saving power since the supply voltage has a profound impact on the operating frequency and power consumption of an integrated circuit. Typically, logic delay increases as  $V_{DD}$  reduces and power consumption increases super linearly with  $V_{DD}$ . Whenever maximum performance is not required, supply voltage can be scaled so that power can be saved while the system can still meet the timing constraints. Figure 1.4 shows the overall architecture of an AVS system [7]. The performance manager predicts performance requirements. Once performance requirement is determined, the performance manager sets the voltage and frequency to values that are just enough to accomplish the performance target of the system. The target frequency is sent to the phase-locked loop (PLL) to accomplish frequency scaling. Based on the target voltage, the voltage regulator is programmed to scale the supply voltage up/down until target voltage is achieved.

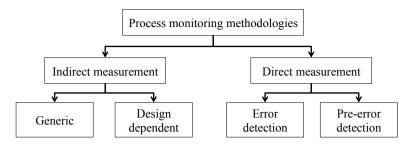

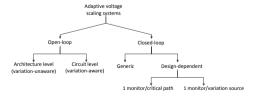

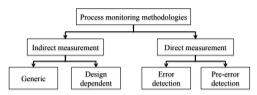

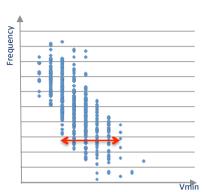

Thus, accurate circuit performance estimation is required to set the optimal voltage for the circuit so that the required performance is guaranteed. AVS techniques use on-chip performance monitors to estimate the actual performance of the circuit. Such on-chip performance monitors either have no interaction with the circuit or monitor the actual critical paths of the circuit. Based on this feature, we propose a taxonomy of process monitoring methodologies illustrated in Figure 1.5. According to this figure, AVS is done either using indirect measurement approaches or direct measurement approaches. Indirect measurement approaches estimate actual frequency of the circuit through correlating frequency responses of performance monitors to the circuit frequency, whereas, direct measurement approaches set the circuit operating parameters by monitoring the actual critical paths of the circuit. These two process monitoring methodologies (direct and indirect) will be discussed and illustrated in more details in the next section.

4 1. Introduction

Figure 1.5: Classification of process monitoring methodologies

#### 1.1.2. PROCESS MONITORING METHODOLOGIES

#### INDIRECT MEASUREMENT APPROACHES

These approaches embed one or various performance monitors in the chip structure. Due to within-die variations, it is more efficient to place various performance monitors close or inside the block which is being monitored so that all types of process variations are captured and taken into account for voltage adaptation. The number of performance monitors depends on the size of the chip. There is no interaction between performance monitors and the circuit.

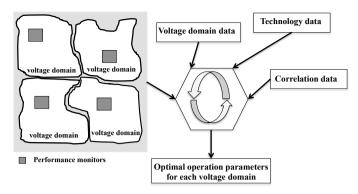

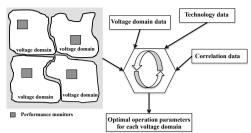

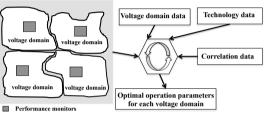

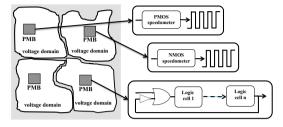

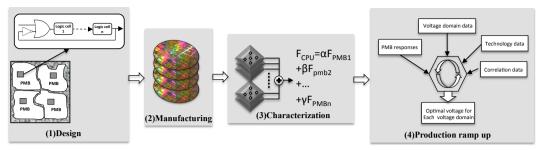

To be able to estimate the circuit frequency based on performance monitor responses during production, the correlation between performance monitors and circuit frequency should be measured during characterization, which is an earlier stage of manufacturing [8]. This procedure is done for the amount of test chips representative of the process window to find the correlation between performance monitors and circuit frequencies. Once the performance monitors are tuned to the design during characterization, they are ready to be used for voltage estimation for each chip during production. Figure 1.6 shows an example of a chip with multiple voltage islands, among which performance monitors are distributed. During production, based on the frequency responses from these monitors, the circuit frequency is estimated so that operating parameters can be adapted to each voltage domain of the chip.

Various performance monitoring structures have been proposed from simple generic ring oscillators to more complicated design dependent critical path replicas. The technique presented in [9] implements replica-paths, representing the critical paths of the circuit. Alternatively, the critical path replica can be replaced by fan-out of 4 (FO4) ring oscillator [10] or a delay line [11]. They claim that with varying operating conditions, the timing of monitors will change similarly to the actual critical path. Moreover, the method presented in [12] synthesizes a single representative critical path (RCP) for post-silicon delay prediction. They claim that the RCP is designed such that it is highly correlated to all critical paths for some expected process variations.

However, as technology scaling enters the nanometer regime, specially from 45 nm onwards, finding one unique critical path has become impossible. Depending on process and operational conditions (the process corner, voltage and temperature variations, and also workload) many different timing paths might become critical. Therefore for real circuits, the concept of finding only one critical path and creating a critical path replica

Figure 1.6: Operating parameter estimation using indirect measurement approaches

as a performance monitor is too simplistic. As a result, regardless of using generic ring oscillators or design dependent replica paths, the characterization phase should be done to find the correlation between monitoring responses and the actual performance of the circuit.

#### DIRECT MEASUREMENT APPROACHES

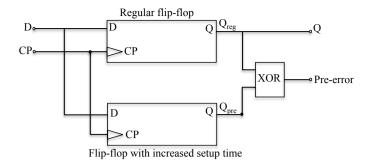

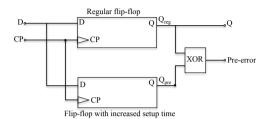

Direct measurement approaches estimate operation parameters by monitoring actual critical paths of the circuit. These approaches add one in-situ delay monitor per critical path. In-situ delay monitors are special latches or flip-flops, included at the end of critical paths to report the timing behavior of the circuit [13]. Circuit delay characterization using in-situ delay monitors can be done in two different ways. The first is by observing the regular operation of a circuit and to detect timing errors in the circuit itself during operation. With this error information, the critical operation parameters, which are needed for correct operation, can be determined. The second possibility is to observe an overcritical system. Here, a test module which is always slower than the most critical part of the chip is observed, and as soon as the test module fails, the system predicts a delayed data transition called a pre-error [14].

For the in-situ monitors, which are able to detect timing errors, error recovery circuits are needed to repeat single computations after malfunction. In contrast, for in-situ approaches which detect pre-errors, no additional hardware effort and complexity for the recovery circuitry is needed, thus, these approaches are easier to manage. Figure 1.7 shows an in-situ delay flip flop which detects pre-errors. These in-situ flips flops detect pre-errors when the timing slack in critical paths drops below a certain value. The idea is to reduce the operation parameters as long as no pre-error is detected and to raise the operation parameters as soon as the pre-error rate is above a certain value.

With regard to accuracy and tuning effort, direct measurement approaches are very accurate and no tuning effort is needed, since they monitor the actual critical path of the circuit, and there is no need to add safety margins on top of the measured parameters due to inaccuracies. However, for indirect measurement approaches, since there is no interaction between performance monitors and the circuit, the correlation between performance monitor responses and the actual performance of the circuit is estimated

6 1. Introduction

Figure 1.7: Structure of in-situ flip-flops which detect pre-errors

during the characterization phase using an amount of test chips representative of the process window. Since there are discrepancies in the responses of the same performance monitors from different test chips, the estimated correlation between the frequency of performance monitors and the actual performance of the circuit could be very pessimistic, which results in wasting power and performance. Hence in terms of accuracy and tuning effort, direct measurement approaches always win.

On the other hand, in terms of planning effort and implementation risk, direct measurement approaches are considered very risky and intrusive since adding flip-flops at the end of critical paths requires extensive modification in hardware and thus incurs a high cost. Moreover, for some sensitive parts of the design, such as CPU and GPU, which should operate at high frequencies, implementing direct measurement approaches is quite risky since it affects planning, routing, timing convergence, area, and time to market. Therefore, indirect measurement approaches are considered more acceptable in terms of planning and implementation risk, since there is no interaction between performance monitors and the circuit. Hence, performance monitors can even be placed outside the macros being monitored, but not too far due to within die variations. Consequently, indirect measurement approaches seem more manageable due to the fact that they can even be considered as an incremental solution for existing devices and the amount of hardware modification imposed on the design is very low. As a result, according to the application, one can decide which technique more suits a specific design. For medical applications for example, accuracy and power efficiency are far more important than the amount of hardware modification and planing effort, while, for nomadic applications, such as mobile phones, tablets, and gaming consoles, cost and the amount of hardware modification are considered the most significant.

In this thesis our focus is on AVS implementation on devices used for nomadic applications. Thus, the performance monitors (which we call Process Monitor Boxes (PMBs) from now on) we consider in this thesis use indirect measurement approaches for performance estimation. PMBs are ring oscillators designed based on the most used cells extracted from the potential critical paths of the design, reported by static timing analysis. So, based on the design, some standard logic cells are put in an oscillator to form performance monitors, which will be distributed among the chip to capture all kinds of variations. During characterization, PMBs are tuned to the design so that during pro-

1.2. MOTIVATION 7

Figure 1.8: Inaccuracy in the optimal operating voltages estimated using different PMBs

duction, according to the frequency responses of PMBs, the voltages are adapted to each chip.

A more detailed survey and discussion of AVS approaches is given in Chapter 2 and in Chapter 3.

#### 1.2. MOTIVATION

Although PMB-based AVS is very fast during production, as technology scaling enters the nanometer regime, this technique is showing limitations regarding time to market, cost, and effectiveness in power saving. These limitations are discussed below:

- Long characterization time—The correlation process (i.e., finding the correlation between PMB responses and the actual frequency of the circuit) should be done for an amount of test chips representative of the process window to make sure (for all manufactured chips) voltage estimation based on PMB responses is correlated with application behavior. This correlation process has a negative impact in terms of design effort and time to market, which makes these approaches rather expensive.

- **Incomplete functional patterns**—Finding a complete set of functional patterns that reflects the real system performance could be very tricky specially for complex systems. Also, we note that identifying the most critical part of the application is not possible in most cases.

- Not a solution for general logic—The fact that functional patterns are used for the

correlation process makes PMB approaches not suitable for general logic, since

even though using functional patterns for programmable parts of the design such

as CPU and GPU is possible, the rest of the design such as interconnects are difficult to be characterized using this approach.

- **Limited effectiveness**—Since there are discrepancies in the responses of the same PMBs from different test chips, the estimated correlation between the frequency of PMBs and the actual performance of the circuit could be very pessimistic, which

8 1. Introduction

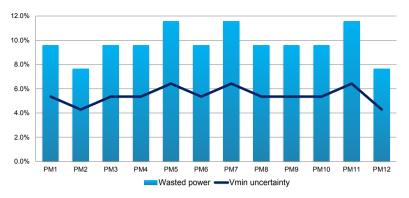

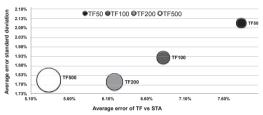

results in wasting power and performance. To validate our claim of low accuracy of PMB approaches, we have done silicon measurement on 625 devices manufactured using nanometric FD-SOI technology. 12 performance monitors (PM) are embedded in each device. We measured the amount of Vmin discrepancy for all 12 monitors, the result of which is presented in Figure 1.8. This figure also presents the wasted power as a results of inaccuracy in Vmin estimation using performance monitors. Results show that optimal voltage estimation based on PMBs lead to nearly 10% of wasted power on average and 7.6% in the best case, when a single PMB is used for performance estimation.

Therefore, we can conclude that trying to predict performance of the many millions of paths in a given design based on information from a single unique path could be difficult and in many cases inaccurate. This results in high costs, extra margins, and consequently yield loss and performance limitations. This approach might work for older well-understood technologies that have become robust with time and when only very few parameters influence performance, such as voltage, process corner, and temperature. However, in deep sub-micron technologies, as intra-die variation and interconnect capacitances are becoming predominant, it is more complex to estimate the performance of the whole design based on few PMBs. Hence, to improve the accuracy, we should use an alternative approach that increases the number of paths we take into account for performance estimation. Moreover, the more the characterization effort can be reduced, the more cost effective the AVS approach will be.

#### 1.3. OUR CONTRIBUTION

We can sum up our contributions in this thesis as follows.

- We propose a comprehensive taxonomy of power reduction techniques for both tiles and the interconnect as well as run-time techniques for adaptive voltage scaling. We discuss several techniques from each class in the taxonomy along with examples as well as reported power reduction values.

- 2. An overview of various on-chip performance monitors for online and offline AVS including a discussion of the pros and cons of each approach.

- 3. We Investigate the limitations of critical path replica performance monitors in terms of accuracy and effectiveness for ISCAS'99 benchmarks using the Nangate 45 nm open cell library with 4 different process corners.

- 4. A detailed investigation of PMB approaches in terms of accuracy and effectiveness using 29 ISCAS'99 bench- marks with an industrial grade 28 nm FD-SOI library for 42 different process corners with different characteristics in terms of process and environmental variations as well as aging.

- 5. Proposing the new concept of using delay testing including transition fault testing (TF), single delay defect testing (SDD), and path delay testing (PDLY) for performance estimation during production as an alternative for PMBs.

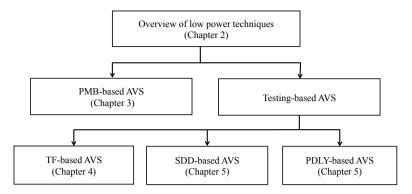

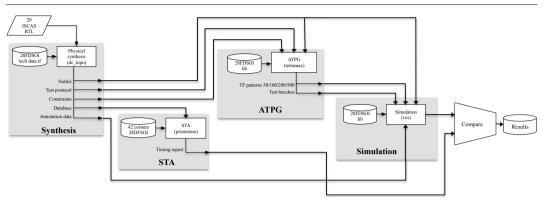

Figure 1.9: Overview of the different thesis topics

- 6. A detailed investigation on the delay testing approach including TF, PDLY, and SDD in terms of accuracy and effectiveness using 29 ISCAS'99 benchmarks with 28 nm FD-SOI library for 42 different process corners with different characteristics in terms of process and environmental variations as well as aging.

- 7. A study on the impact of technology scaling on accuracy and effectiveness of the delay testing approach using 65 nm and 28 nm FD-SOI libraries.

#### 1.4. Thesis organization

The various chapters of the thesis and their relationships is presented in Figure 1.9. The thesis is organized as follows.

In **Chapter 2**, we give a survey of low power techniques for single and multicore systems.

In **Chapter 3**, we discuss the state of the art for AVS techniques that are currently being used in industry. We also introduce their limitations in terms of efficiency and cost.

In **Chapter 4**, we introduce our new proposal for AVS using Transition Fault test patterns (TF).

In **Chapter 5**, we discuss our new AVS technique using Single Delay Defect (SDD) and Path Delay (PDLY) testing.

In **Chapter 6**, we investigate on the impact of technology scaling on the effectiveness of AVS techniques using delay testing.

In **Chapter 7**, we summarize the finding s of the thesis and present the conclusions.

10 REFERENCES

#### REFERENCES

[1] Y.B. Kim, *Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics*, Trans. on Electrical and Electronic Materials, vol. 11, pp. 93-105, 2010.

- [2] S.H. Fuller and L.I. Millett, *The Future of Computing Performance: Game Over or Next Level?*, The National Academy of Sciences, 2011.

- [3] L. Spracklen and S.G. Abraham, *Chip Multithreading: Opportunities and Challenges*, in HPCA, pp. 248-252, 2005.

- [4] H. Esmaeilzadeh, et al., *Dark Silicon and the End of Multicore Scaling*, in ISCA, vol. 46, pp. 5–26, 2011.

- [5] Z. Al-Ars, *DRAM Fault Analysis and Test Generation*, Delft University of Technology, Delft, Netherlands, June, 2005.

- [6] Z. Al-Ars, S. Hamdioui, G. Gaydadjiev, S. Vassiliadis, *Test Set Development for Cache Memory in Modern Microprocessors*, Trans. on VLSI, vol. 16, no. 6, pp. 725-732.

- [7] M. Elgebaly and M. Sachdev, *Variation-Aware Adaptive Voltage Scaling System*, in TVLSI, vol. 15, no. 5, pp. 560-571, 2007.

- [8] T. Chan and A.B. Kahng, *Tunable Sensors for Process-Aware Voltage Scaling*, in IC-CAD, pp. 7-14, 2012.

- [9] A. Drake, et al., A Distributed Critical-Path Timing Monitor for a 65nm High-Performance Microprocessor, in ISSCC, pp. 398-399, 2007.

- [10] TD. Burd, et al., *A dynamic voltage scaled microprocessor system*, in ISSCC, pp. 294-295, 2000.

- [11] J. Kim and M.A. Horowitz, *An efficient digital sliding controller for adaptive power-supply regulation*, in IJSSC, vol. 37, no. 5, pp. 639-647, 2002.

- [12] Q. Liu and S.S. Sapatnekar, *Capturing Post-Silicon Variations Using a Representative Critical Path*, in TCAD, vol. 29, no. 2, pp. 211-222, 2010.

- [13] M. Wirnshofer, et al., A Variation-Aware Adaptive Voltage Scaling Technique based on In-Situ Delay Monitoring, in DDECS, pp. 261-266, 2011.

- [14] M. Eireiner, et al., *In-Situ Delay Characterization and Local Supply Voltage Adjustment for Compensation of Local Parametric Variations*, in IJSSC, vol. 42, no. 7, pp. 1583-1592, 2007.

# LOW POWER TECHNIQUES FOR SINGLE AND MULTICORE SYSTEMS

#### **SUMMARY**

This chapter surveys state of the art low-power techniques for both single and multicore systems. Based on our proposed power management model for multicore systems, we present a classification of total power reduction techniques including both leakage and active power. According to this classification, three main classes are discussed: power optimization techniques within the cores, techniques for the interconnect and techniques applicable for the whole multicore system. This chapter describes several techniques from these classes along with a comparison. For the whole multicore system, we focus on adaptive voltage scaling and propose a comprehensive taxonomy of adaptive voltage scaling techniques, while considering process variations.

This chapter is based on the following paper.

**Zandrahimi, M.**; Al-Ars, Z., *A Survey on Power Low-Power for Single and Multicore Systems*, International Conference on Context-Aware Systems and Applications (ICCASA), 15-16 October 2014, Dubai, United Arab Emirates.

# A Survey on Low-Power Techniques for Single and Multicore Systems

Mahroo Zandrahimi Delft University of Technology Delft, the Netherlands m.zandrahimi@tudelft.nl

#### ABSTRACT

This paper surveys state of the art low-power techniques for both single and multicore systems. Based on our proposed power management model for multicore systems, we present a classification of total power reduction techniques including both leakage and active power. According to this classification, three main classes are discussed: power optimization techniques within the cores, techniques for the interconnect and techniques applicable for the whole multicore system. This paper describes several techniques from these classes along with a comparison. For the whole multicore system, we focus on adaptive voltage scaling and propose a comprehensive taxonomy of adaptive voltage scaling techniques, while considering process variations.

#### 1. INTRODUCTION

Power has been one of the primary design constraints and performance limiters in the semiconductor industry such that reducing power consumption can extend battery lifetime of portable systems, decrease cooling costs, as well as increase system reliability.

The continuous progress in microprocessors has been maintained mostly by technology scaling, which results in exponential growth both in device density and performance. However, as the technology scaling enters nanometer regime, CMOS devices are facing many problems such as increased leakage currents, large parameter variations, low reliability and yield [1]. The inability to continue to lower the supply voltage halted the ability to increase the clock speed without increasing power dissipation. Therefore, in order to avoid encountering a stall in the future growth of computing performance, high performance microprocessors had to enter the multicore era [2]. However, the growth in the number of cores causes super-linear growth in non-core area and power; accordingly, the power dissipation problem did not disappear in the new multicore regime [3, 4]. Therefore, in addition to a focus on multicore design and parallel processing, we need research and development on much more

Zaid Al-Ars

Delft University of Technology

Delft, the Netherlands

z.al-ars@tudelft.nl

Figure 1: System model block diagram

power-efficient computing systems at various levels of abstraction.

There are various power reduction techniques published in the literature. This paper provides a survey of these techniques. Fig. 1 displays a system model that will be considered in this survey. The model consists of a number of tiles (either a processor or memory), each of which contains a local power management (LPM) unit for local power optimizations. The model also contains a global power management (GPM) unit, which aims to reduce power considering all tiles and interactions among them. The figure also shows the interconnect, which is used for the interaction among tiles and GPM. Notably, techniques used for LPM are applicable to both single and multicore systems. Based on Fig. 1, power reduction techniques can be applied to either the tiles or the interconnects, whether inside or outside the cores.

A high-level taxonomy of the power reduction techniques for both single and multicore systems is illustrated in Fig. 2. Many techniques have been proposed to achieve power reduction at different levels of abstraction, some of which require modification of the process technology, achieving power reduction during fabrication/design stage. Others are run-time techniques that require architectural support, and in some cases, technology support as well. Based on Fig. 2, there are different techniques which aim to reduce power either during fabrication/design or runtime in the tiles. Power consumption of single and multicore systems can also be reduced in the interconnects or through adaptive voltage scaling techniques in the local and global power management units to dynamically manage power during run-time. The contributions of this survey are as follows:

• We propose a comprehensive taxonomy of power reduction techniques for both tiles and the interconnect as well as run-time techniques for adaptive voltage scaling.

Figure 2: Taxonomy of total power reduction

- We discuss several techniques from each class in the taxonomy along with examples as well as reported power reduction values.

- We address various design and manufacturing issues, which degrade the effectiveness of power reduction techniques such as process and environmental variations and describe several low-power techniques considering these effects.

The rest of this paper is organized as follows. Section 2 presents low-power techniques that are applied either during fabrication/design or run-time stage to the tiles. Section 3 discusses interconnect low-power techniques that are applied dynamically during run-time. Section 4 specifically focuses on adaptive voltage scaling, which is widely used for run-time power optimization under process variations. Finally Section 5 concludes the paper.

#### 2. TILE-BASED POWER REDUCTION

In this section we discuss the fabrication/design as well as run-time techniques for power reduction in the tiles for both single and multicore systems from architecture level to circuit level

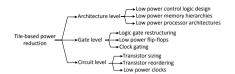

Power consumption of the tiles of single and multicore systems can be diminished at different levels of abstraction from system to layout, among which we will investigate various techniques at architecture, gate, and circuit levels in details. Fig. 3 illustrates a taxonomy of techniques for power reduction in the tiles from architecture to circuit level.

Based on Fig. 3, the tile power at architecture level can be cut back through low power control logic designs, low power memory hierarchies, and low power processor architectures. To explain low power control logic designs, assume the control logic of a processor as a finite state machine (FSM), which activates the appropriate circuitry for each state. Accordingly, optimizations in FSMs can be done for power reduction. Encoding FSM states to minimize the switching activity, or decomposing the FSM into sub-FSMs and activating only the circuitry needed for the currently executing sub-FSM are some examples of FSM optimizations throughout the processor [6]. A summary of attainable power reduction from this and other techniques is given in Table 1. Applying both of these techniques at the same time reduces power from 30-90%, while increasing area from 20-120%.

Another architecture level solution could be designing low power memories and memory hierarchies. Power dissipation in memories can be diminished in two ways, either by reducing the power dissipated in a memory access, or by reducing the number of memory accesses [5]. Moreover, splitting memory into smaller sub-systems is an effective way to reduce power consumed in a memory access. This can be done by partitioning memory into smaller, independently accessible components in different granularities so that only the needed circuitry is activated in each memory access [7]. A combination of subbanking, multiple line buffers and bit-line segmentation can reduce the on-chip cache power dissipation by as much as 75% in a technology-independent manner without compromising the processor cycle time. Augmenting the memory hierarchy with specialized cache structures is another popular method to save power by reducing memory hierarchy accesses. A simple example is a trace cache, which stores traces of instructions in their executed order rather than their compiled order. Hence, if an instruction sequence is already in the trace cache, it does not need to be fetched from the instruction cache and can be decoded di-

Figure 3: Taxonomy of tile-based power reduction

rectly from the trace cache [8]. However, conventional trace caches (CTC) may increase power in the fetch unit because of the simultaneous access to both the trace cache and the instruction cache. Dynamic direction prediction-based trace cache (DPTC), which avoids simultaneous accesses to the trace cache and the instruction cache achieve 38.5% power reduction over CTC, while only trading a 1.8% performance overhead compared to CTC [8].

Another method to save power at architecture level is through adaptive processor architectures, which aim to save power by activating minimum hardware resources needed for the code that is executing. Adaptive caches and adaptive instruction queues are two examples. In an adaptive cache, storage elements (lines, blocks, or sets) can be selectively activated based on the workload. One example of such a cache is the drowsy cache whose lines can be placed in a drowsy mode where they dissipate minimal power, but retain data during drowsy mode and can be activated instantly [9]. In adaptive instruction gueues, only the partitions that contain the currently executing instructions are activated at any time. For example, the heuristic proposed in [10], periodically measures the IPC (instructions per cycle) over fixed length intervals. If the IPC of the current interval is smaller than the previous interval, the size of the instruction queue is increased to enhance the throughput. The drowsy cache technique reduces power up to 53% with a performance overhead of 4.06-12.46%. Also, the adaptive instruction queue method achieves up to a 70% power reduction, while the complexity of the additional circuitry needed to achieve this result is almost negligible.

At gate level, logic gate restructuring is one simple method for power reduction. The idea is that since there are many ways to build a circuit out of logic gates, thus, how to arrange the gates and their input signals is important to power consumption [5]. Another possible solution is using low power flip-flops. Power consumption in flip-flops consists of the power dissipated in the clock signal, internal switching, and output transitions. Most of these low power designs for flip-flops reduce the switching activity or the power dissipated by the clock signal. Another method, which is very effective for power reduction at gate level is clock gating. Since clock is always active, and makes two transitions per cycle, it consumes about 40% of total processor power, so clock gating which inhibits clock to unused blocks is useful for power reduction.

Transistor sizing reduces the width of transistors based on the fact that reducing the width of transistors causes an increase in transistor delay, which leads to dynamic power reduction. Thus, the transistors that lie away from the critical paths of a circuit are usually the best candidates for this technique. Algorithms for applying this technique usually associate with each transistor a tolerable delay, which varies depending on how close the transistor is to the critical path. These algorithms then try to scale each transistor to be as

Figure 4: Taxonomy of Interconnect power reduction

small as possible without violating its tolerable delay [11]. Up to 15.3% power reduction can be achieved when 20% of the transistors are resized.

At circuit level, transistor reordering rearranges transistors to minimize their switching activity as their arrangement in a circuit affects power consumption [13, 14]. Another method is using low power clocks such as half-frequency and half-swing clocks, which reduce frequency and voltage respectively. Traditionally, hardware events such as register file writes occur on a rising clock edge. Half-frequency clocks synchronize events using both edges, and they tick at half the speed of regular clocks, thus cutting clock switching power in half. Reduced-swing clocks also often use a lower voltage signal, and hence reduce power quadratically [12]. As can be seen in Table 1, with transistor reordering, power can be reduced by up to 18% with minimum area and no performance overhead. The half-swing clocking scheme cuts power back by up to 67% in the whole chip and 75% in the clocking circuitry with minimal speed degradation.

#### 3. INTERCONNECT POWER REDUCTION

Interconnects dissipate power due to switching of interconnect capacitances. Since efforts to improve chip performance lead to smaller chips with more transistors and more densely packed wires carrying larger currents [15], there arise additional sources of power consumption such as crosstalk. Therefore, power dissipating in interconnects has become one of the important contributors to total chip power consumption. Several methods have been proposed to cut back power consumption in interconnects, each of which tries to reduce power by focusing on a different aspect of power dissipation in the interconnect as depicted in Fig. 4.

A popular way to diminish interconnect power consumption is to reduce switching activity using intelligent bus encoding systems such as bus-inversion, which ensures that at most half of the bus wires switch during a bus transaction [16]. However, because of the cost of the logic required to invert the bus lines, this technique is mainly used in external buses rather than the internal chip interconnect. For every data transmission, the number of wires that switch depends on the current and previous values transmitted. If the Hamming distance between these values is more than half the number of wires, then most of the wires on the bus will switch current. To prevent this, bus-inversion transmits the inverse of the intended value and asserts a control signal alerting recipients of the inversion. For example, if the current binary value to transmit is 110 and the previous was 000, the bus instead transmits 001, the inverse of 110. This technique decreases the I/O peak power dissipation by 50% and the I/O average power dissipation by up to 25%.

Low swing buses transmit the same information but at a lower voltage [17]. Traditionally, logic one is represented by +5 volts and logic zero is represented by -5 volts. However, in a low-swing system, logic one and zero are encoded using lower voltages, such as +300mV and -300mV. The input

signal is split into two signals of opposite polarity bounded by a smaller voltage range. The receiver sees the difference between the two transmitted signals as the actual signal and amplifies it back to normal voltage. This system has several advantages in addition to reduced power consumption. It is immune to crosstalk and electromagnetic radiation effects. Since the two transmitted signals are close together, any spurious activity will affect both equally without affecting the difference between them. However, the costs of increased hardware at the encoder and decoder should be considered. These buses decrease power from 62-78% with approximately 45% performance overhead.

As mentioned above, another source of power consumption in interconnects is crosstalk, which is false activity caused by activity in neighboring wires. One way of reducing crosstalk is to insert a shield wire between adjacent bus wires [18]. Since the shield remains deasserted, no adjacent wires switch in opposite directions, however, this solution doubles the number of wires. Another alternative is using coding systems which are resistant to crosstalk such as self-shielding codes [19, 20]. Just like traditional bus encoding system, a value is encoded and then transmitted. However, this system avoids opposing transitions on adjacent bus wires.

Bus segmentation is another effective technique for interconnect power reduction. In a traditional shared bus architecture, the entire bus is charged and discharged upon every access. Segmentation splits a bus into multiple segments connected by links that regulate the traffic between adjacent segments. Links connecting paths essential to a communication are activated independently, allowing most of the bus to remain powered down. Ideally, devices communicating frequently should be in the same or nearby segments to avoid powering many links. There are different algorithms for partitioning a bus into segments to benefit from this property as much as possible [21]. This technique achieves 24.6-37.21% power reduction with 6% area overhead.

Another solution to reduce power in interconnects is to reduce total capacitance, which is the principal behind adiabatic circuits [22]. These circuits reuse existing electrical charge to avoid creating new charge. In a traditional bus, when a wire becomes deasserted, its previous charge is wasted. A charge-recovery bus recycles the charge for wires about to be asserted. The saved power depends on transition patterns. No energy is saved when all lines rise. The most energy is saved when an equal number of lines rise and fall simultaneously. The biggest drawback of adiabatic circuits is the delay for transferring shared charge. This technique can achieve 28% power reduction.

#### 4. ADAPTIVE VOLTAGE SCALING

With the on going scaling of CMOS technologies, variations in process, supply voltage, and temperature (PVT) have become serious concern in integrated circuit design. Depending on their spatial correlation, process variations can be divided into three groups. Die-to-die (D2D) variations have a correlation distance larger than the die size, i.e., all transistors on a chip are affected the same way. Within-die (WID) variations have a correlation distance smaller than the chip size. Random variations are not correlated at all; every transistor is affected individually. Environmental variations such as power supply noise and crosstalk have also gained significance with increasing current densities and reduced geometric dimensions [32].

Figure 5: Schematic of the worst-case guard-banding approach (PV, VV, and TV stand for process, voltage, and temperature variations, respectively)

Figure 6: Architecture of an AVS system

Therefore, an individual safety margin for each variation source is added on the top of supply voltage needed for the nominal case as depicted in Fig. 5. However, this classical worst-case analysis is quite pessimistic and leads to power and performance be wasted. To overcome this problem, various adaptive design strategies have been proposed. The basic idea is to adapt the supply voltage to the optimal value, based on the current operation conditions of the system so that power is saved; variations are compensated, while maintaining the desired performance.

In this section, LPM techniques which are used in both single and multicore systems are explored. Specifically we focus on adaptive voltage scaling, which is widely used for run-time power optimization under process variations. In addition, we discuss GPM techniques which are specialized for multicore systems.

#### 4.1 Local power management unit

Adaptive voltage scaling (AVS) systems are very efficient in saving power since the supply voltage has a profound impact on the operating frequency and power consumption of an integrated circuit. Typically, logic delay increases as  $V_{DD}$  reduces and power consumption increases super linearly with  $V_{DD}$ . Whenever maximum performance is not required, supply voltage can be scaled so that power can be saved while the system can still meet the timing constraints. Fig. 6 shows the overall architecture of an AVS system [28]. The performance manager predicts performance requirements. Once performance requirement is determined, the performance manager sets the voltage and frequency just enough to accomplish the performance target of the system. The target frequency is sent to the phase-locked loop (PLL) to accomplish frequency scaling. Based on the target voltage, the voltage regulator is programmed to scale the supply voltage up/down until target voltage is achieved.

Figure 7: Taxonomy of adaptive voltage scaling systems

Thus, accurate circuit performance estimation is required so that the actual performance of the core running under the scaled voltage is monitored to guarantee a fail-safe operation, while maintaining the required performance [28]. A taxonomy of AVS systems is illustrated in Fig. 7. Based on whether the performance estimation is done early in manufacturing or during run-time, these techniques can be classified as either open or closed-loop [25]. The following subsections explore the commonly used AVS techniques.

#### 4.1.1 Open-loop adaptive voltage scaling

A typical open-loop adaptive voltage scaling system creates a pre-characterized LUT to find the corresponding minimum voltage for a given frequency target. Conventionally, the voltage levels for each domain, as well as the mapping between frequencies and voltages are determined at architecture level without considering variations. One example is the three domain dynamic voltage frequency scaling (DVFS) power management scheme proposed in [26]. In this architecture level technique, the voltage and frequency of each power domain are dynamically scaled according to the performance requirement of each domain. They assumed that each domain has a specific requirement of voltage and frequency due to different workloads that they execute. Using three power domains diminishes power by up to 65% compared to a single domain, while imposes 2.6% area and 9.5% power overhead on the system.

However, with the increasing effect of process variations as a result of technology scaling, the research has become more focused towards the variation-aware adaptive voltage scaling techniques at circuit level. A technique proposed in [27], utilizes a user and process driven dynamic voltage and frequency scaling scheme to adapt voltage to the frequency of a microprocessor in real-time according to processor needs. User-driven frequency scaling (UDFS) uses direct user feedback to determine the processor frequency for individual users. Process-driven voltage scaling (PDVS) creates an LUT which maps frequency and temperature to the operating minimum voltage considering process variations. Using both of these techniques at the same time reduces power by up to 50% for single task and 70% for multi-task workloads compared to Windows XP DVFS. However, since these techniques do not have a feedback mechanism, the LUT is heavily guard-banded to ensure reliable system operation which results in performance and energy wastes. At the same time, characterizing the LUT is a time consuming and expensive procedure. Thus, closed-loop schemes which take advantage of feedback mechanisms during run-time are more efficient in saving power.

#### 4.1.2 Closed-loop adaptive voltage scaling

A closed-loop adaptive voltage scaling system adjusts supply voltage by probing actual chip performance using onchip monitors, thus, margin required by open-loop systems can be recovered. To track timing performance of a chip, many approaches have been proposed. Based on Fig. 7, in terms of design point of view, performance monitors are classified into design dependent and generic[24].

#### Generic performance monitors

Generic performance monitors range from simple inverterbased ring oscillators [29] to more complex process-specific ring oscillators (RO) [30] and also alternative monitoring [36]

BCE

| Table 1. Reported power reduction values |         |                                           |                 |                                                                                     |  |  |

|------------------------------------------|---------|-------------------------------------------|-----------------|-------------------------------------------------------------------------------------|--|--|

| Reference                                | Section | Technique                                 | Power reduction | Comments                                                                            |  |  |

| [6]                                      | II.A    | Encoding FSM & decomposition to sub-FSMs  | 30% to 90%      | 20% to 120% area overhead                                                           |  |  |

| [7]                                      | II.A    | Splitting memory into smaller sub-systems | 75%             | sub-banking, bit-line segmentation, multiple-line buffers - no performance overhead |  |  |

| [8]                                      | II.A    | DPTC                                      | 38.5%           | 1.8% performance overhead over CTC                                                  |  |  |

| [9]                                      | II.A    | Drowsy cache                              | 53%             | 4.06% to 12.46% performance overhead                                                |  |  |

| [10]                                     | II.A    | Adaptive instruction queue                | 70%             | Complexity of additional circuitry is negligible                                    |  |  |

| [5]                                      | II.A    | Clock gating                              | up to 40%       | small area overhead                                                                 |  |  |

| [11]                                     | II.A    | Transistor sizing                         | up to 15.3%     | 20% of transistors are resized                                                      |  |  |

| [14]                                     | II.A    | Transistor reordering                     | 18%             | minimum area overhead, no performance overhead                                      |  |  |

| [12]                                     | II.A    | Half-swing clock                          | 67%-75%         | small speed degradation                                                             |  |  |

| [16]                                     | II.B    | Bus inversion                             | 50%-25%         | peak and average power reduction of I/O                                             |  |  |

| [17]                                     | II.B    | Low swing bus                             | 62% to 78%      | 45% performance overhead                                                            |  |  |

| [21]                                     | II.B    | Bus segmentation                          | 24.6% to 37.21% | 6% area overhead                                                                    |  |  |

| [22]                                     | II.B    | Adiabatic bus                             | 28%             | •                                                                                   |  |  |

| [26]                                     | III.A   | Three domain DVFS                         | 65%             | power overhead: 9.5%, area overhead: 2.6% compared to single domain                 |  |  |

| [27]                                     | III.A   | UDFS-PDVS                                 | 50% to 75%      | compared to Windows XP DVFS                                                         |  |  |

| [33]                                     | III.A   | Universal delay line                      | 13% to 27%      | area overhead: 0.01%, power overhead is negligible                                  |  |  |

| [23]                                     | III.A   | In-situ delay monitoring (over-critical)  | 13.5%           | compared to the worst-case design, prediction error rate: 1.10 <sup>-15</sup>       |  |  |

| [32]                                     | III.A   | In-situ delay monitoring (regular)        | 14%             | power overhead: 0.5%, area overhead: 10%                                            |  |  |

| [34]                                     | III.A   | Critical path replica                     | 11% to 78%      | highly dependent on the benchmark                                                   |  |  |

Table 1: Reported power reduction values

structure such as PLLs [31]. Although generic monitors are very simple to design and can be used in any product without customizations, they are inadequate to capture design characteristics, and there will be a large error in the measurements due to the difference in gate structure between the actual critical path and the delay monitor. So, delay estimation using generic monitors is less accurate and sometimes incurs larger margins. However, the generic performance monitor proposed in [33] tries to minimize the errors due to gate structure difference by utilizing certain chain of delay gates, as well as the errors due to the within die variations by distributing monitors among the chip. Each performance monitor, which is called a universal delay line, contains a ring oscillator and a counter. The ring oscillator is designed with double stacked NMOSs and PMOSs since this gate structure is the most dominant component in the critical path delay, which minimizes the error due to the gate structure difference. This technique decreases power by up to 27% with a negligible area overhead.

#### Design-dependent performance monitors

According to Fig. 7, some of the design-dependent techniques implement one monitor per variation source, while the others implement one monitor per critical path. One group of methods that utilize one monitor per critical path are based on in-situ delay monitors, which are special latches or flip-flops, included at the end of critical paths to report the timing behavior of the circuit in order to form a closed loop configuration for voltage adaptation [32]. Circuit delay characterization using in-situ delay monitors can be done in two different ways. The first is by observing the regular operation of a circuit and to detect timing errors in the circuit itself during operation. With the error information, the critical supply voltage, that is the minimum supply voltage which is needed for correct operation, can be determined. The second possibility is to observe an over-critical system. Here, a test module which is always slower than the most critical part of the chip is observed, and as soon as the test module fails, the system detects a late data transition called a pre-error[23]. The regular in-situ method achieves 14% power reduction using two power switches, while imposing 10% area overhead and 0.5% power overhead to the system. The over-critical method compared to the worst-case design reduces power to 13.5% with a negligible error rate of  $10^{-15}$ .

Another approach implements replica-paths, representing the critical paths of the circuit, thus, with varying operating conditions, the timing of the replica-path will change similarly to the actual critical path. So, the timing information of the replica-path can be used to control the supply voltage adaptively. Alternatively, the critical path replica can be replaced by fan-out of 4 (FO4) ring oscillator [34] or a delay line [35]. A safety margin is added to account for any mismatch between the ring oscillator (or the delay line) and the actual critical path. The FO4 technique achieves 11% power reduction for compute-intensive code; the power decreased by up to 78 % for non-speed-critical applications compared to operating at a fixed supply voltage.

smaller guard-band than critical path replica, prediction error rate: 2.8%

Several methods have been proposed which implement one monitor per variation source. For instance, the method presented in [36] synthesizes a single representative critical path (RCP) for post-silicon delay prediction. The RCP is designed such that it is highly correlated to all critical paths for some expected process variations. For both this and the critical path replica method, it is essential to guard-band the prediction. However, the RCP approach with 2.8% predication error rate requires a guard-band 31% smaller than the critical path replica method.

Although design-dependent monitors show good estimation accuracies, most of them rely on monitoring and characterization of one unique critical path, however, due to the increasing effect of process variations, finding one unique critical path is a hard task to do. Depending on the operating point, process corner, and workload many different timing paths might become critical, therefore, for real circuits the concept of finding one critical path and create a critical path replica as a performance monitor is too simplistic. Moreover, techniques that have one monitor per critical path incur high area overhead as well as long design turnaround time to the system[24].

#### 4.2 Global power management unit

We discussed various types of performance monitors used for AVS to locally manage power within each core. All the mentioned types of performance monitors are applicable for both single as well as multicore processors. As we discussed earlier in this section, process variations are static during operation and manifest themselves as D2D, WID variations, while temperature and voltage variations are dynamic. These affect both single as well as multicore processors. However, as the individual core size becomes smaller, there arises another source of process variations that specifically affects multicore systems, called core-to-core variations (C2C). C2C variations occur due to spatially correlated WID

variations, for example due to non-uniformity in the lithographic exposure field [38]. Thus, multicore processors are still threatened by increasing power consumption due to PVT variations since they require large design margins in the supply voltage resulting in large power consumption.

Dynamic power management of multicore processors is extremely important because it allows power savings when not all cores are used. AVS is one of the techniques that is widely used for power reduction in multicore processors. The percore performance data collected by performance monitors is sent to the global power management unit to decide the supply voltage. AVS for multicore processors can be performed at various levels of granularity: 1) Per-chip, the supply voltage is set globally for the whole chip, 2) Per-core, the supply voltage is set for each core, which means that only cores that require higher frequency are set to the higher supply voltage, while other cores operate at lower supply voltage or are completely shut down, 3) cluster-level, the voltage is set for each cluster which one or more cores are associated with.

#### CONCLUSION

This paper presented a classification of power reduction techniques in single and multicore systems. Three main classes have been discussed: the techniques which aim to reduce power either during fabrication/design or runtime in the tiles, run-time power reduction techniques for interconnects, and adaptive voltage scaling techniques to dynamically manage power during run-time. In addition, a number of design and manufacturing issues (such as process and temperature variations) have been taken into consideration. The paper also discussed a number of examples for each of the classes and presented the published power reduction numbers reported by their respective papers. A summary of these numbers has been listed along with the trade-offs in performance and/or area overhead incurred as a result.

#### Acknowledgments

This work is carried out under the BENEFIC project (CA505), a project labelled within the framework of CATRENE, the EUREKA cluster for Application and Technology Research in Europe on NanoElectronics.

#### REFERENCES

- [1] Y. B. Kim, Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics, Trans. On Electrical and Electronic Materials, vol. 11, pp. 93-105,2010.

- S. H. Fuller and L. I. Millett, The Future of Computing Performance: Game Over or Next Level?, The National Academy of Sciences, 2011.

- [3] L. Spracklen and S. G. Abraham, Chip Multithreading: Opportunities and Challenges, in HPCA, pp. 248-252, 2005.

- [4] H. Esmaeilzadeh, et. al, Dark Silicon and the End of Multicore Scalina. in ISCA, vol. 46, pp. 5âĂŞ26, 2011.

- V. Venkatachalam and M. Franz, Power Reduction Techniques for Microprocessor Systems, ACM Computing Surveys, vol. 37, no. 3, pp. 195-237, 2005.

- [6] F. Gao and J. P. Hayes, ILP-based optimization of sequential circuits for low power, in ISLPED, pp. 140-145, 2003.

[7] K. Ghose, B. Kamble, Reducing power in superscalar processor

- caches using subbanking, multiple line buffers and bit-line segmentation,in ISLPED, Pages 70-75, 1999.

- J. Hu, et. al, Using Dynamic Branch Behavior for Power-efficient Instruction Fetch, in ISVLSI, pp. 127-132. 2003.

- [9] S. N. Kim, et. al, Drowsy Instruction Caches: Leakage Power Reduction Using Dynamic Voltage Scaling and Cache Sub-bank Prediction, in MICRO, pp. 219-230, 2002.

- $[10]\,$  A. Buyuktosunoglu, et. al, An Adaptive Issue Queue for Reduced Power at High Performance, Proc. of the Inter. Workshop on Power-aware Computer Systems, pp. 25-39, 2001.

- [11] J. Ebergen, J. Gainsley, and P. Cunningham, Transistor sizing: How to control the speed and energy consumption of a circuit, Proc. of the Inter. Symp. on Asynchronous Circuits and Systems, pp. 51-61, 2004.

- [12] H. Kojima, S. Tanaka, and K. Sasaki, Half-Swing Clocking Scheme for 75% Power Saving in Clocking Circuitry, JSSC, vol. 30, no. 4, pp. 432-435, 1995.

- [13] E. Kursun, S. Ghiasi, and M. Sarrafzadeh, Transistor Level Budgeting for Power Optimization, in ISQED, pp. 116-121,

- [14] A. Sultania, D. Sylvester, and S. Sapatnekar, Transistor and Pin Reordering for Gate Oxide Leakage Reduction in Dual in ICCD, pp. 228-233, 2004. Tox circuits,

- [15] K. Banerjee and A. Mehrotra, Global interconnect warming, IEEE Circuits and Devices Magazine, pp. 16-32, 2001.

- [16] M. Stan and W. Burleson, Bus-invert coding for low-power in TVLSI, pp. 49-58, 1995.

- [17] H. Chang, J. Rabaey, Low-swing interconnect interface circuits, in ISLPED, pp. 161-166, 1998.

[18] C. N. Taylor, S. Dey, and Y. Zhao, Modeling and Minimization

- of Interconnect Energy Dissipation in Nanometer Technologies, in DAC, pp. 754-757, 2001

- [19] B. Victor and K. Keutzer, Bus encoding to prevent crosstalk delay, in ICCAD, pp. 57-63, 2001.

- delay, in ICCAD, pp. 57-63, 2001.

[20] K. N. Patel and I. L. Markov, Error correction and crosstalk avoidance in dsm busses, Proc. of ACM Inter. Workshop on System-Level Interconnect Prediction, pp. 9-14, 2003.

- [21] W. B. Jone, et. al, Design theory and implementation for in TODAES, vol. 8, issue low-power segmented bus systems, 1, pp. 38-54, 2003.

- [22] B. Biship, M. J. Irwin, Databus Charge Recovery: Practical Considerations, In ISLPED, pp. 85-87, 1999.

[23] M. Wirnshofer, et. al, A Variation-Aware Adaptive Voltage

- Scaling Technique based on In-Situ Delay Monitoring, DDECS, pp. 261-266, 2011.

- [24] T. Chan, et. al, DDRO: A Novel Performance Monitoring Methodology Based on Design-Dependent Ring Oscillators,

- in ISQED, pp. 633-640, 2012.

[25] T. Chan and A. B. Kahng, Tunable Sensors for Process-Aware Voltage Scaling, in ICCAD, pp. 7-14, 2012.

[26] J. Lee, B. G. Nam, and H. J. Yoo, Dynamic Voltage and

- Frequency Scaling (DVFS) Scheme for Multi-Domains Power Management, in ASSCC, pp. 360-363, 2007. [27] B. Lin, et. al, User and Process-Driven Dynamic Voltage and

- in ISPASS, pp. 11-22, 2009. Frequency Scaling,

- [28] M. Elgebaly and M. Sachdev, Variation-Aware Adaptive Voltage Scaling System, in TVLSI, vol. 15, no. 5, pp. 560-571,

- [29] T. Yamagishi, et. al, An Area-Efficient, Standard-Cell Based On-Chip NMOS and PMOS Performance Monitor for Process Proc. of IEEE Inter. Conf. on Cool Variability Compensation, Chips, pp. 1-3, 2012.

- [30] M. Bhushan, et. al, Ring Oscillators for CMOS Process Tuning and Variability Control, in TSM, Vol. 19, No. 1, pp. 10-18, 2006.

- [31] K. Kang, et. al, On-Chip Variability Sensor Using Phase-Locked Loop for Detecting and Correcting Parametric in TVLSI, vol. 18, no. 2, pp. 270-280, 2010. Timing Failures,

- [32] M. Eireiner, et. al, In-Situ Delay Characterization and Local Supply Voltage Adjustment for Compensation of Local Parametric Variations, in JSSC, vol. 42, no. 7, pp. 1583-1592, 2007.

- [33] Y. Ikenaga, et. al, A 27% Active-Power-Reduced 40-nm CMOS Multimedia SoC with Adaptive Voltage Scaling Using Distributed Universal Delay Lines, in JSSC, vol. 47, no. 4, pp. 832-840, 2012.

- TD. Burd, T. Pering, A. Stratakos, and R. Brodersen, dynamic voltage scaled microprocessor system, in ISSCC, pp. 294 âĂŞ 295, 2000.