# D-JRA2.2 Smart Grid ICT Assessment Method

Widl, Edmund; Spiegel, Michael; Findrik, Mislav; Bajraktari, Argon; Bhandia, Rishabh; Steinbrink, Cornelius; Heussen, Kai; Jensen, Tue Vissing; Mantafounis, Panagiotis; Dimeas, Aris

#### **Publication date** 2019

**Document Version**

Final published version

Citation (APA)

Widl, E., Spiegel, M., Findrik, M., Bajraktari, A., Bhandia, R., Steinbrink, C., Heussen, K., Jensen, T. V., Mantafounis, P., Dineas, A., Laukkanen, M., Divshali, P., Nguyen, V. H., Akroud, N., & Chodura, P. (2019). D-JRA2.2 Smart Grid ICT Assessment Method. European Commission H2020. https://erigrid.eu/wpcontent/uploads/2019/01/DL\_D-JRA2.2\_Smart\_Grid\_ICT\_assessment\_method\_2018-12-23.pdf

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# **European Research Infrastructure supporting Smart Grid Systems Technology Development, Validation and Roll Out**

# Work Package 08

# JRA2 - Co-Simulation based Assessment Methods

# Deliverable D8.2

# D-JRA2.2: "Smart Grid ICT assessment method"

Grant Agreement No: 654113

Funding Instrument: Research and Innovation Actions (RIA) – Integrating Activity (IA)

Funded under: INFRAIA-1-2014/2015: Integrating and opening existing national

and regional research infrastructures of European interest

Starting date of project: 01.11.2015

Project Duration: 54 months

Contractual delivery date: 31/10/2018

Actual delivery date: 23/12/2018

Name of lead beneficiary

for this deliverable: 1 AIT Austrian Institute of Technology GmbH

Deliverable Type: Report (R)

Security Class: Public (PU)

Revision / Status: released

#### **Document Information**

Document Version: 04

Revision / Status: released

All Authors/Partners Edmund Widl, Michael Spiegel, Mislav Findrik, Agron Ba-

iraktari / AIT

Rishabh Bhandia / TUD Cornelius Steinbrink / OFF Kai Heussen, Tue Jensen / DTU

Mantafounis Panagiotis-Timolewn, Aris Dimeas / ICCS-NTUA

Matti Laukkanen, Poria Divshali / VTT

Van Hoa Nguyen / GINP Nabil Akroud / OCT

Przemyslaw Chodura / DNVGL

**Distribution List** ERIGrid consortium members

## **Document History**

| Revision | Content / Changes                                    | Resp. Partner                                              | Date     |

|----------|------------------------------------------------------|------------------------------------------------------------|----------|

| 1        | Document structure generated                         | AIT                                                        | 10.09.18 |

| 2        | Draft inputs, first version for internal review      | AIT, TUD, OFF, DTU,<br>ICCS-NTUA, VTT,<br>GINP, OCT, DNVGL | 26.09.18 |

| 3        | Included feedback from internal review               | AIT                                                        | 12.10.18 |

| 4        | Included feedback from Security Advisory Group (SAG) | AIT                                                        | 07.12.18 |

# **Document Approval**

| Final Approval                   | Name                              | Resp. Partner  | Date     |

|----------------------------------|-----------------------------------|----------------|----------|

| Review Task Level                | Edmund Widl                       | AIT            | 26.09.18 |

| Review WP Level                  | Ron Brandl                        | Fraunhofer IEE | 10.10.18 |

| Review WP Level                  | Dimitrios Siagkas, Manikas Savvas | HEDNO          | 12.10.18 |

| Review Security Adv. Group (SAG) | Kieran McLaughlin                 | QUB            | 28.11.18 |

| Review Security Adv. Group (SAG) | Thomas Bleier                     | BSEC           | 06.12.18 |

| Review Steering Com. Level       | Thomas Strasser                   | AIT            | 23.12.18 |

#### Disclaimer

This document contains material, which is copyrighted by certain ERIGrid consortium parties and may not be reproduced or copied without permission. The information contained in this document is the proprietary confidential information of certain ERIGrid consortium parties and may not be disclosed except in accordance with the consortium agreement.

The commercial use of any information in this document may require a licence from the proprietor of that information.

Neither the ERIGrid consortium as a whole, nor any single party within the ERIGrid consortium warrant that the information contained in this document is capable of use, nor that the use of such information is free from risk. Neither the ERIGrid consortium as a whole, nor any single party within

the ERIGrid consortium accepts any liability for loss or damage suffered by any person using the information.

This document does not represent the opinion of the European Community, and the European Community is not responsible for any use that might be made of its content.

# **Copyright Notice**

© The ERIGrid Consortium, 2015 - 2020

Deliverable: D8.2 Revision / Status: released 3 of 94

# **Table of contents**

| E | xecutiv                         | /e Summary                                                                                                                                                                               | 7              |

|---|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1 | Intro                           | oduction                                                                                                                                                                                 | 8              |

|   | 1.1<br>1.2<br>1.3               | Purpose of the Document                                                                                                                                                                  | 8              |

| 2 | Mot                             | tivation and Background                                                                                                                                                                  | 10             |

|   | 2.1<br>2.2                      | Smart Grid ICT Assessment  Drivers for ICT Assessments Based on Co-Simulation                                                                                                            |                |

| 3 | Pro                             | posed Approach                                                                                                                                                                           | 13             |

|   | 3.1<br>3.2<br>3.3               | General Requirements for Simulation-based Smart Grid ICT Assessment  The ERIGrid Holistic Test Description for Assessments Based on Co-Simulation  Smart Grid ICT Assessment Methodology | 15             |

| 4 | Sm                              | art Grid ICT Assessment Toolchain Implementation                                                                                                                                         | 20             |

|   | 4.1<br>4.2<br>4.3<br>4.4        | Co-Simulation Environment                                                                                                                                                                | 23<br>25       |

| 5 | Pro                             | of-of-Concept Validation                                                                                                                                                                 | 32             |

|   | 5.1<br>5.2<br>5.3               | Power System Simulation with Cyclic Dependent Models (TC1)                                                                                                                               | 39             |

| 6 | Cor                             | nclusions and Outlook                                                                                                                                                                    | 58             |

| 7 | Ref                             | erences                                                                                                                                                                                  | 59             |

| 8 | Anr                             | nex                                                                                                                                                                                      | 60             |

|   | 8.1<br>8.2<br>8.3<br>8.4<br>8.5 | List of Figures                                                                                                                                                                          | 61<br>61<br>71 |

#### **Abbreviations**

API Application Programming Interface

ARP Address Resolution Protocol

CC Creative Commons

CS Co-Simulation (FMI specification)

CVC Coordinated Voltage Control

CMSA/CA Carrier-sense Multiple Access with Collision Avoidance

DE Discrete Event (MoC)

DER Distributed Energy Resources

DES Discrete Event Simulation

DoE Design of Experiments

DSL DIgSILENT Simulation Language

DT Discrete Time (MoC)

DulDomain under InvestigationFMIFunctional Mock-up Interface

FMU Functional Mock-up Unit

FRT Fault Ride Through

Ful Function under Investigation

FuT Function under Test

HIL Hardware-in-the-Loop

HLA High-Level Architecture

HTD Holistic Test Description

IO Input/output

ICT Information and Communications Technology

ISO International Standards Organization

JRA Joint Research Activity

LV Low Voltage

ME Model Exchange (FMI specification)

MoC Model of Computation

MV Medium Voltage

OLTC On-Load Tap ChangerOul Object under InvestigationPCC Point of Common Coupling

PLC Programmable Logic Controller

POI Purpose of Investigation

RMS Root Mean Square SA Sensitivity Analysis

SCADA Supervisory Control and Data Acquisition

SG Smart Grid

SuT System under Test

TC Test Case

UDP User Datagram Protocol

UML Unified Modelling Language

WP Work Package

WPP Wind Power Plant

WTG Wind Turbine Generator

#### **Executive Summary**

Work Package JRA2 has developed advanced simulation-based methods to check and validate Smart Grid scenarios, configurations and applications. The required models cover the various parts of Smart Grids, such as power system infrastructures, control algorithms, communication systems, market aspects or/and external factors like weather and people. The challenge is that the individual models of these parts are of very different nature (continuous, discrete, stochastic, etc.). From the technical perspective, this challenge has been overcome with the help of offline co-simulation, where the most suitable simulation tools for all considered domain can be coupled via the Functional Mockup Interface specification. From the methodological perspective, this challenge has been addressed by basing the work in JRA2 on ERIGrid's holistic testing procedure.

From the modelling point of view, it is important to integrate commercial and open-source modelling and simulation frameworks, both specialized on particular system aspects (e.g., power system simulator, communication system simulator) and universal (e.g., general modelling environments like MATLAB/Simulink or Modelica-based tools). The specialized tools are usually equipped with validated component libraries, sophisticated import/export capabilities and well-designed user interfaces. The universal tools, on the other hand, are good for rapid prototyping of new and uncommon components, have extensive mathematical capabilities and are well-accepted in the scientific community. It is necessary to combine the best of both worlds.

The goal of work package JRA2 was to have easy-to-deploy software packages that can cover the required simulation needs, i.e., system scalability, model heterogeneity, and simulation performance. The focus was on integrating existing diverse solutions to achieve a common and flexible simulation solution to perform holistic Smart Grid scenarios, configurations and applications. Therefore, work in JRA2 has been based on the FMI specification, an emerging industry standard that allows the coupling of simulation packages and the encapsulation of models.

From the application point of view, one of the main challenges in designing, validating, and rolling out Smart Grid innovation is the size of the energy system, which puts the simulation packages under stress. Performance and accuracy are often traded against each other, which is not a desirable situation. Work package JRA2 has approached these challenges via:

- scenario handling and system modelling via specialized software;

- modular system of systems architecture with clean boundaries for separate optimization;

- · cyber-security assessment.

This document shows how the approach outlined above enables Smart Grid information and communication technology assessments covering system stability, system scalability, component interoperability and cyber-security. The goal is to find operational limits and the sensitivity of these system properties towards specific system parameters. In combination with best practice approaches for modelling and simulation, such as design-of-experiments or Monte Carlo simulations, this approach allows to master the complexity of Smart Grid scenarios in offline simulations. In addition, first steps towards integrating these methods into online simulations (hardware-in-the-loop simulations) are shown.

#### 1 Introduction

# 1.1 Purpose of the Document

Work Package (WP) Joint Research Activity (JRA) JRA2 has implemented a co-simulation approach, using the *mosaik* platform and standardised interfacing techniques for models and simulation tools, based on the Functional Mock-up Interface (FMI) specification, as much as was technically feasible. Testing the applicability of the FMI specification and developing FMI-compliant models and tools for Smart Grid systems were thus a dominant aspect in JRA2.

Initial work conducted in JRA2 (see Deliverable D-JRA2.1) focused on the definition of concrete research challenges, based on which three distinct Test Cases (TC) have been devised. These test cases not only highlighted the relevance of the research challenges but were also used to derive technical requirements for JRA2's co-simulation approach.

This document gives an overview of the methods and tools developed in the context of work package JRA2 for the simulation-based assessment of ICT-enabled Smart Grid applications. This overview comprises a short review of the identified requirements, the proposed methodology and an outline of the implemented simulation toolchain. Furthermore, it is demonstrated how these tools and methods can be applied to assess Information and Communication Technology (ICT) enabled Smart Grid applications, by applying them to the above-mentioned test cases. These test cases are:

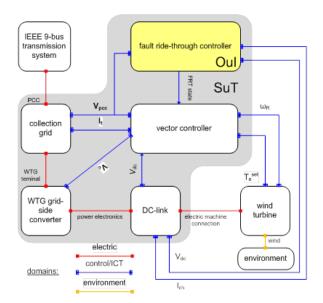

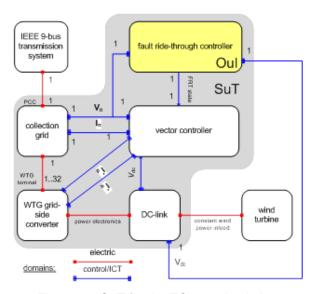

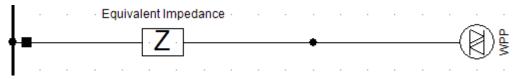

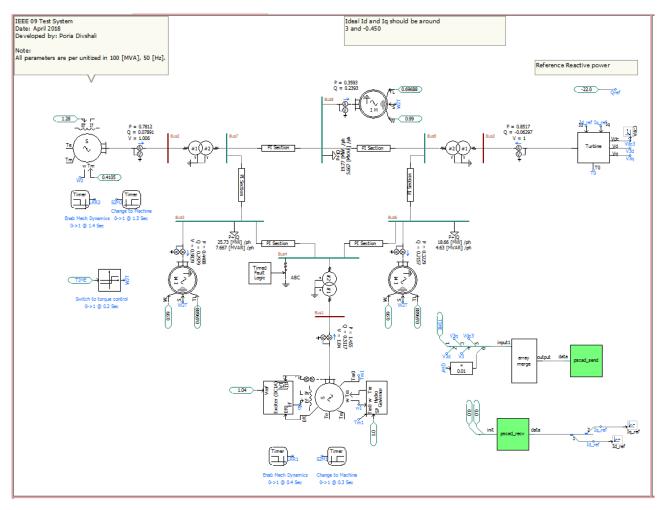

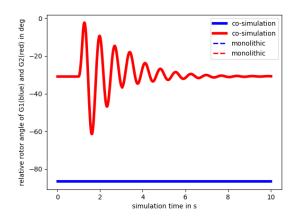

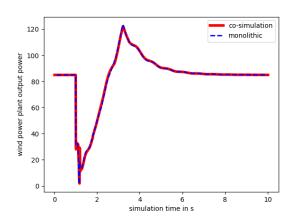

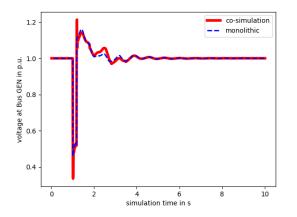

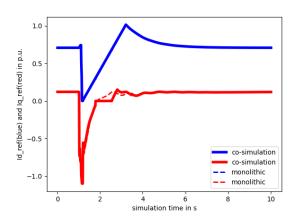

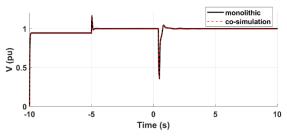

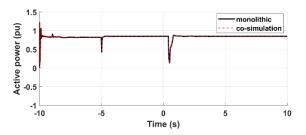

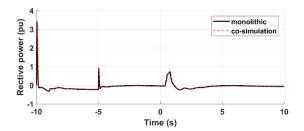

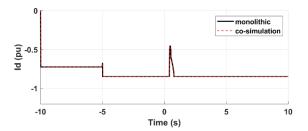

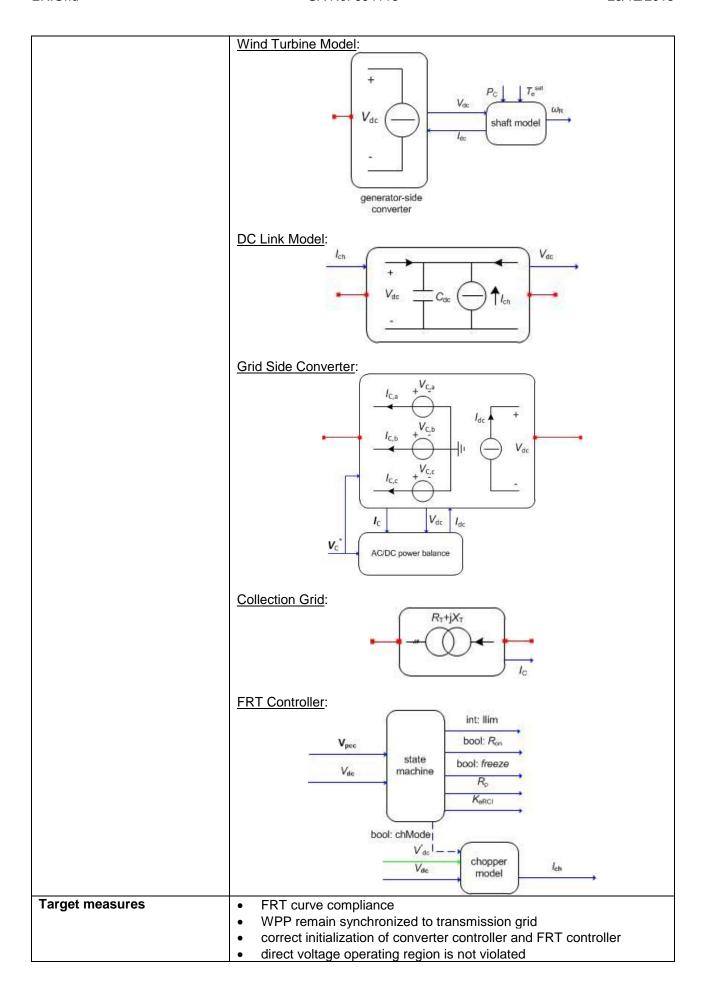

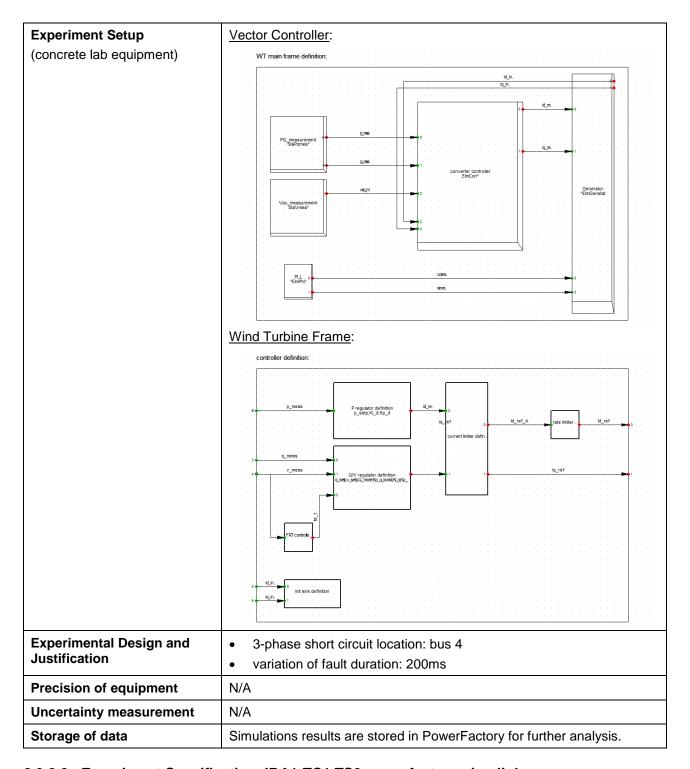

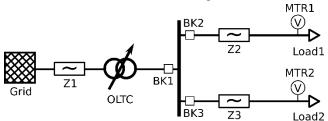

- Power system simulation with cyclic dependent models (TC1): This test case verifies the low-voltage ride through capability of an onshore wind power plant that is interconnected to a small transmission system. The Fault Ride Through (FRT) curve is enforced at the plant's coupling point, whereas the grid interface of the converter, its controls, protection, and electromechanical conversion components ensure the compliance to this curve.

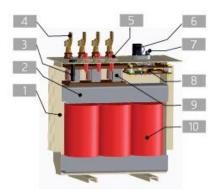

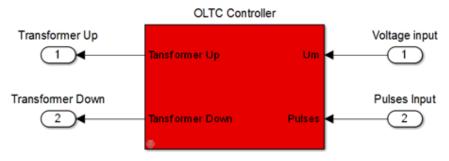

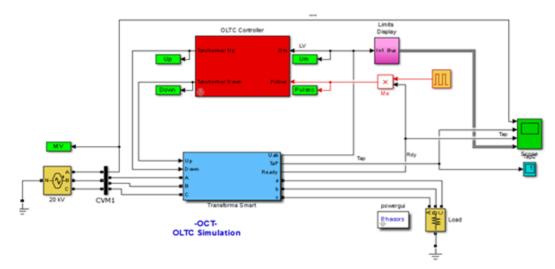

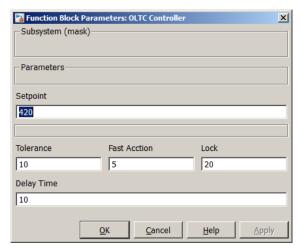

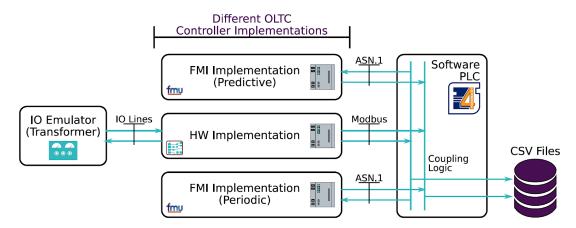

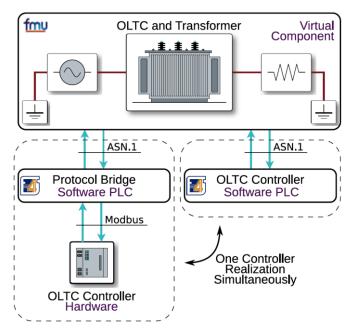

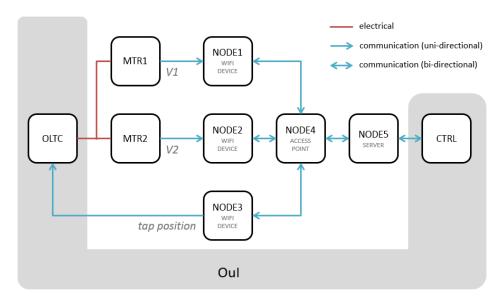

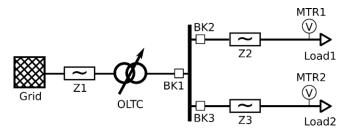

- Combined hardware and software simulation (TC2): The purpose of this test case is to validate

the operation of a controller for a transformer with On-Load Tap Changer (OLTC). Parts of this

test case are implemented in real hardware, whereas the remainder of the system is implemented as a simulation model. TC2 will demonstrate the ability to interface the models and tools

developed in JRA2 with online (hardware-in-the-loop) simulations.

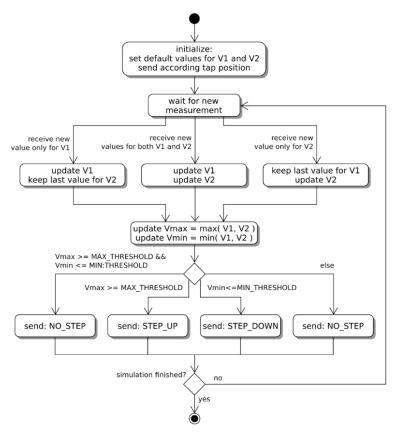

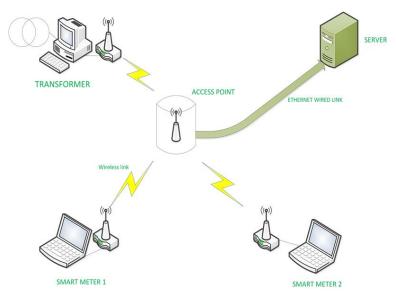

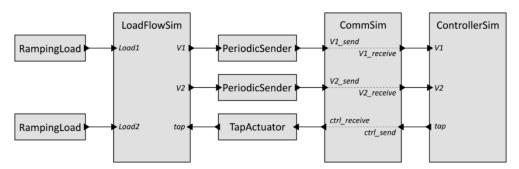

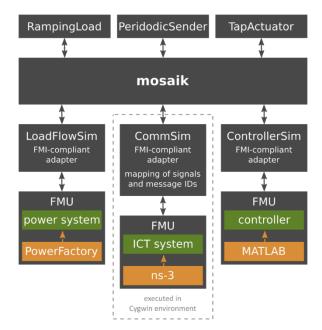

- Signal-based synchronization between simulators (TC3): This test case deals with the impact of

communication delays and controller dead times in a simple low voltage distribution grid, where

two meters send information about local voltage levels via a communication network to a remote

controller. Based on these meter readings, the controller actuates the tap position of the OLTC

transformer.

#### 1.2 Scope of the Document

The goal of WP JRA2 was to have easy-to-deploy software packages that can cover the requirements for assessing ICT-enabled Smart Grid applications: system scalability, model heterogeneity and simulation performance. The focus was on integrating existing diverse solutions instead of developing a new monolithic special-purpose tool. This deliverable explains the methods that have been developed/adapted as well as the tools that have been implemented/extended for this purpose. Furthermore, the application of these methods and tools to simple yet instructive test cases is shown, demonstrating their basic functionality.

One of the main challenges in designing and engineering Smart Grid applications is the size of the energy system. This size and complexity put simulation tools under stress, such that performance and accuracy are often traded against each other, often leading to an undesirable situation. In order to address such issues, the methods and tools described in this deliverable have been developed with the goal to enable the assessment of large-scale systems. However, the description of how these methods and tools are applied to large-scale systems is not addressed in this document, but rather in deliverable D-JRA2.3 (Smart Grid simulation environment).

Deliverable: D8.2 Revision / Status: released 8 of 94

#### 1.3 Structure of the Document

The document is structured as follows: Section 1 provides an overview of the subjects addressed in this document, including its scope and structure. Section 2 presents the motivation and background for the work presented in this document. Specifically, the definition of what a Smart Grid ICT assessment is in the context of work package JRA2 is given. Furthermore, the drivers for using co-simulation for such assessments are presented. Section 3 explains the approach for simulation-based Smart Grid ICT assessment devised in work package JRA2. First, the relation to ERIGrid's holistic testing procedure is explained. Then the technical requirements for simulation-based Smart Grid ICT assessments in the context of JRA2 are described. Based on this, the methodology adopted for JRA2 is presented. Section 4 gives an overview of the tools and methods that have been implemented/extended for the purpose of work package JRA2. This comprises a brief explanation of the co-simulation environment and the domain specific simulation tools for power system and ICT network simulation. Furthermore, the interface for integrating FMI-compliant simulation models as virtual components in hardware setups is presented. Section 5 provides a proof-of-concept validation of the methods and tools presented in Section 3 and Section 4, respectively. This is done by applying them for the assessment of ICT-enabled Smart Grid applications, namely, power system simulation with cyclic dependent models (TC1), combined hardware and software simulation (TC2) and signalbased synchronization between simulators (TC3). Section 6 presents the conclusion and outlook for the work presented in this document.

# 2 Motivation and Background

#### 2.1 Smart Grid ICT Assessment

Electric power systems as Smart Grids are inherently multi-domain systems involving the power system dynamics, communication as well as control and supervision applications at various operational time scales. Assessment such as the validation of control solutions at higher levels of maturity (e.g., pre-deployment) and system integration requires that the solution components and functionality are accurately represented. The factors influencing this solution can be of physical, ICT or algorithmic and computational aspects, accordingly the assessment methodology and simulation has to account for the domain specific representations and procedures.

The development of a Smart Grid brings new requirements and new functionality to the power systems domain and associated ICT systems. More than just increasing in "scale", this means functionality is to be provided beyond the boundaries of components and across different technology domains. Systems become multi-domain systems of increasing complexity. It can be expected that these developments require assessment approaches beyond those feasible in the state of the art. Explicit reflection of ICT and multi-domain interdependencies in simulation has to address complex interactions and behaviours internally and externally. As the system evolves in complexity and interdependency, it is conceivable to view the Smart Grid as a system-of-systems. In assessment of the Smart Grid as system-of-systems, the scope would shift from direct technical assessments to investigations on the modularity structure and resiliency of the overall energy infrastructure. Simulation-based assessment of complex and large-scale multi-domain systems does not aim at this level of abstraction, but instead focusses on explicit representation of technical elements and their assessment in a system context.

In the context of ERIGrid, Smart Grid ICT assessment describes the test-based qualification of Smart Grid ICT functions that entail continuous cyber-physical interactions (i.e., no grid planning or pure simulation but at least a closed-loop function). The assessment is aimed at anticipating and qualifying the behaviour of realistic systems where relevant phenomena arise from interactions of at least two domains. A key effort in multi-domain assessment is the separation of assessment procedures (and methodologies) from implementation, modelling and simulation techniques. Assessment procedures typically serve an assessment purpose and need and thus are problem-oriented. Relevant for Smart Grid ICT assessment are for instance:

- Control performance testing

- Interoperability testing

- Cyber-security testing

As the testing purposes used to be domain specific, the testing tools are domain specific as well, and thus the concrete realization of these procedures involved domain specific modelling and simulation tools. The domains of testing tools (both in hardware and in simulation) relevant for Smart Grid ICT assessments include:

- Physical simulations of power system and other energy forms (e.g., buildings)

- ICT/cyber systems and communication

- Control systems specification and verification tools

It is a premise in this work that the convergence of tooling for cross-domain simulation is more effective by means of tool coupling rather than convergence into monolithic simulation tools.

#### 2.2 Drivers for ICT Assessments Based on Co-Simulation

#### Overview

Simulation-based assessments of smart energy systems are typically employed to:

- Complement analytical assessments where scale, behaviour and nonlinearity of phenomena extends beyond those feasible to be addressed by analytical methods;

- Assess the concept of a control system for characterization or validation purposes, e.g., to check stability and robustness and quantify control performance with respect to alternative solutions or a baseline approach;

- Prepare a control implementation, as an intermediate step before transferring the control solution to an embedded system.

Co-simulation is practical when domain-specific models from several domains are required to reflect the relevant dynamics for a particular scenario (e.g., a power system model, controller implemented in a native language, and an emulation of communication): time is saved in the model development, and a possible model-translation error could be avoided. However, co-simulation also introduces a complication as compared to monolithic simulation approaches: the need for frequent data exchange (between simulators) and time-synchronization (across simulations) requires additional computational resources and implementation overheads, which typically slows simulations down. Obviously, there is a trade-off between co-simulation benefits and the expected slow-down and software complexity. In scaling up to larger simulation scenarios, this trade-off becomes even more prominent. In this context, the natural questions to ask are: In what cases should one resort to assessments based on co-simulation? Where are the trade-offs also acceptable when scaling up the simulation model to larger simulation scenarios? What is the alternative to co-simulation?

Avoiding co-simulation is generally achieved by the use of a native multi-domain simulation environment, such as *SystemModeler*, *MATLAB/Simulink*, and the like. Alternatively, a multi-domain simulation could be built from scratch. However, a simulator that supports multi-domain is not trivial to implement, due to the significant effort and expertise required. Also, models from different domains often target different time scales, Models of Computation (MoC) and specialized solvers. Building a simulator capable of providing appropriate environments, correct MoC, solvers and properly coordinating them internally is expensive and maybe not worth the effort.

#### Linking Models of Computation

One of the most critical points of integration is the MoC behind a model and the simulator. It is the organizing principle of a model to represent the semantics of the interactions between modules, components or phenomena. A MoC is independent from the implementation technology (i.e., sequential or parallel) and language (i.e., Matlab, Python). MoCs can be classified as in [1]: Imperative (e.g., emulators), Finite-state Machines (e.g., a set of states, rule-based control), Dataflow (e.g., for ordinary differential equations of differential algebraic equations), Discrete Event (e.g., communication, zero-crossing) and others. Discrete Event simulation can be further broken down into event scheduling, process interaction and activity scanning [2].

Energy domain simulators often employ dataflow MoC, due to the fact that they derive mostly from sets of ordinary differential equations defining the peculiarity of the state variables and the environment factors of a system (e.g. steady-state simulations, electromagnetic transients and circuit simulations, or electromechanical phenomena). However, simulators for ICT, markets or controls often use Discrete Event or Finite-state Machine semantics. The discrete models react to events that occur at a given time instant and produce other events either at the same time instant or at some future time instant in a chronological execution order. More specifically, discrete event models are discrete, dynamic and stochastic in nature and are "run", whereas continuous model are "solved". Combining discrete event-based and continuous time-driven simulation requires mixing different MoC, such as

Deliverable: D8.2 Revision / Status: released 11 of 94

Discrete Events and Dataflow in a hierarchical way. This requires an interaction semantic that resolves the ambiguities caused by differences among MoCs. Events crossing the domains need to be totally ordered and associated with time stamps. Moreover, each domain (Simulator and MoC) must also support a rudimentary notion of time. The main difficulties of the integration of such different MoCs involves the handling of simultaneous events and zero-delay feedback loops [1]. Co-simulation can help to integrate and harmonize such models with different MoC.

#### Domain Expert Support

A further argument against native multi-domain simulation is the need for models of professional quality in testing and operations assessments: domain experts are required to verify the correctness of models, which is easier to realize within domain-specific, accepted tools.

An assessment methodology based on co-simulation is necessary when system complexity requires a domain specific modelling approach. Often this complexity is viewed only as complexity of behaviour (nonlinearity, scale in number of nodes), but more important in a multi-domain setting is that each domain has a specific approach to system architecture, structure, and behaviour. For domain specific simulators, this means a domain specific approach to:

- Architectures: semantics of model lumping into sub-modules and coupling across modules

- Structures: coupling between modules basic simulation elements and data structures

- Behaviours: basic model of computation and mathematical representation of model elements

Professional domain expertise is tied to domain specific representations (e.g., networking and communications technology is modelled in network simulators; power system models including complex generator and load dynamics are modelled by power system engineers). Similarly, domain expertise is required in the semantics of a domain model in structure and architecture. For instance, cyber-security experts assessing vulnerability have to model an attack using a language that is descriptive of the cyber-domain (ICT network components, protocol layers, data streams, operating systems). For cyber-physical security assessments, the classical threat-model assessment approach has to be extended to a cyber-physical threat model and approach.

# Integration into Laboratory Environment

Finally, the development of control applications beyond the context of an embedded system is tied to more complex software, where transcoding a control description from a simulation model to implementation context can be similarly error prone, and thus at least a domain specific control description language is required (e.g., IEC61499). Testing of target control code in laboratory environment is limited due to the physical constraints of the lab environment. Here, a lab-integrated cosimulation can extend the physical environment with a virtual counterpart, enabling to explore scalability limits of the control code and to enhance the System under Test (SuT) with scale phenomena otherwise not feasible in a laboratory setup.

# Intellectual Property Issues

Another use case for upscaling co-simulations arises for grid integration of systems comprising (intellectual property-restricted) component models, such as for validation of third party systems, e.g. a "black box" control software.

# Extensibility

The above cases justify co-simulation in particular where domain-specific model complexity and expertise is the key driver. Another key driver is the simple notion that training and testing should be based on the most realistic and mature models, so that the model can be trusted. In that view, amending an existing and trusted simulation model with properties from a different domain (e.g. adding ICT communication delays) or an extended context (e.g. by extending a local electrical model with a more realistic demand behaviour) can only be realized with co-simulation.

Deliverable: D8.2 Revision / Status: released 12 of 94

# 3 Proposed Approach

# 3.1 General Requirements for Simulation-based Smart Grid ICT Assessment

The following section provides an overview of the most important general requirements for Smart Grid assessments in the context of JRA2. These requirements are general in the sense that they are not domain-specific (i.e., not directly related to the assessment of power systems, automation and control, or communication), but rather comprise generic prerequisites for simulation-based assessments. As the focus of the work package lies on approaches based on co-simulation, these requirements reflect to some extend (but not exclusively) the challenges specific to assessment approaches based on co-simulation, also taking into account that the ultimate goal of JRA2 is the assessment of large-scale systems. In addition to listing these requirements, the following section also explains how the associated challenges are handled with mosaik, the co-simulation environment chosen for work package JRA2 (see Deliverable D-JRA2.1).

# 3.1.1 System-of-Systems Architecture with Clean Boundaries for Separate Optimization

Smart Grid technologies are at their core the application of automation to the operation of electrical power systems. In the context of JRA2, the most relevant applications are those where (distributed) control systems are connected with smart sensors and actuators through ICT systems. Consequently, for the assessment of Smart Grid systems, it is of crucial importance to capture the interaction between the following three technical domains (see also Deliverable D-JRA2.1):

- Power and energy domain: This domain contains equipment for the generation, consumption and storage of electricity, as well as the technical infrastructure used to interconnect this equipment.

- Communication: This domain includes sources and sinks of information, information hubs such

as routers and switches, communication media such as cables and wireless connections, as well

as auxiliary equipment such as media converters.

- Automation and control: This domain contains control logic and algorithms.

From a conceptual point of view, this means that a Smart Grid system can be considered as a system-of-systems. Naturally, any assessment approach for Smart Grid applications should be able to capture and replicate system-of-systems properties. Within this context, an assessment approach based on co-simulation offers several advantages:

- Modularity is the most fundamental property of system-of-systems architectures. On the condition that appropriate interfaces are available that allow a proper linking of domain-specific tools, co-simulation allows the representation of (parts of) sub-systems with the most appropriate tool available. This encourages a modular representation of the SuT, with clean semantic and functional model boundaries along the real-world domain borders.

- Hierarchical composition is a prominent feature of many system-of-systems architectures, typically in the form of system layers with distinct functionality (e.g., an ICT layer "on top" of the physical power system). By following a modular approach, the combination of specialized tools in a co-simulation can also help to address typical issues of hierarchical modelling. For instance, co-simulation can help with mixing models of computation (e.g., continuous time-based and discrete event-driven simulations) or multi-rate simulations by encapsulating the individual models, each with its own dedicated solver.

The potential of assessment approaches based on co-simulation to capture systems-of-systems in terms of modularity and hierarchy, enables experts to focus on the assessment and optimization of their specific domain. At the same time, it provides them with the possibility to assess the effects of changes in the setup of their specific sub-system on the overall system, enabling a holistic assessment.

Deliverable: D8.2 Revision / Status: released 13 of 94

A substantial part of the work done in work package JRA2 focused on the subject of modularity and hierarchical modelling, specifically the development of appropriate simulation interfaces for the selected domain-specific tools (see Sections 4.2 and 4.3) as well as mosaik's capability of linking tools from different domains and with diverse models of computation (see Section 4.1). In addition, the domain-specific tools chosen for work package JRA2 (see deliverable D-JRA2.1) all use object-oriented component models, further reinforcing a modular and hierarchical modelling approach.

## 3.1.2 Scenario Handling and System Handling

The use of co-simulation for validation in holistic Smart Grid systems requires means of flexible scenario handling in complex setups. Such a feature allows for easy component replacement and system scaling, which make up the main advantages simulation-based validation has over lab-based validation.

In the co-simulation framework mosaik, flexible scenario handling is achieved via a dedicated scripting interface. This interface, called *Scenario Application Programming Interface* (Scenario-API), provides simple commands for the initialization of simulators, the instantiation and parameterization of model objects, and the connection of models. The fact that scripting is required leads to the need of users to possess some programming skills, but the slight loss in usability is easily outweighed by the gain in flexibility. If the employed simulators support instantiation, hundreds to thousands of model entities can be created with a single command allowing for fast upscaling of any co-simulation setup. Similarly, large sets of model entities can be easily connected to each other. Since the Scenario-API is based on the general-purpose programming language Python, structures for iterations and conditional control may be used for filtering of model entities and rule-based connections. Similarly, iterative structures may be used to initialize large sets of simulators.

Flexible scenario and system handling supports several of the system assessment efforts analysed in JRA2. On the one hand, higher numbers of modelled entities can easily be realized in a co-simulation setup, as mentioned above. On the other hand, integration of upscaled versions of single components is also possible. An example for this may be a power grid or communication system model with more nodes. Since the work in JRA2 is based on generally accepted and popular modelling tools as well as standardized interfaces (via FMI), it is relatively easy to replace, e.g. a 100-node model with a 1000-node model in a holistic co-simulation scenario. Finally, script-based scenario handling allows for easy creation of parameter studies with several parallel or sequential simulation processes exploring the parameter space of the scenario. This can either be used for gradual upscaling of a system simulation or for more general assessment approaches like sensitivity analysis or uncertainty quantification in form of a Monte Carlo study.

#### 3.1.3 Distributed and Parallel Simulation

The mosaik co-simulation environment supports distributed simulation via the possibility to start simulation components in remote processes or connect to already running processes. Apart from enabling the distribution of a co-simulation across several hardware nodes, this approach allows to couple simulators with different run-time requirements executing on the same hardware node. For instance, the coupling of 32-bit and 64-bit applications on the same hardware node is possible, or Windows and Linux applications (using Cygwin, see for example Section 5.3). A distribution of the scheduling module itself, however, is not possible - unlike it is the case for co-simulation tools based on the High-Level Architecture (HLA).

It the context of parallel simulation, it is important to note that mosaik provides conservative scheduling of its simulator processes. This means that simulation components will stop their execution after a simulation step until new input data is provided. The alternative to this would be progressive scheduling that has components simulate in advance and force them to roll back in case of changing input data. Mosaik employs conservative over progressive scheduling since several simulators do

Deliverable: D8.2 Revision / Status: released 14 of 94

not support rollbacks and may thus only be employed in a conservative setting. Consequently, mosaik's potential to parallelize a single simulation scenario is limited. After all, conservatively scheduled simulators cannot be executed in parallel if one of them is expecting input data from the other. Instead, parallel simulation is only possible for those components that do not possess any direct or indirect data dependencies towards each other.

# 3.2 The ERIGrid Holistic Test Description for Assessments Based on Co-Simulation

The specification and execution of tests or experiments is central to any assessment approach. The holistic testing procedure proposed in ERIGrid aims to unify the approach to testing across different research infrastructures, different testbed types and to facilitate multi-domain testing. In practice, holistic testing here means to make the most of available infrastructure by providing a common frame for coupled simulations.

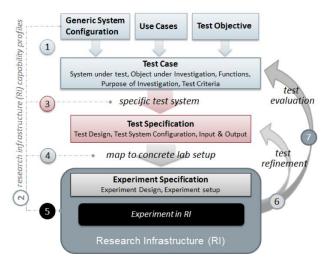

Figure 1: Overview of ERIGrid's holistic testing procedure

A central element of the ERIGrid approach is the *Holistic Test Description* (HTD) method: it defines a number of specification elements for any test, to be identified independently of the particular assessment methodology. The specification elements comprise three main levels of specification:

- Test Case: a concise formulation of the overall test objectives and purpose of investigation, specifying the object under investigation, separating system structure from functions (system under test vs. functions) and identifying test criteria.

- *Test Specification*: a detailed description of the test system, control parameters and test signals to address a specific subset of the test criteria.

- Experiment Specification: how is the test specification realized in a given testbed? What compromise had to be made in the representation with respect to the test specification?

The method is supported by structured templates to facilitate the harmonized recording of test descriptions. Method detail is defined in detail in [3], and the description templates are provided under a Creative Commons (CC) license.

It is relevant here to emphasize how the HTD approach applies to co-simulation based Smart Grid ICT-assessment. First of all, the approach is *inherently multi-domain*, where the SuT outlines the generic multi-domain structure and interfaces relevant to a test case. Furthermore, the approach facilitates the separation of simulator embedding from specification of the test system structure (i.e., the model topology, also across simulators). To that end, the test specification is formulated independently of test beds but focusses on system parameters, including exchange variables. The description method is thus *independent of simulator embedding even in a co-simulation context* and

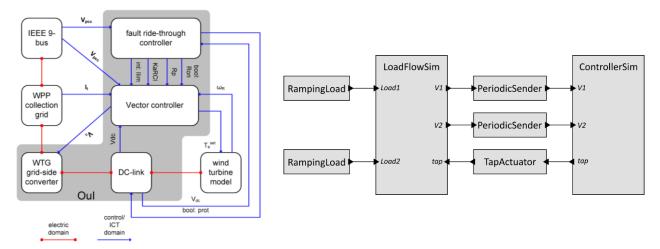

allows the detailing of test purposes before a simulation platform is selected. Figure 2 illustrates two such test system definitions. Third, the *framing of the assessment approach is generic* in a test case; it is not specific to any particular assessment method, so that it can be applied to any of the cyber-physical energy system and Smart Grid ICT-assessments investigated (e.g. controller validation, upscaling, cyber-security).

Figure 2: Example representations of test systems: components, terminals (with directionality) and domains are clearly distinguished

Two critical mapping steps are framed by the HTD: the step from generic test case to detailed test specification(s), and the step from test specification to realization in a specific set of simulation environments in an experiment setup. The former is addressed by a *Qualification Strategy*, which accounts for the division of tests, for example to first characterize the simulators before testing. In general, multiple individual test purposes are addressed by a single test case. Similarly, the implementation of test systems in a test-bed is well expressed by an illustration of simulator-embedded models, as illustrated for example in Figure 3.

In that, the HTD aids the specification of tests or experiments also for co-simulation testbeds:

- The formulation of test objectives in isolation from use case or simulation environments separates test purpose from test object and tooling; this aids technology-agnostic formulation of assessment methods.

- Co-simulation experiments, by definition, contain multiple simulation models; for the testing context, it remains essential to establish a shared topology of the experiment across domains; the notions of "test system" vs. "experiment setup" offer a natural framework for this distinction (compare Figure 2 to Figure 3).

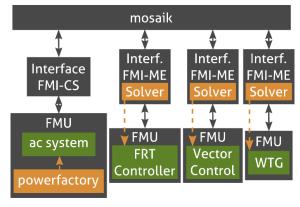

Figure 3: Representation of experiment setup (simulators representing testbed level)

# 3.3 Smart Grid ICT Assessment Methodology

The following section provides an overview of the methodical approaches that have been applied for the assessment of ICT-enabled Smart Grid applications using the toolchain developed in JRA2. The investigated methodical concepts represent general best practice approaches for simulation-based assessments (and beyond) and are themselves not limited to assessments of Smart Grid applications. However, by applying these methods to the JRA2 toolchain, a large spectrum of problems related to the assessment of ICT-enabled Smart Grid application can be addressed. The investigated methodical approaches are not exclusive, i.e., there are potentially others that can be successfully applied to this toolchain. However, during the course of the project, these approaches have been proven valuable for achieving the set goals. As such, they together form work package JRA2's methodology for Smart Grid ICT assessments.

#### 3.3.1 Monte Carlo Simulations

Monte Carlo simulations are a stochastic approach that is based on a (very) large number of similar random experiments. In the context of work package JRA2, randomness comes from processes whose properties can only be characterized statistically. For instance, ICT systems are typically modelled in discrete event simulations, with events corresponding to arrival of messages at various points in the system. As packages entering the system as well as processing delays at each node are typically modelled by random sampling, each model run will in general have different outcomes. This requires gathering statistics on outcomes from multiple model runs, as any single model run cannot represent the full range of possible outcomes. However, exploring all combinations in the case of multiple variable parameters may become computationally expensive. On the other hand, propagation of correlated variables may overestimate the output measure and statistical distributions.

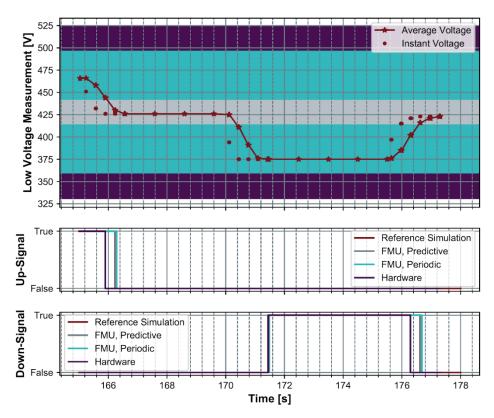

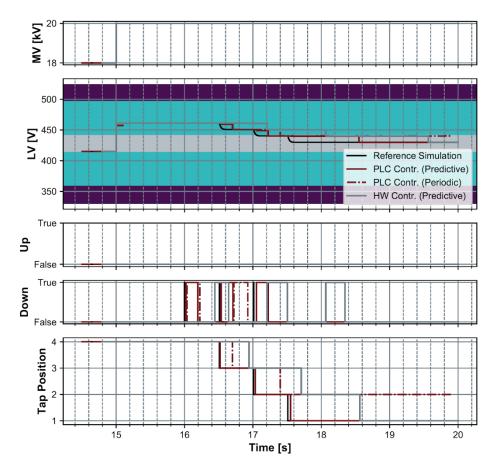

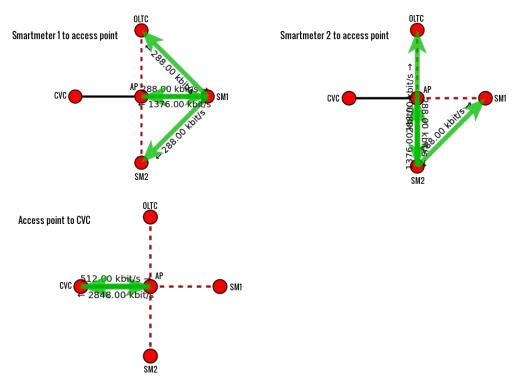

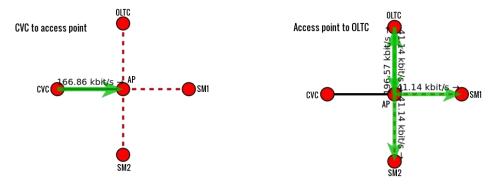

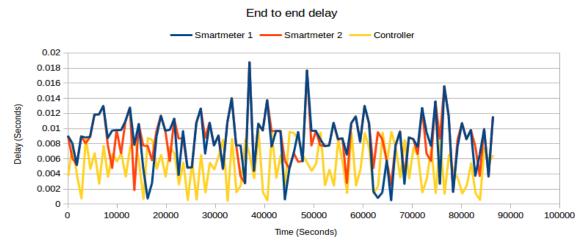

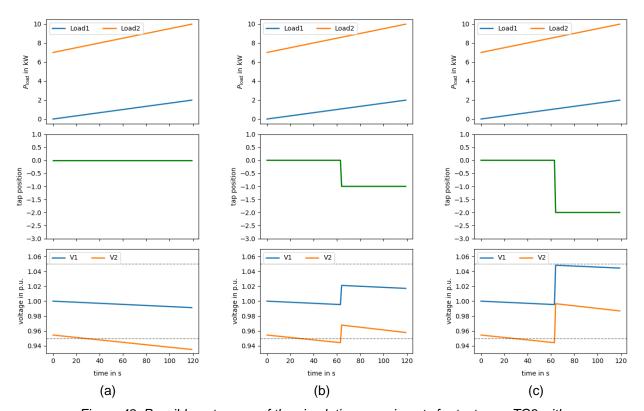

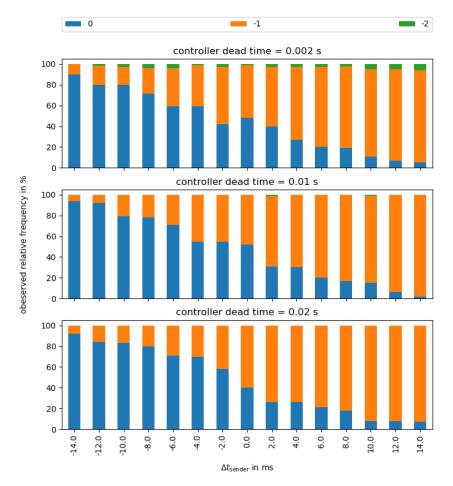

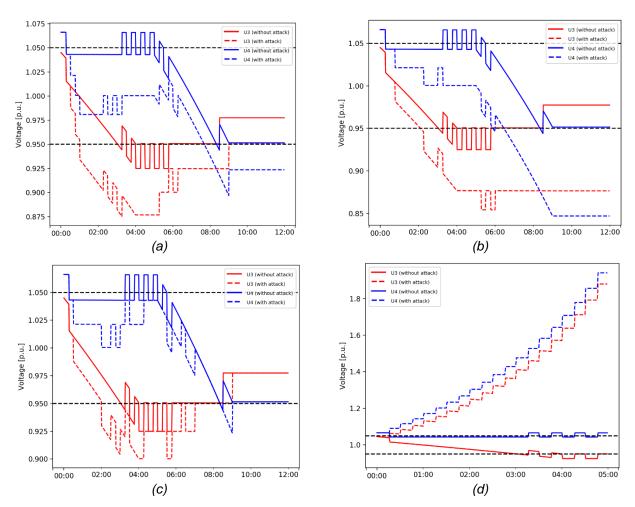

JRA2 deals with controllers coupled through simulated ICT systems, making the use of Monte Carlo simulations necessary to quantify the impact of (randomized) ICT delays. This is demonstrated in test case TC3, where the effects of network delays and controller dead times on an OLTC transformer are analysed. In the example, two voltage meters periodically send their readings to a server, which calculates a new tap position for the OLTC transformer whenever a new measurement is available. The tap positions are then sent to the OLTC transformer where they are actuated. In this specific test case, it can be shown that the delays and dead times can lead to random, unexpected outcomes (see Section 5.3).

#### 3.3.2 Sensitivity-aware Parameter Variation and Design of Experiments

Smart Grid ICT systems are typically complex systems-of-systems with each sub-system possessing several parameters that determine its behaviour. The overall ICT system thus possesses a highly multi-dimensional *design space* which each parameter of each subsystem posing as one dimension. One point in this space stands for a particular system parameterization and a common task in ICT research is to identify the sets of parameters that lead to a system behaviour that is in some sense optimal. Obviously, in a high-dimensional and possibly continuous design space not all possible parameter value combinations can be tested. Instead, *Design of Experiments* (DoE) methods can be employed to obtain the maximal amount of information from a finite number of experiments or simulations.

While classical DoE is typically geared towards analysis of systems with intrinsic statistical fluctuations, the work in JRA2 is mostly focused on so-called "modern" DoE that is typically associated with software simulation experiments. Software models have the analytical benefit that they do not contain fluctuations (unless explicitly introduced into the model) so that one and the same set of parameters always leads to the same outcome. On the other hand, simulation models typically possess a larger number of tuneable parameters (factors) than hardware systems since they are used in earlier stages of the design process. Accordingly, modern DoE methods are often used for screening of the analysed system to gain information about its behaviour, which may be used to refine following experiments. With *space-filling* sampling strategies, modern DoE makes sure that large numbers of

Deliverable: D8.2 Revision / Status: released 17 of 94

simulation runs are efficiently used to account for nonlinear system behaviour. Similarly, high-dimensional design spaces can be efficiently filled. This way, a *Sensitivity Analysis* (SA) can be conducted that allows users to identify the most influential factors and value ranges for a given system. Furthermore, DoE techniques to restrain the parameter variation zone can be particularly helpful to reduce the number of Monte Carlo simulations to be performed and avoid unwanted design choice effects.

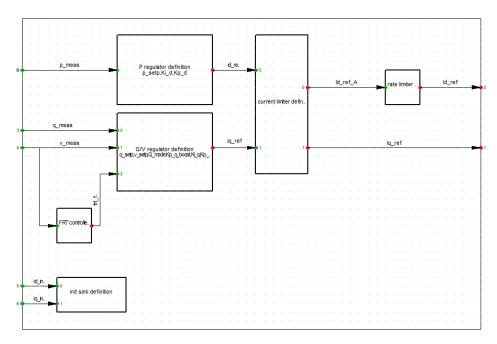

In JRA2, an exemplary screening experiment has been conducted in the context of test case TC1 (see Section 5.1). The analysed system contains a power grid, a wind turbine generator as well as its converter, and a control system influencing the converter behaviour. The factors analysed in the screening have been proportional control gain, the current limiting strategy followed by the control system, and the active power recovery rates. As the system response to value changes, its voltage and frequency behaviour have been analysed. As a result of the screening, the current limiting strategy has been identified as a negligible factor while control gain and recovery rates should be considered as important factors in following experiments. The importance of using DoE methods for such SA endeavours stems from the fact that factor interactions should be considered for SA instead of just single-factor effects. Furthermore, modern DoE also helps to consider nonlinear effects in a system, as mentioned before. This is typically associated with the term *global* SA.

#### 3.3.3 Cyber-Security Assessment

Compared with legacy power systems, the ICT-enabled Smart Grid is envisioned to fully integrate high-speed, two-way communication technologies into a large number of devices. This will enable the creation of a dynamic and interactive infrastructure with new capabilities, such as energy management by means of active voltage control in medium and low voltage distribution grids. Therefore, the Smart Grid is a progressive evolution of existing power grids, whereby increased levels of automation and ICT technology will ultimately result in a large-scale system supporting complex interactions between various actors in the electricity sector (energy producers, consumers, distributors, etc.). One of the biggest challenges for such systems is to ensure that automation systems and supporting ICT networks are adequately designed and secure.

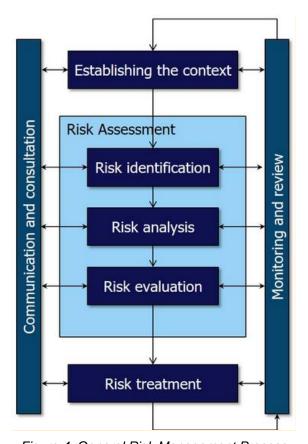

In 2009, the International Standards Organization (ISO) published the international standard for risk management ISO 31000:2009 [4] which is based on national approaches from Australia and New Zealand (AS/NZS 4360:2004, see [5]) as well as Austria (ONR 49000:2004, see [6]). This standard has evolved to a widely accepted standard, which – due to its generic approach – can be ubiquitously applied to basically every kind of organization, regardless of its type, perspective or size. The generic steps of every risk management process are shown in Figure 4.

This generic process has been adopted and tailored to Smart Grid applications within the research project SPARKS [7]. The project SPARKS suggested several good practices and tools for conducting the cyber-security risk assessment on Smart Grid systems. One of them is also consequence informed risk assessment, which can also be applied for cyber-security assessment in the context of work package JRA2. Specifically, the following steps of the risk management process along with the best practices for their application in the context of Smart Grids have been derived from the SPARKS project:

- Establishing the context: This step involves the definition of the scope of the risk assessment to

be carried out and the overall goals of the stakeholders involved. To support the context establishment and provide guidance specific for Smart Grid assessments when necessary (including

aspects such as the business goals and relevant actors) the underlying architecture is recommended to be modelled using the Smart Grid Architecture Model (SGAM) framework according

to the SPARKS project.

- Risk Identification: The purpose of this step is to determine what could happen to cause a potential loss and further how, where and why the loss might happen. To answer these questions SPARKS recommends usage of threat libraries and structural graph-oriented techniques, such as attack graphs.

Deliverable: D8.2 Revision / Status: released 18 of 94

- Risk Analysis: This step addresses the assessment of impact and likelihood, and finally the determination of a risk level, which is based on the impact and likelihood values. On the one hand, for addressing likelihood, SPARKS recommends the usage of quantitative measures (low, medium, high). On the other hand, impact should be assessed from multiple perspectives (safety, financial, reputational, system impact, etc.). For deriving the system-level impact, it is recommended to use simulation-based approaches for the systematic identification of consequences in Smart Grid systems. These consequences also need to be placed in relation to threats identified in the previous step.

- Risk Evaluation: After completing a satisfactory risk assessment, risk treatment follows. Initially, security requirements and recommendations for the specific use case are derived. These can be viewed as high-level technical and organizational recommendations that can be realized using a number of different, more specific, controls. The SPARKS project recommends deriving specific security control based on the NISTIR 7628 [8] and ENISA guidelines.

- Risk Treatment: This step is concerned with the choice of security control to implement, such as

firewalls and intrusion detection systems or authentication mechanisms, which will be based on

an organization's risk tolerance and the budget allocated to cyber-security matters.

Figure 4: General Risk Management Process

In conclusion, designing security for (potentially large) Smart Grid systems is a complex process, which requires that cyber-security experts can assess an impact of ICT systems on physical infrastructure. One way to assist experts in performing such risk assessments are simulation-based holistic approaches, like the one developed in work package JRA2, as the results of the simulations enable better risk perception and decisions during the risk treatment phase.

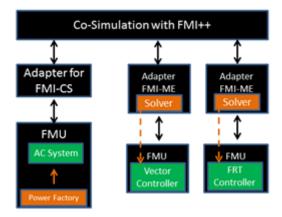

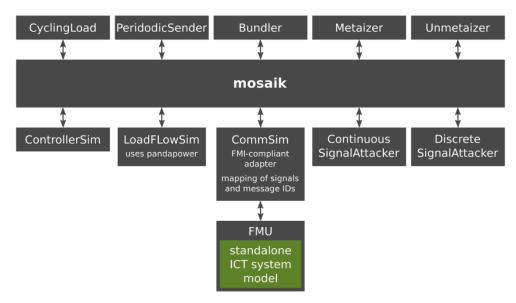

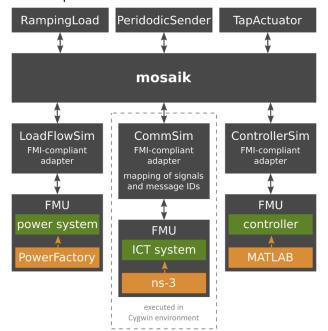

# 4 Smart Grid ICT Assessment Toolchain Implementation

The following section gives an overview of the toolchain implemented in work package JRA2. The goal of work package JRA2 was to have easy-to-deploy software packages that are capable of covering the requirements for assessing ICT-enabled Smart Grid applications. At the same time, the goal was also *not* to implement yet another tool that just covers one view of the system, but to integrate existing solutions within a co-simulation approach. Therefore, work in JRA2 has been based on the FMI specification, an emerging industry standard that touches that allows for coupling simulation packages and encapsulating models. Therefore, the development work in JRA2 focused on two tasks:

- FMI-compliant developments: Several of the tools selected for the use in JRA2 do not provide or

provide only limited support for FMI by themselves. Hence, FMI-compliant co-simulation interfaces have been developed, as well as tools and user-friendly scripts to generate FMI-compliant

co-simulation components, so called Functional Mock-up Units (FMU).

- mosaik developments: The co-simulation framework mosaik also needed to be extended for the purpose of JRA2. This included a user-friendly way of handling FMUs (instantiation, data exchange, execution), the handling of cyclic dependencies between simulators and signal-based simulations.

At the time of writing, several of these developments are prototype implementations that will need to be improved and extended in the future. However, together they provide a proof-of-concept that FMI-based co-simulation is well suited for the assessment of ICT-enabled Smart Grid applications, able to address the research challenges defined for work package JRA2 (see Deliverable D-JRA2.1).

#### 4.1 Co-Simulation Environment

The mosaik framework is an easy-to-deploy software package that facilitates the integration of new simulators as well as the creation of co-simulation experiments. This is achieved via a lightweight software core based purely on Python, a special *Component-API* for simulator integration, and a *Scenario-API* for flexible simulator coupling. Since the mosaik framework is still under active development, new features have been introduced based on requirements defined for work package JRA2 (see deliverable D-JRA2.1).

## 4.1.1 FMI Support

The FMI specification intentionally provides only the most essential and fundamental functionality in the form of a C interface. On the one hand, this increases flexibility in use and portability to virtually any platform. On the other hand, such a low-level approach implies several prerequisites a simulation tool has to fulfil in order to be able to utilize such an FMI component.

To this end, the *FMI++ Python Interface* [9] has been developed, a Python package wrapping the *FMI++ Library* [10]. The FMI++ Library bridges the gap between the basic functionality provided by the FMI specification and the typical requirements of simulation tools. It provides high-level functionality that eases the handling and manipulation of FMUs, such as numerical integration, advanced event-handling or state predictions. This allows FMUs to be integrated more easily, e.g., into fixed time step or discrete event simulations.

For the purpose of work package JRA2, the FMI++ Python Interface and the mosaik framework have been successfully combined for the co-simulation of FMUs. Several examples of importing FMUs have been implemented using the FMI++ Python Interface to interact with the FMU and mosaik's high-level component API to integrate it into the co-simulation. For this, especially the functionality for conveniently handling FMUs was extensively used, such as extracting the FMU, parsing its model description or the ability to refer to input/output variables by name (rather than the numerical value reference associated to each variable).

Deliverable: D8.2 Revision / Status: released 20 of 94

Within JRA2, the main effort was to make the installation of the FMI++ Python Interface more user-friendly. Previously, users had to compile it from source code, which involved a rather complicated toolchain that only users with experience in software development were able to use. Therefore, easy-to-install binary packages (Python wheels) for Windows and source distribution packages for Linux have been made publicly available on the official Python Package Index [9].

# 4.1.2 Handling of Cyclic Dependencies

#### Overview

The term "cyclic dependencies" here refers to a co-simulation setup in which two (or more) simulators require data from each other to advance their state in time. These data dependencies may lead to deadlocks with all simulators waiting for data from each other, halting the whole simulation process. Therefore, proper handling of cyclic dependencies is one of the most crucial tasks in co-simulation.

In the following, the proposed extension for enabling co-simulation of models with cyclic dependencies in the mosaik framework is presented. For concrete examples highlighting this extension, please refer to Sections 5.1 and 5.3.

# Extension of mosaik

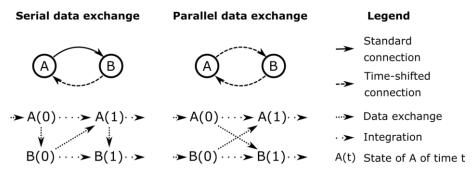

Most basic considerations about the topic stem from co-simulation research for continuous-time white box models. In this context, the simulation scheduling differentiates between micro steps for integration steps of the simulators and macro steps for the data exchange between simulators. Different procedures have been proposed for the scheduling of macro steps and iterative calculation of stable system states. Fundamentally, researchers differentiate between serial data exchange schemes (also called *Gauss-Seidel* type procedure) and parallel schemes (also called *Jacobi* type procedure). In Smart Grid co-simulation, simulators are typically treated as black box systems so that iterative refinement of the same time step is usually not considered. Nevertheless, the concepts of serial and parallel data exchange schemes also exist in black box Smart Grid co-simulation.

Additional aspects that are more pronounced in Smart Grid co-simulation than in classical white box systems are the ideas of *usability* and *flexibility*. Usability means that co-simulation solutions are expected to be applicable by different types of domain experts that are not necessarily simulation experts. Flexibility means that the solutions are expected to work in a variety of different application cases without requiring major changes to the employed tools.

The co-simulation framework mosaik has been developed with a strong focus on flexibility. Accordingly, the scheduling algorithm of mosaik is designed in a way to allow integration of any number of simulators. Furthermore, all integrated simulators may display different macro step sizes and even vary their step size over time. In order to guarantee the absence of deadlocks for any given setup, the handling of cyclic dependencies in mosaik has so far had some limiting characteristics. In particular, using mosaik's intuitive connection capabilities to establish cyclic data exchange between two or more simulators has been prohibited. Instead, users had to extend the simulator interfaces to realize cyclic data exchange, which obviously decreases the usability of mosaik for researchers with little programming experience. Furthermore, the described solution in mosaik only supports serial data exchange schemes.

Within the scope of the ERIGrid project, the capabilities of mosaik have been extended to allow for higher usability in the handling of cyclic dependencies. The basic idea of the extension is the separation of data exchange into two stages: Simulators may receive data either *before* they are called to calculate a time step, or *after* they have calculated so that they store the data for the next time they are called. With this separation, priorities between simulators can be established so that deadlocks are avoided. Figure 5 illustrates different data exchange options between two simulators A and B. Connections for data exchange before calculations are called *standard connections* since they are part of the typical functionality of mosaik. The newly added connection type is called *time-shifted connection* since they provide data to simulators that already have been called for calculation.

Deliverable: D8.2 Revision / Status: released 21 of 94

Figure 5: Data exchange schemes possible in mosaik

As Figure 5 shows, standard connections in mosaik provide data to a simulator for its calculation of the current time step while time-shifted connections provide data for the next time step to be calculated. Furthermore, mosaik provides the option to set default input data for the first calculation of a simulator that is addressed by time-shifted connections. This way, parallel data exchange schemes may also be realized if initial input data can be assigned to each simulator.

Overall, the extension of mosaik improves its usability and provides it with the most common options for handling cyclic dependencies in Smart Grid black box co-simulation.

# 4.1.3 Signal-based Synchronization

#### Overview

One of the research challenges formulated for JRA2 was the detailed simulation of ICT-based communication in Smart Grid systems. This involved two challenges:

- Discrete Event (DE) simulation: The mosaik framework has been primarily designed for Discrete

Time (DT) simulation, where the time step size between each call to a simulator is a fixed, constant

value (even though the step size may be different for different simulators). Even though DT simulations are useful for the assessment of a large variety of Smart Grid application, they struggle

to capture the details of discrete event-driven models (such as typical models of communication

systems). Similarly, the API for FMUs for Co-Simulation is not primarily intended to be used in DE

simulations (for instance, it lacks the functionality to predict internal simulation events).

- Signals: The co-simulation of "physical" systems mostly involves the exchange of information that corresponds directly to physical properties (voltages levels, temperatures, etc.). This is typically done and the APIs of mosaik and the FMI specification are no exception here by directly sending the values of the associated model variables from one simulator to another. However, communication systems typically do not just exchange values, instead information is transmitted with the help of protocols, which involve meta-data and data formats.

In the following, the proposed extensions for enabling signal-based simulations to the mosaik framework are presented. A discussion of the prototype for an FMU for Co-Simulation (CS) for signal-based simulations can be found in Section 4.3.1. For concrete examples showcasing these extensions please refer to Section 5.3.

## Extension of the mosaik Framework

The intention for work package JRA2 was to extend mosaik in a way that it supports DE simulations. Unfortunately, a closer look showed that this would require more substantial modifications of mosaik's core than previously assumed. Work on the subject started nevertheless, but it became clear that the final result would not be available in time for the purpose of JRA2. It was therefore decided to use a workaround that is functional, even though its drawbacks with respect to computational performance and time resolution compared to actual DE simulations are obvious.

In the following, the approach chosen for signal-based simulations in JRA2 is outlined. Its big advantage is that it does not require changes to the mosaik core, but only in the simulators APIs:

- Logical time: The internal representation of time in mosaik is an integer value. In one approach

examined here, the internal mosaik time is dynamically scaled such that the necessary resolution

is achieved (e.g., one tick of internal mosaik time may correspond to 5 milliseconds at one time,

and 3 seconds at another time). The simulators have to be implemented such that they can

translate mosaik's logical time to simulation time, which can be accomplished quite easily when

calling an FMU's step function.

- Absent values: For signal-based simulations it is important to define the notion of a signal being absent. This means for instance that the output of a simulator only provides values whenever a signal is being sent. mosaik's implementation in Python allows to set outputs to the built-in constant None, which indicates the absence of a value. Simulators have to incorporate this notion accordingly, and only set input values for FMUs whenever a signal and hence an associated value is present or provide an output value whenever they send a signal.

- Message IDs: In contrast to mosaik, communication network simulators provide dedicated functionality to handle the details of data transmission protocols. Hence, it was decided to encapsulate these details in the simulators themselves, by not giving actual values as inputs to communication simulators. Rather, actual values being sent are associated with unique, integer-based message IDs, which are given to the communication simulator instead (with a special value representing an absent signal). The simulator then processes internally a dummy message associated to this message ID. Once the message is received, the corresponding message ID is given as output, which can then be retranslated to the initial value.

Taken together, these adaptations allow simulating discrete-event systems, albeit with a significant performance loss.

#### 4.2 Power System Simulation

For the power system domain, two simulation tools – PowerFactory and PSCAD – have been identified that fulfil the general and domain-specific selection criteria (see deliverable D-JRA2.1 for details). Among other criteria, FMI compliance or at least the existence of a simulation API (or equivalent mechanism) was a determining factor. Since neither of the tools (nor any other comparable power system simulator) has an FMI-compliant interface, the work in JRA2 regarding to power system simulation focused on the development of such interfaces. The following section gives an overview of the accomplished work.

## 4.2.1 PowerFactory

# Overview

DIgSILENT PowerFactory (DIgital SImuLation and Electrical NeTwork calculation program Power-Factory) [11] is a commercial tool for power system design and analyses. It is an engineering tool targeting primarily professional users, enabling the analysis of industrial, utility, and commercial electrical power systems. It has been designed as an advanced integrated and interactive software package dedicated to electrical power system and control analysis in order to achieve the main objectives of planning and operation optimization.

PowerFactory does not officially provide an FMI-compliant co-simulation interface. However, it provides an API that enables basic interactions with simulation models at run-time [12], e.g., setting/retrieving variable values and calculating power flows. A stand-alone tool for creating FMUs from PowerFactory models based on this API was already available before the project start. However, this implementation did only support consecutive power flow calculations. Therefore, to comply with the domain-specific criteria of JRA2, the interface has been extended to support time-domain simulations (referred to as "RMS simulations" in PowerFactory).

Deliverable: D8.2 Revision / Status: released 23 of 94

PowerFactory provides the possibility to issue so-called events during RMS simulations that can change the system state at a specified point in simulation time. This mechanism has been utilized to enable a dynamic interaction with simulation models at run-time. This mechanism is suited for co-simulation and has been integrated into the FMU exporter tool mentioned above.

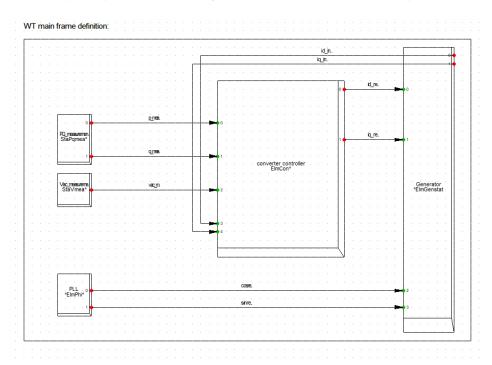

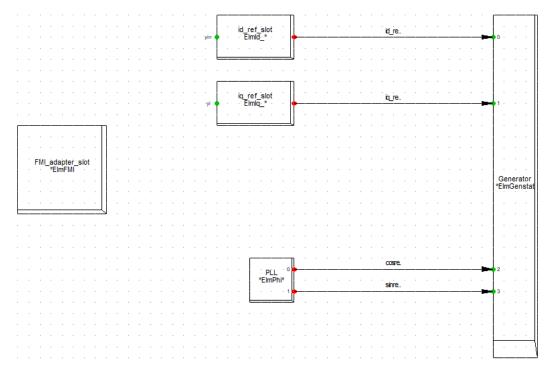

#### Creating Models for RMS Simulation

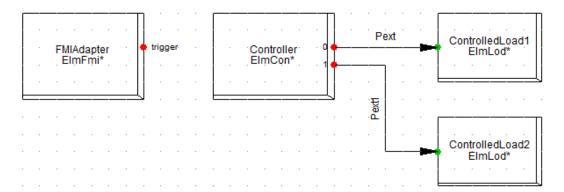

This approach relies on PowerFactory's so-called *DIgSILENT Simulation Language* (DSL), a domain-specific language used to program models for electrical controllers and other components used in electric power systems. PowerFactory provides the functionality to associate objects with user-defined DSL models via a composite model (type *ElmComp*). By sending a so-called *parameter event* (type *EvtParam*) to such a DSL model, the model's input parameters can be changed. This change of input parameters can be easily propagated to the parameters of any object by connecting the DSL model with the corresponding object in a *composite model*.

For sending events to a composite model, a dedicated compiled DSL block called *FMIAdapter* is provided. To use this DSL block it must be included into a composite model (see example in Figure 6). The block does not have to be connected directly to any other block, instead it sends events to other blocks (in the example to the block called *Controller*) to change their input parameters. To which blocks these events are sent is defined in the FMU export configuration.

Figure 6: Example of a composite frame including DSL model FMIAdapter

# Exporting Models for RMS Simulation

To create an FMU from a PowerFactory model that is intended for RMS simulation, a dedicated Python script has to be executed. When calling this script, the user has to provide relevant information such as the FMU model identifier (i.e., the FMU's name), the PowerFactory model or lists of input and output variable names. For inputs intended to be sent as event via DSL block FMIAdapter, a dedicated naming convention has been devised that specifies the name of the receiving block and its input parameter name.

#### **4.2.2 PSCAD**

#### Overview

PSCAD is a commercial general-purpose time domain simulation tool for studying transient behaviour of electrical networks. Its strengths, in addition to its computational performance and advanced user interface, are in the modelling modularity and ability to model the components using standard library components or user-built model components of desired level of detail. As addressed in deliverable D-JRA2.1, the most recent versions of PSCAD provide a built-in interface for MATLAB/Simulink. However, this interface proved to perform poorly in TC1 scenarios, as data exchange was remarkably slow.

PSCAD provides a so-called *Automation API*, a Python interface that can be used to interact with the software, e.g., for opening and loading projects, setting model parameters and running simulations. Despite providing a wide range of functions, this API cannot access the simulation model's data signals that are needed for co-simulation. However, user components in PSCAD are programmable with Fortran, which in turn allows cross-compiling C/C++ code and thus enables the development of a co-simulation interface.

#### Co-simulation Interface

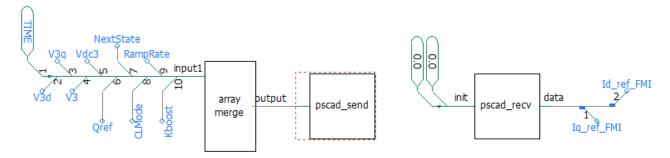

A prototype of an FMI-compatible co-simulation interface for PSCAD has been developed in work package JRA2. It consists of two parts:

- A back-end component used by PSCAD, and a front-end component used by the master algorithm. This part is implemented as user-defined components called pscad\_send and pscad\_recv (see Figure 7 for an example). They take desired input/output signal names as arrays, and at configurable time intervals (co-simulation time-step) they send/receive data over a socket. Socket communication functions are written in C.

- 2. At the time of writing this report, the front-end component has been implemented as a "mock-up FMU", i.e., a Python program that acts as a socket server, exchanging data with PSCAD and exposing it to the master algorithm. It also handles the time synchronization between the master and the slave. The developed co-simulation interface does not currently implement the FMI standard, but is compatible with it. After successfully demonstrating feasibility of the co-simulation with PSCAD, further work would include rewriting the front-end component in C++ with the help of the FMI++ library and encapsulating it into a real FMU.

Figure 7: Example usage of PSCAD components for the FMI-compliant simulation back-end

#### 4.3 ICT Network Simulation

#### 4.3.1 ns-3

#### Overview

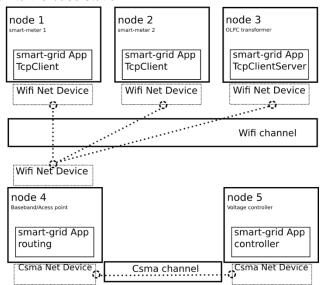

When implementing a co-simulation scenario where all the basic functionalities of a Smart Grid system are included, the telecommunication aspect of the system has to be addressed with caution. Today, many software tools are available for the assessment of communication networks, each one with its own benefits and drawbacks. In the scope of JRA2, the *ns-3* network simulator software was selected (see Deliverable D-JRA2.1). In recent years, ns-3 has become very popular in the network simulation community, mainly due to its high flexibility, which allows programmers to add new attributes without modifying the "core" of the source code, or having to deal with a specific, restricted and complex API.

The development of ns-3 is based on popular object-oriented programming languages (C++ and Python) and the design of ns-3 also follows an object-oriented approach. The default version of ns-3 comes with an extensive library of models, which can be used to describe the components and other

aspects of a communication network (e.g., devices, channels, interfaces, protocols). Additionally, ns-3 provides special objects that are associated with more general grid characteristics, such as the geographical grid extension, the (non-)presence of buildings and other obstacles or the mobility of a node.

#### FMI Export Functionality

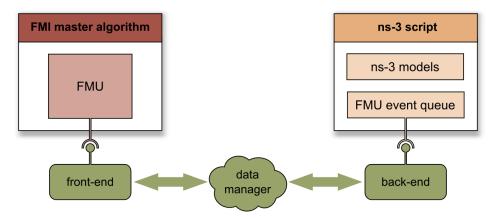

A dedicated ns-3 package called *fmippex* has been developed in work package JRA2, which provides all functionality needed for creating an FMU for CS from a user-defined ns-3 application (typically referred to as "script"). An FMU created with the help of this package implements a tool coupling mechanism that allows to control the execution of the ns-3 simulator and to establish a connection for data exchange during run-time.

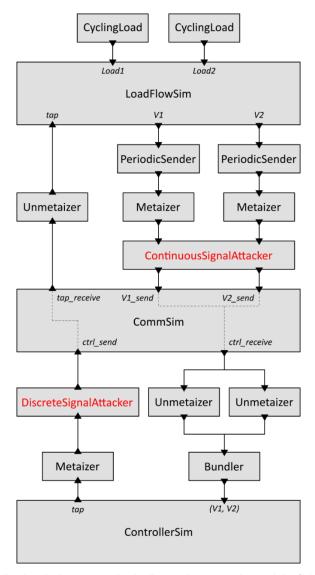

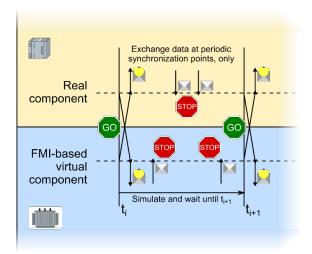

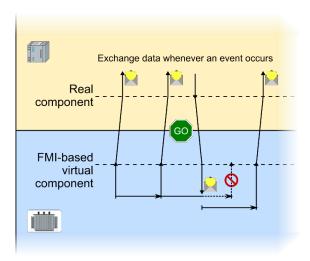

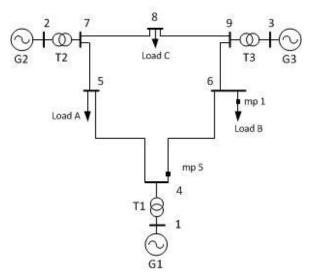

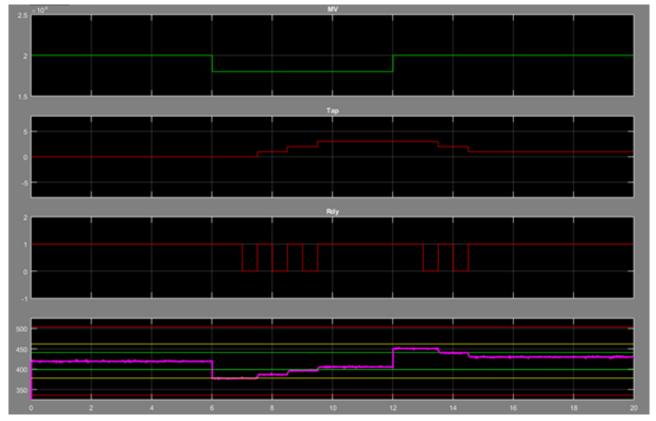

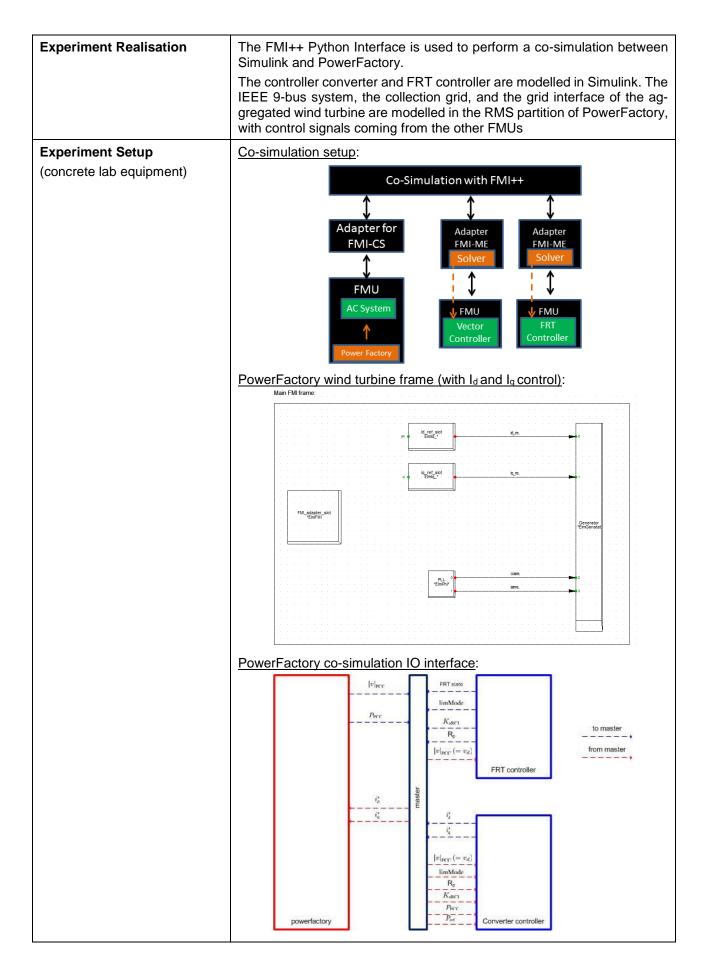

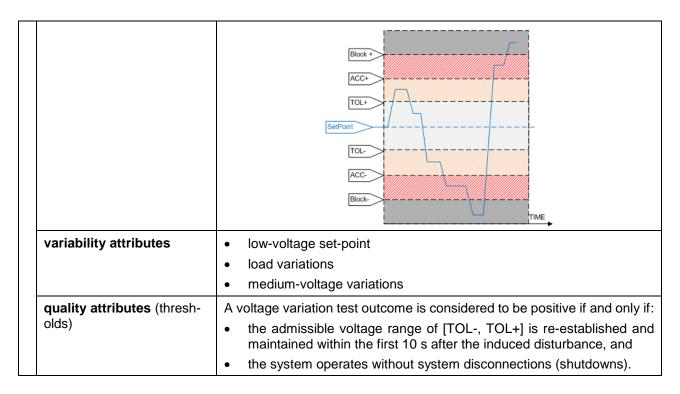

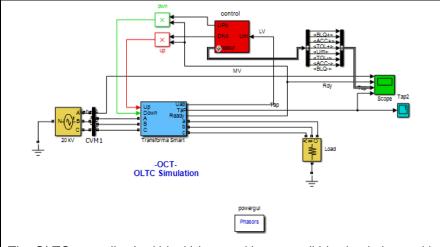

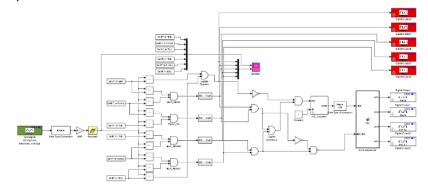

This implementation represents a first prototype, which provides a proof-of-concept that an FMI-based co-simulation interface can indeed overcome the challenges associated with signal-based simulations (see Section 4.1.3). As such, the fmippex package can be successfully used to create FMUs from ns-3 models, even though there are some restrictions to its use: