#### Advanced calibration and measurement techniques for (sub)millimeter wave devices characterization

Galatro, Luca

DOI

10.4233/uuid:245192d2-34c4-44a8-81da-61f12fda5c33

**Publication date**

**Document Version**

Final published version

Citation (APA)

Galatro, L. (2019). Advanced calibration and measurement techniques for (sub)millimeter wave devices characterization. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:245192d2-34c4-44a8-81da-61f12fda5c33

To cite this publication, please use the final published version (if applicable). Please check the document version above.

#### Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Advanced calibration and measurement techniques for (sub)millimeter wave devices characterization

| _1 |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

| _  |  |  |  |

## Advanced calibration and measurement techniques for (sub)millimeter wave devices characterization

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus, Prof.dr.ir. T.H.J.J. van der Hagen, chair of the Board for Doctorates to be defended publicly on Monday 25 November 2019 at 12:30 o'clock

by

#### Luca GALATRO

Dottore in Ingegneria Elettronica, Università degli Studi di Napoli "Federico II", Italy born in Salerno, Italy This dissertation has been approved by the promotors.

Composition of the doctoral committee:

Rector Magnificus, chairperson

Prof. dr. ir. L.C.N. de Delft University of Technology, promotor

Vreede,

Dr. M. Spirito, Delft University of Technology, promotor

Independent members:

Prof. dr. ir. A. Neto, Prof. dr. A.P. Ferrero, Prof. dr. T. Zimmer, Delft University of Technology Keysight Technology, USA University of Bordeaux, France

Prof. dr. M. Schröter, Technical University Dresden, Germany Dr. L.F. Tiemeijer, NXP Semiconductors, the Netherlands

Prof. dr. N. Llombard Delft University of Technology, reserve member

Juan,

Keywords: millimeter wave, sub-THz, on-wafer, calibration, VNA, small-signal,

large-signal, characterization, wafer probes, transmission lines, CPW, EM simulation, de-embedding, load-pull, power control, in-

strumentation ...

Printed by: IPSKAMP printing

Front & Back: Cover designed by 28DO IT https://www.28do.it/

Copyright © 2019 by L. Galatro

All rights reserved.

No parts of this material may be reproduced, stored in a retrieval system, nor transmitted in any form or by any means without the prior written permission of the copyright owner.

ISBN 978-94-028-1813-0

An electronic version of this dissertation is available at

http://repository.tudelft.nl/.

| To Valeria, Elisa and Poppy, the (sometimes literal) reasons I get out of bed every morning |

|---------------------------------------------------------------------------------------------|

| To Marco Di Rosa,<br>a better friend than I could have ever been                            |

| A Nonna Elena                                                                               |

|                                                                                             |

|                                                                                             |

|                                                                                             |

ı

| _1 |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

| _  |  |  |  |

### **Contents**

| 1 | Intr | oduction                                                                                                                                     | 1         |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 1.1  | Challenges related to millimeter wave applications                                                                                           | 3         |

|   | 1.2  | Thesis objectives                                                                                                                            | 6         |

|   | 1.3  | Thesis outline                                                                                                                               | 7         |

| 2 | Con  | ventional high frequency calibration and measurements                                                                                        | 9         |

|   | 2.1  | The Vector Network Analyzer                                                                                                                  | 10        |

|   | 2.2  | VNA Calibration                                                                                                                              |           |

|   | 2.3  | Planar Measurements                                                                                                                          |           |

|   |      | <ul><li>2.3.1 Calibration challenges in planar measurements</li><li>2.3.2 On the definition of the reference planes in probe-level</li></ul> |           |

|   | 2.4  | calibration                                                                                                                                  |           |

| 3 | Adv  | anced (sub)mm-wave planar calibration                                                                                                        | 31        |

|   | 3.1  | Probe-tip planar calibration                                                                                                                 |           |

|   |      | 3.1.1 Multimode propagation in calibration standards                                                                                         |           |

|   |      | 3.1.2 Calibration transfer                                                                                                                   |           |

|   | 3.2  | Direct on-silicon calibration                                                                                                                |           |

|   |      | 3.2.1 Measurement based methods for characteristic impedance                                                                                 |           |

|   |      | extraction of transmission lines                                                                                                             |           |

|   | 2 2  | 3.2.2 $Z_0$ extraction using EM simulations                                                                                                  |           |

|   |      |                                                                                                                                              | 30        |

| 4 | _    | acitively loaded inverted CPWS for distributed calibration                                                                                   |           |

|   |      | de-embedding                                                                                                                                 | <b>57</b> |

|   |      | Direct DUT-plane calibration                                                                                                                 |           |

|   | 4.2  | CL-ICPW concept                                                                                                                              |           |

|   | 43   | Design of calibration/de-embedding kit                                                                                                       |           |

|   |      | TRL Calibration/de-embedding                                                                                                                 |           |

|   | 4.5  | Measurements of intrinsic devices on SiGe Technology                                                                                         |           |

|   |      | Conclusions                                                                                                                                  |           |

| 5 |      | GHz MSALP for mm-wave devices characterization                                                                                               | 77        |

| _ |      | Conventional load-pull techniques                                                                                                            |           |

|   |      | 5.1.1 Mixed-signal active load-pull                                                                                                          |           |

viii Contents

| 0.2                                           | Millimeter wave active load-pull                      | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3                                           | Waveguide based test-set                              | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                               | 5.3.1 Measurement stability                           | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                               | 5.3.2 Driving power capability                        | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4                                           |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               | 5.4.1 Schematic optimization                          | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.6                                           |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.7                                           |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.8                                           |                                                       | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F 0                                           |                                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.9                                           |                                                       | 06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5 10                                          |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1                                           | •                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.2                                           | 6.1.1 Frequency extension                             | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.2                                           | 6.1.1 Frequency extension                             | 106<br>107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.2                                           | 6.1.1 Frequency extension                             | 106<br>107<br>108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                               | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.3                                           | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>110<br>111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.3                                           | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>110<br>111<br>113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.3                                           | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>110<br>111<br>113<br>113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.3                                           | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>113<br>114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>114<br>115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>113<br>114<br>115<br>116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>113<br>114<br>115<br>116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>114<br>115<br>116<br>117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>114<br>115<br>116<br>117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul> | 6.1.1 Frequency extension                             | 106<br>107<br>108<br>108<br>110<br>111<br>113<br>113<br>114<br>115<br>116<br>117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

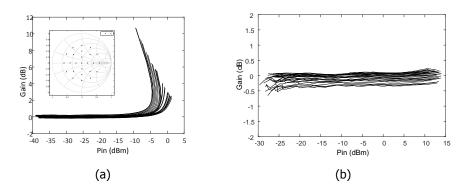

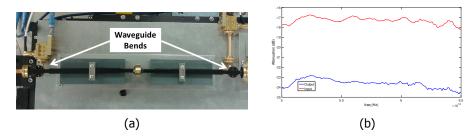

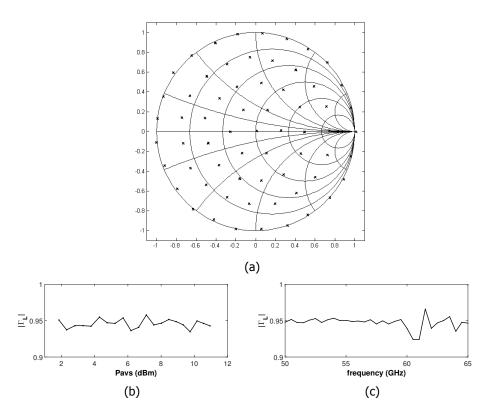

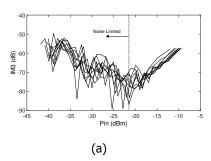

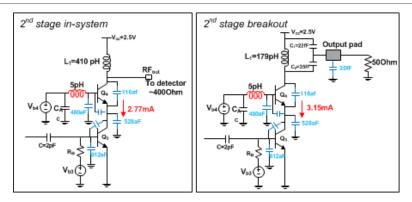

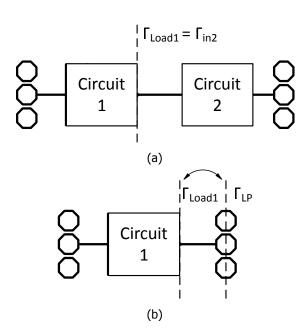

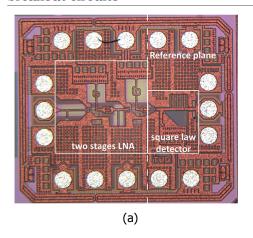

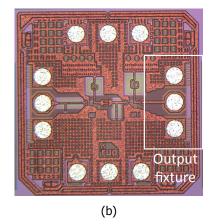

|                                               | 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br><b>VNA</b> | 5.4 System configuration 5.4.1 Schematic optimization 5.5 System operation 5.6 System performances 5.6.1 Impedance control 5.6.2 Stability 5.6.3 Two tones 5.7 Large signal characterization of mm-wave devices using mixed signal active load-pull 5.8 Large signal characterization of power amplifiers using active load-pull at mm-waves 5.9 Load-Pull aided small signal characterization of millimeterwave breakout circuits 5.9.1 Breakout circuits characterization flow 5.9.2 Standalone characterization of a LNA breakout 5.10 Conclusions  VNA based small-signal and large-signal characterization at (sub) millimeter wave frequencies |

Contents ix

| 7  | Conclusions 1 |         |                                                               |     |  |  |

|----|---------------|---------|---------------------------------------------------------------|-----|--|--|

|    | 7.1           | Outco   | ome of the thesis                                             | 123 |  |  |

|    |               | 7.1.1   | Calibration                                                   | 123 |  |  |

|    |               | 7.1.2   | Small and large signal measurements                           | 125 |  |  |

|    | 7.2           | Futur   | e work                                                        | 126 |  |  |

|    |               | 7.2.1   | Cross-talk correction during on-wafer calibration             | 126 |  |  |

|    |               | 7.2.2   | Comparing CL-ICPW to conventional de-embedding                | 127 |  |  |

|    |               | 7.2.3   | Expanding the use of active load-pull at millimeter waves 127 |     |  |  |

|    |               | 7.2.4   | Automatic active load-pull at sub-millimeter wave fre-        |     |  |  |

|    |               |         | quencies                                                      | 127 |  |  |

| A  | Wav           | e form  | nalism, characteristic impedance and impedance trans-         | -   |  |  |

|    | forn          | nation  |                                                               | 129 |  |  |

|    | A.1           | Travel  | lling modes and travelling waves                              | 129 |  |  |

|    | A.2           | Pseud   | lo-Waves                                                      | 130 |  |  |

|    | A.3           |         | trix, Z-matrix, cascade matrix                                |     |  |  |

|    |               |         | Impedance renormalization                                     |     |  |  |

|    | A.4           | Power   | Waves                                                         | 133 |  |  |

| В  | CPV           | 7 analy | ysis by means of conformal mapping                            | 135 |  |  |

| Bi | bliog         | raphy   |                                                               | 137 |  |  |

| Su | mm            | ary     |                                                               | 147 |  |  |

| Li | st of         | Public  | cations                                                       | 151 |  |  |

| Ac | knov          | wledge  | ements                                                        | 155 |  |  |

| Cu | ırric         | ulum V  | /itæ                                                          | 159 |  |  |

| _1 |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

|    |  |  |  |

| _  |  |  |  |

1

#### Introduction

Homo Sapiens Sapiens is the only extant human (sub)species [1], and arguably the most "impactful" animal species in the world. The impact of human kind can be measured by the influence humans have on the ecosystem they live in (the Earth), which is not comparable to any other single animal species in the Earth's history. In time, the reasons why humans grew to "shape" the world have been much discussed. As a matter of fact, humans are not the biggest [2] nor the strongest [3] living animals, while other species have been found to have similar intelligence [4] and complex social structures [5]. Many studies relate the human success to the ability of standing, or manufacturing and employing tools (although similar skills can be found also in orangutan and chimpanzees [6]), but probably the most important skill that distinguishes humans from any other animal is their capability to communicate. It is true that several animals are capable of complex communication and language (Bottlenose Dolphins can call each other by name [7], while Elephants can even communicate using seismic signals [8]), but humans are the only ones capable of transmitting information through both space (communication can be achieved even on very long distances) and time (the knowledge acquired can be preserved during time, transmitted and increased during generations). In this respect it can be stated that the human world-conquer campaign started when written language was invented. Until then, although information could be transmitted orally, its preservation during time was subject to alteration. With the invention of writing, the knowledge acquired by humans had the possibility to be stored for long time and possibly transported to very far regions, allowing the accumulation and the dissemination of knowledge, leading to a faster species advancement. During centuries, the capability of efficiently transporting information also determined the influence and the technology advancement of a civilization. It is not by chance that the first advanced postal service (the cursus publicus) was established under Augustus Caesar, the first Roman emperor [9]. Also, the invention of *printing* is considered one of the cornerstones that characterizes the passage from the *Middle* Age to the more technologically advanced Renaissance, due to the novel capability 2 1. Introduction

Figure 1.1: a) Bottlenose dolphins rely on (ultra)sound production to communicate, hunt and navigate, and they have been found to be able to call other individuals by name [7]. b) African Elephants can use complex communication mechanism, including using seismic waves to signal position and danger [8].

to promptly reproduce written information in mass production, enormously augmenting its dissemination. Until modern history, however, information could only be transmitted in *deferred* time: the information was first produced and written, and then eventually transported with processes that could take long times depending on the means of transport. Only with the invention of telecommunication, starting in the early 19th century, information could be transmitted in real time. Telecommunication allowed the technological leap that characterized the last two centuries, and every technical step from then on has been supported by a newer and more effective way of communicating. It first was telegraph and phone, which still required physical connection between the communication points (by cable), basically allowing only one-to-one connection. Then, radio and television were invented, wireless technologies creating the possibility of transmitting information from one to many. Later in the 20th century, internet gave the possibility to individuals to independently access a high volume of information from their home, and the introduction of cellular phone allowed people to communicate from any position in the world. The era of smartphones, the era we currently live in, is characterized by an enormous availability of information, to basically anybody, everywhere in the world. It is reasonable at this point to start wondering what will be the next telecommunication step, and how to enable it. In the last decade, the fast development of electronic devices, in conjunction with computer science and artificial intelligence (AI) has fostered the development of new applications that promise to revolutionize everyday life, from business to entertainment. From big data analytics and augmented reality used to support industry, to 3D media and virtual reality for video gaming, these emerging applications are, day by day, changing the way telecommunication systems are used. However, in a world in which the portability is the key requirement for each device, the real challenge is to make these applications sustainable for the mobile network infrastructure. As a matter of fact, such bandwidth

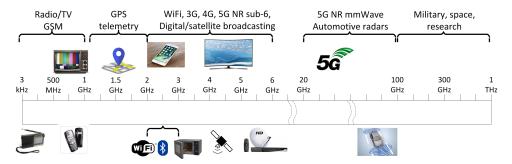

Figure 1.2: This table depicts the spectrum occupation by most of the RF/microwave consumer application. Almost all current commercial wireless application employ frequencies lower than 6 GHz, while millimeter waves are at the moment mostly dedicated to military and space application.

demanding applications need reliable and efficient connectivity, where any high latency or data corruption would just be not sustainable, determining the failure of the application. To really bring these applications to the end users, new communication paradigms will need to be introduced, with an increasing occupation of an already crowded radio spectrum. The congestion of the RF and microwave spectrum risks to be the real bottleneck for the development of new applications. Most of wireless applications work at frequencies lower than 6 GHz (see, Figure 1.2), and communication channels are typically bandwidth limited, while most of the bandwidth slots are already allocated by local and global regulations, limiting the space for the introduction of new applications and systems. On top of that, data intensive applications would need large bandwidth allocation and sufficient guard space to avoid interference. For these reasons, the attention is moving towards the exploitation of the underutilized millimeter wave and sub-millimeter wave portion of the spectrum (30 GHz to 1 THz), where the high carrier frequency and low spectrum congestion would guarantee large bandwidth availability, enabling the needed ultra-high data rate communication capability. In this respect, also the discussion about the next generation of mobile broadband technology (5G) is moving towards considering millimeter wave frequencies as possible candidates for future application deployments, with frequencies between 30 GHz and 87 GHz raising interest in the research community, with some already being assigned for testing [10].

### 1.1. Challenges related to millimeter wave applications

Developing applications and shifting wireless telecommunication to millimeter wave frequencies is, unfortunately, not a trivial task. The shortcomings are first of all physical, as propagation of electromagnetic waves at higher frequency is more prone to suffer from atmospheric conditions. Atmospheric gases interact with electromagnetic waves, in specific sub-bands, blocking long distance signal propagation (see, Figure 1.3a). Moreover, phenomena such as high humidity and rain tend to increase propagation losses in the mm-wave range. This means that outdoor trans-

4 1. Introduction

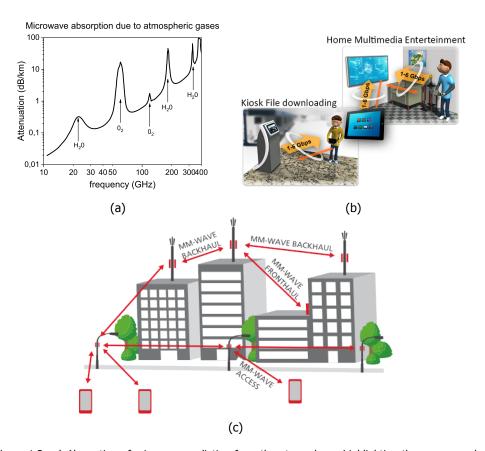

Figure 1.3: a) Absorption of microwave radiation from the atmosphere, highlighting the oxygen and water attenuation peaks. b) In-door application for millimiter wave frequencies include close-range media distribution and kiosks for mobile syncronization of large data. c) Open-space application for mm-wave frequencies require clear line-of-sight between the communicating devices, requiring dense networks of base stations and access points.

missions would be strongly affected by weather conditions, which cannot be controlled if not barely predicted with relatively short notice time. For these reasons, millimeter wave wireless technologies are mainly intended either for outer space applications (satellite-to-satellite applications, space imaging), where the electromagnetic propagation is not affected by the atmospheric conditions, or for short range applications, like automotive radar, security imaging, indoor media sharing (for home/in-flight entertainment, or for office networks), virtual reality or data sharing kiosks (see, Figure 1.3b), so that the electromagnetic propagation would not be compromised by the high attenuation related to atmospheric dispersion. The use of mm-wave frequencies for cellular communication is also being considered [11] (see,Figure 1.3c). The way this kind of application is conceived, however, requires clean line-of-sight between communicating devices, and it is constrained

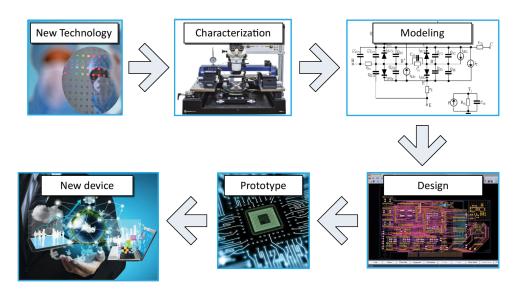

Figure 1.4: Development flow for (telecommunication) electronic devices based on semiconductor technologies.

by the use of high-density small cells in order to neglect the effects of high atmospheric attenuation.

While the physical constraints define the space of applicability for millimeter wave wireless technologies, the development of any commercial application needs to be supported by a proper technological advancement. In this respect, the continuous improvement in performances of integrated/semiconductor devices, in terms of speed of operation, space occupation and power consumption is fostering the implementation of the first commercial millimeter wave systems [12]. Technology, however, is still not mature enough to open the possibility for consumer applications in the (mobile) telecommunication market for millimeter waves. When considering mobile applications, electronic devices need to be developed to guarantee some main requirements:

- As mobile systems rely on limited power supply (i.e., batteries), the power consumed by the electronic circuitry should be limited;

- The quality of the signals transmitted (and received) should be sufficient to guarantee a reliable communication;

- The system should guarantee high reliability (durability) and resilience to adapt to different communication conditions.

As current state-of-the-art technology still presents limitations in meeting those requirements for millimeter wave communications, the further development of new devices is necessary [13]. The development flow characterizing the realization of a commercial application is composed of several steps, the most important of which

1

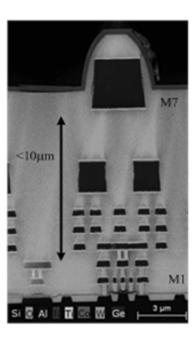

are summarized in Figure 1.4. First step is represented by the definition of the device fabrication technology, which is the set of chemical/mechanical processes and rules used to fabricate electronic devices on wafers of semiconductor materials. The semiconductor industry is characterized by a continuous innovation in the fabrication technology, involving improvements in the material composition, as well as in the geometrical feature sizes. These directly impact on the electrical performances of the individual devices that are embedded in the semiconductor material (the front-end-of-line or FEOL) and on the interconnection between the devices (back-end-of-line or BEOL). The development of a new fabrication technology brings, as a consequence, a new generation of electronic devices, both active (i.e., capable of actively control/amplify electrical signals, like transistors) and passive (i.e., transmission lines, capacitors, inductors, etc.) which need, first of all, to be characterized. Using accurate data from measurements, the device characteristics can be used for the development of compact models, to be used for the prediction of the device performances in different working conditions. The use of models allows combining different devices to design complex circuitry, where the overall performances can be predicted with extensive use of circuit simulators. The design is finally used for the realization of a prototype circuit, manufactured in the target production technology, and when the prototype is successfully tested it can be then turned into a final product to be introduced to the market. If the performances of the prototype do not comply with the specifications, the development cycle needs to restart from one of the intermediate steps. Each cycle can have several months of duration, and be characterized by costs that can sum up to several millions of Euro. It is therefore essential from both an engineering and economic point of view to optimize the device development cycle. An important condition for the reduction of time-to-market and development costs of new devices is the availability of **accurate** and **reliable** characterization processes, capable of measuring the characteristics of the devices under test (DUTs) directly in the environment in which they are manufactured (i.e., on-wafer) and in the frequency range in which they are supposed to be employed. While for RF and microwave frequencies many solutions already exist and are widely available on the market, when it comes to higher frequencies (i.e., higher than 60 GHz) the availability of measurement equipment reduces, and the existing instrumentation presents lower performances in respect to the microwave counterpart. It becomes of primary importance, for the fostering of millimeter wave applications, to work towards the development of novel characterization strategies, allowing to achieve accurate measurements of on-wafer millimeter wave devices.

#### 1.2. Thesis objectives

This thesis concentrates on the analysis of some of the major challenges related to the characterization of (sub)mm-wave devices, especially regarding on-wafer measurements, and proposes a series of possible solutions and novel approaches. The analysis is first dedicated to the *calibration* of on-wafer test-benches, which is the set of processes required to correct all the errors introduced into the measurements by the characterization equipment. The main bottlenecks of conventional calibration

1

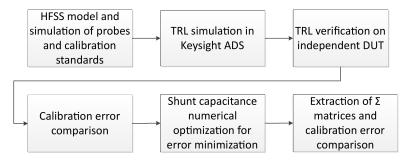

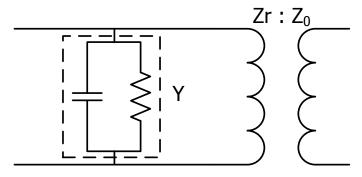

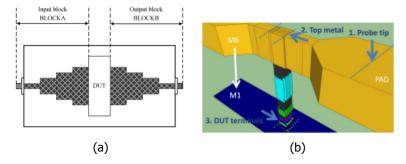

approaches at millimeter waves are first identified, and a novel simulation-based approach for the characterization of on-wafer calibration artifacts is proposed, with a focus on transmission lines. Then, we introduce a novel transmission line structure, the capacitively loaded inverted coplanar waveguide (CL-ICPW), dedicated to the implementation of direct calibration on silicon back-end-of-line (BEOL), which allows moving the measurement plane directly at the intrinsic (FEOL) device plane. The focus of the thesis will then shift towards the implementation of accurate instrumentation and test-benches. First, we describe the use of a mixed-signal active load pull architecture for the characterization of millimeter wave devices in the frequency range between 50 GHz and 65 GHz, including the design of the dedicated waveguide-based test-bench and its optimization for low- and high-power devices. Then we introduce a novel approach for the measurement and the control of power during small and large signal characterization of millimeter wave devices, which allows using conventional measurement instrumentation (Vector network analyzers, millimeter wave extenders, power meters) to achieve refined power control and vector corrected power measurement with unprecedented speed. This method also opens the possibility to develop active load-pull approaches for frequencies up to 1 THz, as will be introduced by the end of this dissertation.

#### 1.3. Thesis outline

This dissertation is structured as follows.

In Chapter 2, a general overview of the conventional calibration approaches for microwave (on-wafer) measurements is provided, in order to highlight the limitations of these methods when the measurement frequency is increased towards the millimeter wave range.

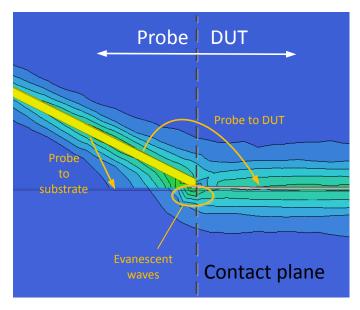

In Chapter 3, an analysis on the sources of error in millimeter wave measurement test-benches for on-wafer measurement is performed. First, the attention is posed on probe-tip calibrations, and the error associated with the common practice of transferring the calibration error terms from an off-wafer calibration substrate to an on-wafer environment in which the device under test (DUT) is embedded, are analyzed. Then, the chapter will highlight the importance of performing the calibration using test-structures already embedded in the DUT environment (i.e., on-wafer), proposing a novel approach for extracting the characteristic impedance of transmission lines employed for thru-reflect-line (TRL) calibration, which is the most important parameter to be known during calibration whilst the more difficult to properly extract by means of measurements.

Chapter 4 introduces the use of capacitively loaded inverted CPWs (CL-ICPW) in test fixtures for (sub)mm-wave device de-embedding. These transmission lines allow implementing a distributed TRL de-embedding of the fixture, opening the possibility for *direct* calibration up to the DUT reference planes, without the need of additional de-embedding procedures.

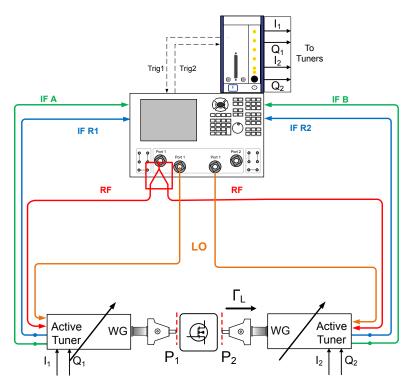

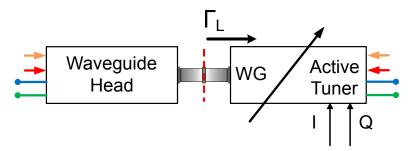

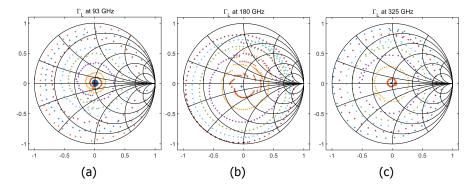

Chapter 5 describes the implementation of a waveguide-based mixed-signal active load-pull test-bench, working in the WR-15 waveguide bandwidth, and its use for the large-signal characterization of millimiter wave devices and circuits.

In Chapter 6, a methodology is described for the accurate measurement and

8 1. Introduction

1

control in conventional (sub)mm-wave small- and large-signal test-benches, and a novel approach for load-pull measurements at frequencies higher than 75 GHz is proposed.

Finally, Chapter 7 will be used to draw some conclusions and make some recommendation for future developments and use of the present work.

# 2

# Conventional high frequency calibration and measurements

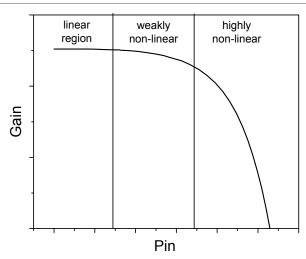

The characterization of high frequency electronic devices relies on the quantification of diverse device properties by means of measurements performed on a device-under-test (the DUT) at the target operating frequency and, in case an active device is considered, under different operating conditions. The kind of parameters that need to be measured also depends on the application in which the DUT has to be employed. For devices that need to be used in telecommunication applications, for example, it can be important to quantify the capability of properly reproducing an analog signal, without loss of information. This capability is typically linked to the *linearity* of the device. A linear device is capable of reproducing a replica (in frequency and phase) of an input signal, without introducing any distortion<sup>1</sup>. The linearity of active devices (like transistors, or amplifiers) can be typically quaranteed by providing low-power signals to the device, and then measuring its response. In this sense, an active device is defined to operate in its linear region when its DC characteristics (i.e., its biasing conditions) are not influenced by the RF signal applied. For this reason, linear measurements of active devices are also commonly addressed as small-signal measurements. On the other end, to verify

Parts of this chapter have been published in Improved RSOL planar calibration via EM modelling and reduced spread resistive layers (2015) [14], On the definition of reference planes in probe-level calibrations (2016) [15] and Fused Silica based RSOL calibration substrate for improved probe-level calibration accuracy (2016) [16].

<sup>&</sup>lt;sup>1</sup>Note that the maximum level of distortion discriminating linear from non-linear operation is typically set through standard definitions using various metrics, like *intermodulation distortion*, *error vector modulation*, *spectral regrowth*, etc.. Discussion of these metrics is out of the scope of this dissertation.

the device linear performances, it might be needed to drive it with larger input power levels. In this case the power provided to the input of the device needs to be increased so that it can influence its DC characteristic, and in this case is said to be in large-signal operation. This kind of operation typically introduces nonlinearity effects in the device RF behavior, that need to be measured (large-signal measurements). The complete characterization of active devices always requires both small- and large-signal measurements even for millimeter and sub-millimeter frequencies. This chapter will be mostly dedicated to the most common measurement system employed for high frequency small signal measurements, the vector network analyzer (VNA). First part of this chapter will be dedicated to a general description of the VNA. Then, important part of the analysis of the measurement systems is dedicated to the errors introduced by the equipment, and the calibration strategies that are needed for correcting them. A more specific analysis of the use of VNAs at millimeter waves and beyond will be presented in Chapter 6. The last part of this chapter will be dedicated to the use of VNA setups for the measurement of on-wafer devices, and the related calibration strategies. Special attention is dedicated to the ambiguities in the selection of the calibration reference plane during planar measurements, and on how to choose the appropriate calibration approach depending on the frequency of operation.

#### 2.1. The Vector Network Analyzer

The *Scattering matrix* is widely used to describe the electrical behavior of linear devices [17]. The S-parameter of an N-port network, where each port i is terminated to a specific reference impedance  $Z_{0i}$  are defined as:

$$\begin{pmatrix} b_1 \\ \vdots \\ b_n \end{pmatrix} = \begin{bmatrix} S_{11} & \cdots & S_{1n} \\ \vdots & \ddots & \vdots \\ S_{n1} & \cdots & S_{nn} \end{bmatrix} \cdot \begin{pmatrix} a_1 \\ \vdots \\ a_n \end{pmatrix}$$

(2.1)

Where  $a_i$  is the *incident* wave at a specific port i, while  $b_i$  is the *reflected* wave at a specific port i. It is important to notice how the S-parameters, and the incident and reflected waves, are reported in literature with different formalism, which sometimes lead to slightly different definitions and properties of other related parameters [18, 19]. In Equation (2.1) and in general in this dissertation, the pseudo-waves formalism is used, based on the one presented in [19], and described in detail in Appendix A. In the case of RF/microwave devices, S-parameters can be employed to compute relevant figures of merit like *small-signa gain*, *insertion loss*, *reflection coefficient* or *amplifier stability*. The measurement of the (frequency dependent) S-parameters of a DUT is commonly performed by means of a vector network analyzer (VNA) [20]. A VNA can be used for measurements of DUTs with one or multiple ports, and is capable of frequency sweeping (from kHz to 1.1 THz, employing different hardware setups) and power control at each test port. In this section, we present a general overview of the principle of operation of VNAs, discussing the limitations associated to this kind of equipment when measuring at (sub)mm-waves.

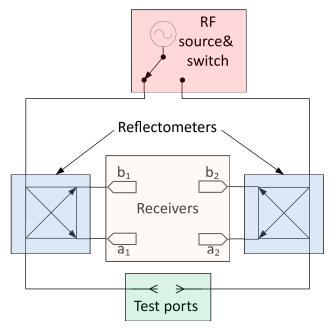

Figure 2.1: General system schematic of a VNA, including the main four stages.

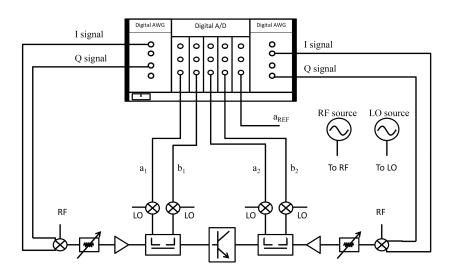

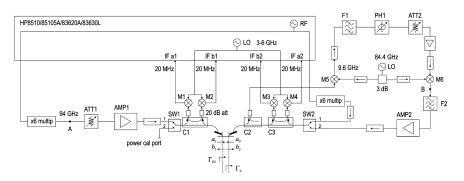

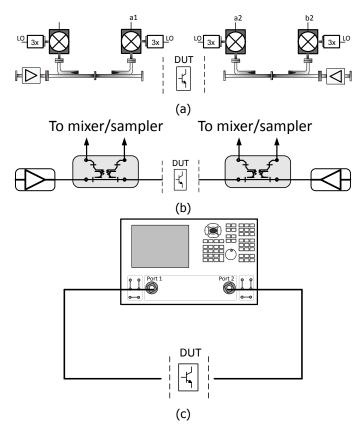

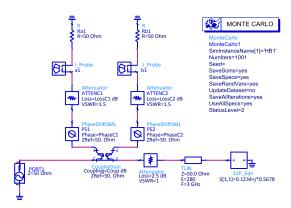

In general, it is possible to schematize a VNA as composed of four main stages (see, Figure 2.1 for two-port example):

- 1. *The signal generation stage*, where an RF signal is generated, at an appropriate frequency and power level, for each test port.

- 2. *The reflectometer stage*, where replicas of the *incident* and *reflected* waves are sampled, for each test port. The sampled waves are typically acquired by means of intermediate frequency receivers;

- 3. *The test ports*, representing the connection point between the VNA and the DUT ports;

From this simple schematic, several variations are possible in terms of number of test ports, number of sources and receivers, add-ons for advanced measurements, etc..

#### Signal generation

The measurement of the S-parameters is based on the capability to provide an appropriate stimulus, at a given frequency of operation, and to measure the corresponding response of the device. The signal provided to the DUT is typically sinusoidal, but more advanced measurements may require more complex signal generation (pulsed, multi-tone, modulated, etc..). The generation of sinusoidal, frequency swept signals is typically performed by means of synthesizers, where a

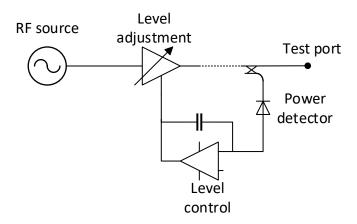

Figure 2.2: Simplified schematic of an ALC loop in VNAs.

phase locked VCO is employed to provide a swept frequency response in a certain, limited, frequency range [21]. In order to guarantee broadband frequency generation, multi-path configurations are typically used, where frequency multiplication, division and mixing allow using a single VCO for multi-octaves frequency coverage [22]. An important aspect to be taken into account during generation is the power control: having a leveled and controllable power delivered at the test-port is generally desirable when measuring active devices, where the DUT's operation (small signal or large signal) needs to be characterized versus the stimulus level (see, also Chap. 6). In VNAs, the power control is achieved by means of the *automatic loop control* (ALC). The ALC system is conceptually simple: the power at the test-port is monitored by means of a detector, while a negative feedback loop is used to control a level adjustment unit (a variable gain amplifier or a variable attenuator) allowing proper power leveling, as shown in Figure 2.2.

#### Reflectometers

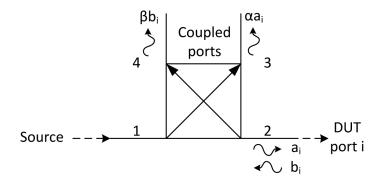

Following the definition of S-parameters [18], the measurement of such quantities is based on the capability of sampling, at each DUT port i, the incident wave  $a_i$  and the reflected wave  $b_i$ . This task is typically performed by means of *reflectometers*. A reflectometer is, at its essence, a 4-port linear device, conventionally schematized as in Figure 2.3. Supposing that the VNA source is connected to port 1 of the reflectometer, while port i of the DUT is connected to port 2 of the reflectometer, this device allows to have at the coupled ports 3 and 4 quantities proportional to the scattered waves  $a_i$  and  $b_i$ , respectively. Different kinds of directional devices can be used to realize a reflectometer, like *directional couplers*, *directional bridges* or splitter based components (i.e.,  $1 + Gamma\ reflectometers$ ) [22]. Regardless of the implementation, reflectometers are typically characterized by some fundamental parameters, such as the *mainline loss* L (attenuation of the  $a_i$  wave), the *coupling* C

Figure 2.3: Generalized schematic of a reflectometer.

(attenuation of the coupled wave), the *directivity* D (ability to separate the coupled  $a_i$  wave from the  $b_i$  wave) and the *isolation* I (power coupling between the input port and the isolated port, i.e., leakage from input to b wave and from output to a, which is linked to directivity and coupling as D = I + C dB). Ideally, for a perfect signal separation (and S-parameter measurement) the losses should always be negligible, the directivity infinite, and the coupling equal between the ports. In this case, the coupled waves would be directly proportional to the scattered waves ( $\alpha$  and  $\beta$ b), and their ratio could be directly linked to the S-parameter of the DUT. In practice, the inevitable non-idealities make the coupled waves always affected by frequency dependent errors. Calibration procedures allow, in principle, to correct for these errors, irrespectively of the quality of the reflectometer parameters (also called *raw performances*), and how they deviate from ideality. In reality, however, good raw performances have strong impact on the *stability* of the calibration [21]. The implications of this on millimeter wave measurements will be further discussed in Chapter 5.

#### **Test ports**

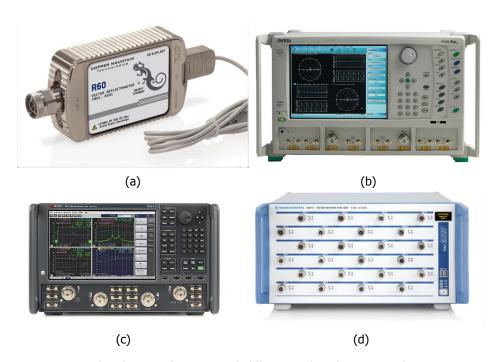

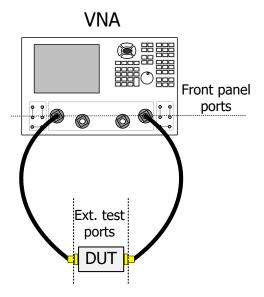

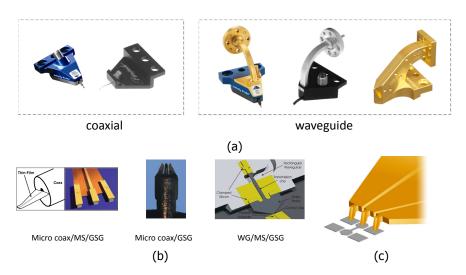

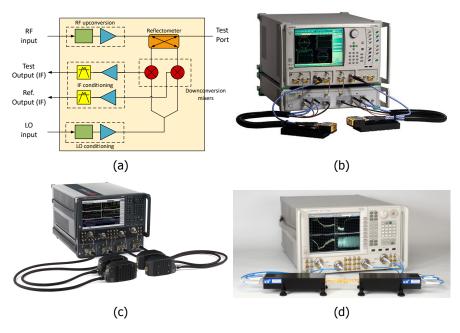

The test ports of a VNA represent the interface between the instrument and the DUT. In principle, a VNA can have one or multiple test ports, while the most common configurations for modern commercial VNAs are 2-ports and 4-ports. Some examples of VNAs with different numbers of test ports are displayed in Figure 2.4. The primary VNA test-ports are constituted by coaxial rugged connectors, which are typically present in the instrument front panel or in an external test set. However, being not always possible to connect a DUT directly at the front panel ports of a VNA, the typical configuration involves the use of coaxial cables to connect the instrument to the DUT ports. In this case, the *extended* test ports are considered to be the coaxial connectors interfacing with the DUT, see Figure 2.5. In principle, the VNA test ports can be seen as the plane at which the S-parameters measurement actually takes place. In practice, the actual measurement plane in a VNA is at the

Figure 2.4: Examples of VNA configurations with different number of test ports. a) Copper Mountain Technologies R60, a 1-port VNA operating from 1 MHz to 6 GHz. b) Anritsu VectorStar, 2-port VNA operating from 70 kHz to 70 GHz. c) Keysight PNAX, 4-port VNA operating from 10 MHz to 67 GHz. d) Rohde&Schwartz ZNBT8, 24-port VNA operating from 9 kHz to 8.5 GHz.

receivers, where the physical quantities (i.e., the scattered waves) are effectively acquired. For this reason, VNAs need procedures that allow relating the acquired quantities to the S-parameters at the test ports, or more specifically to the measurement reference planes. These procedures go under the name of *calibration techniques*, and will be discussed further in this chapter.

#### 2.2. VNA Calibration

When using the VNA to perform the characterization of a DUT, the goal of the measurement is to obtain the physical characteristics (i.e., the S-parameters) of the device at a user defined reference plane (i.e., the extended test ports in Figure 2.5). It is necessary to model all the system imperfections present between the instrument's primary test ports and the measurement reference planes. This is typically done by defining a fictitious network incorporating the system's errors. The process of defining, quantifying and mathematically correcting this error network, in order to set the measurement reference planes, is called VNA calibration. In general, two big groups of errors can be identified: *systematic* and *random* errors. While random sources of errors (i.e., noise, repeatibility, etc..) can only be described by means of qualitative/statistic figure of merit, systematic errors (like

Figure 2.5: Example of test port extension from VNA front panel to the DUT measurement plane, by means of coaxial cables.

losses, directivity, source match, load match, etc..) generally allow a proper quantification, and therefore can be corrected by means of calibration. For a complete review of the systematic contribution to error in a VNA, the reader is invited to read [23]. When the error network is subtracted from the measurement results, it is possible to obtain a *corrected* measurement representing the most accurate estimate of the actual S-parameter of the DUT.

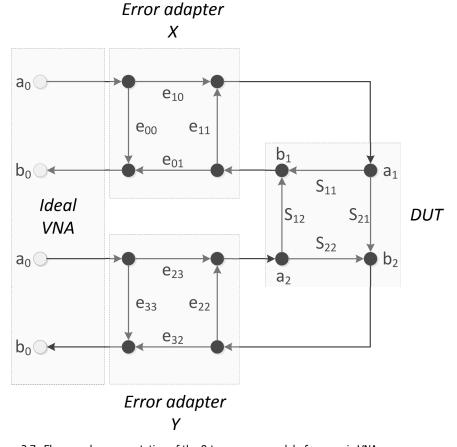

The way a certain calibration procedure is performed depends, on a first instance, on the way the error network is modeled. As a matter of fact, diverse error models exist, which lead to different calibration methods. For the specific case of two-port VNAs, two main error models are typically employed for calibration, the *12-terms* and the *8-terms*.

#### 12-terms error model

The 12-terms error model is the most widely used, while it was developed for older, less advanced VNA architectures, that were based on the use of only three receivers [22]. In this case a clear differentiation between the forward (power is applied at port 1) and reverse (power is applied at port 2) measurement directions is needed. As a matter of fact, this model describes the two measurement phases with two separate error sets (called the forward and reverse error *adapters*), which can be conveniently represented by means of flow graphs, as shown in Figure 2.6. The model includes a total of 12 independent *unkwnown* terms, describing the overall systematic errors in the VNA, and that need to be quantified in order to correct the measurements. The terms  $e_{30}$  and  $e'_{03}$  are associated to cross talk errors, and can typically be directly measured using  $S_{21}$  and  $S_{12}$  obtained when terminating port 1

Figure 2.6: Flow graph representation of the 12-terms error model of a generic VNA

and port 2, reducing the number of unknowns to 10. For the other terms, for the forward mode, a typical calibration procedure would require to:

- 1. Measure three independent one-port DUT with known reflection coefficient (*calibration standards*) to evaluate  $e_{00}$ ,  $e_{11}$  and  $e_{10}e_{01}$  (also called one-port calibration).

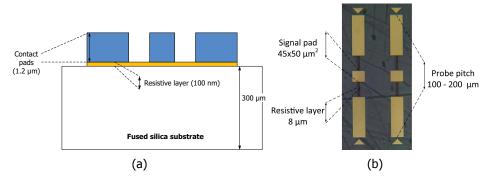

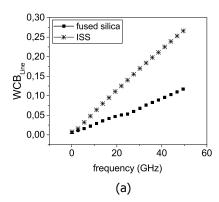

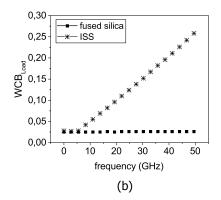

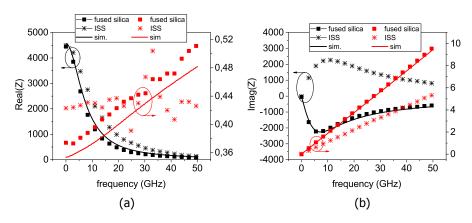

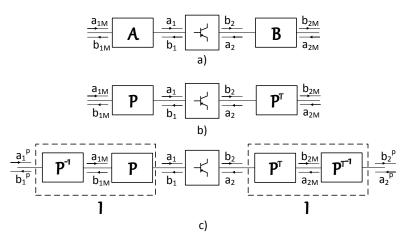

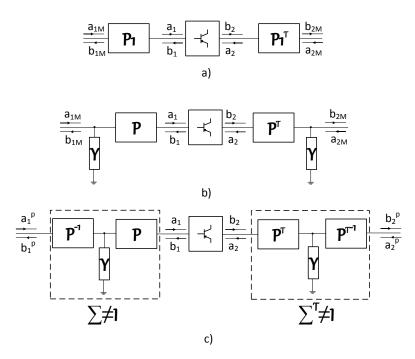

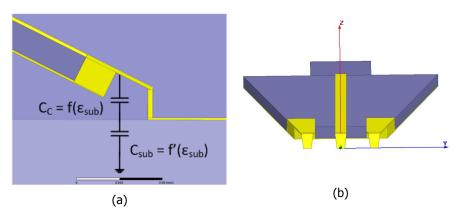

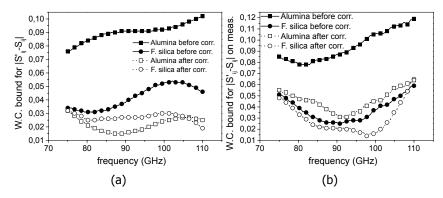

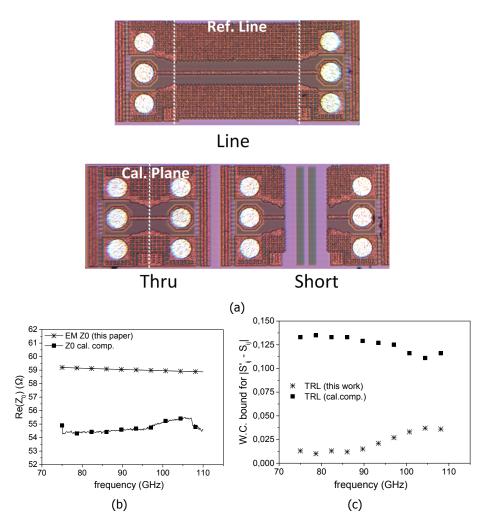

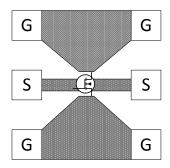

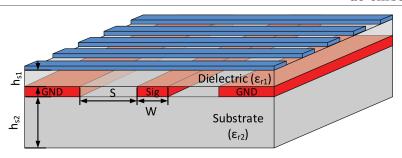

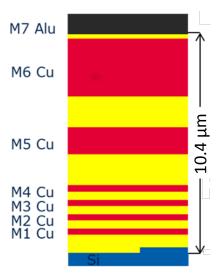

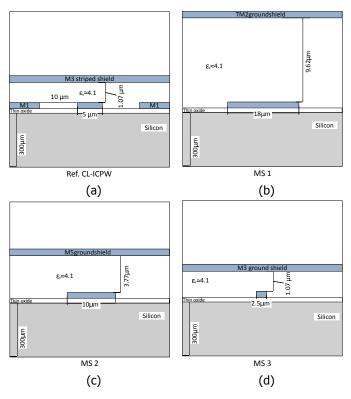

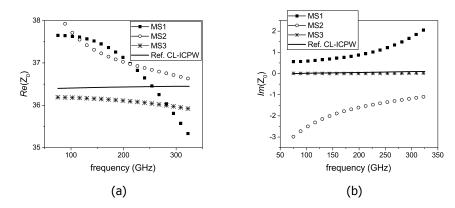

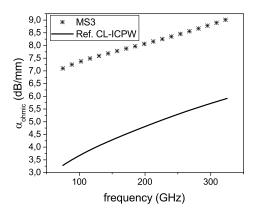

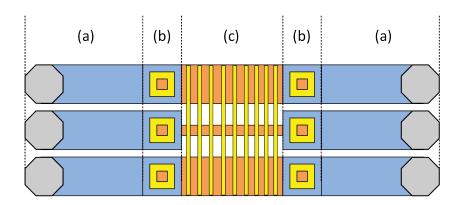

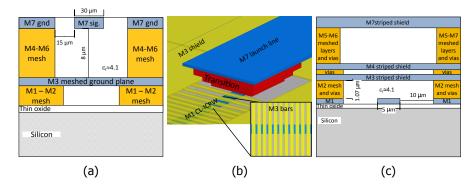

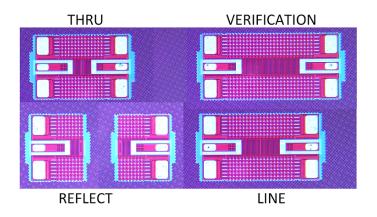

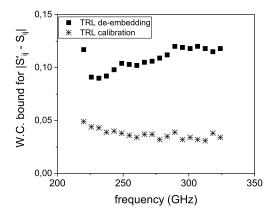

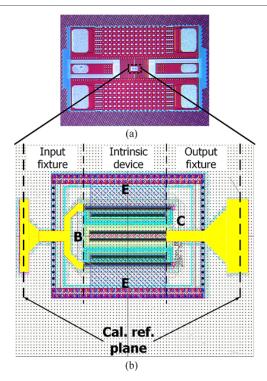

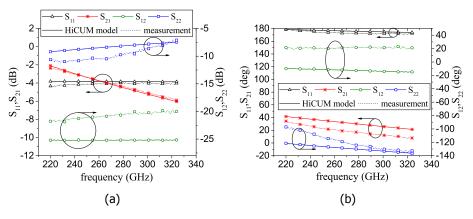

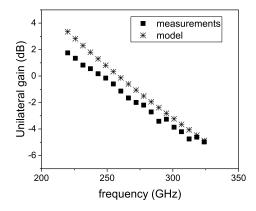

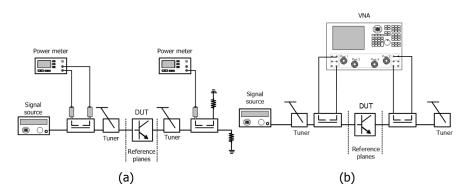

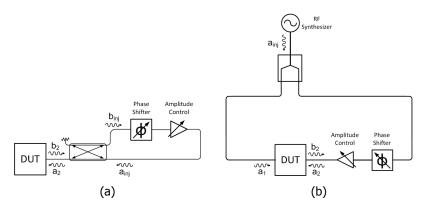

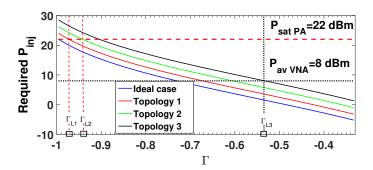

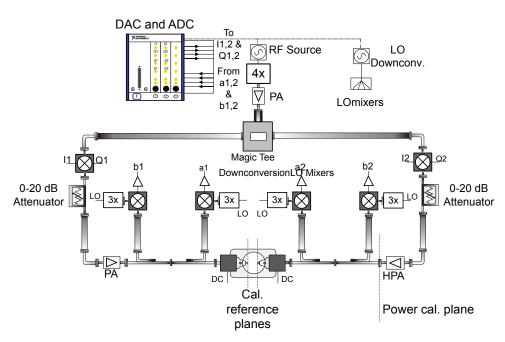

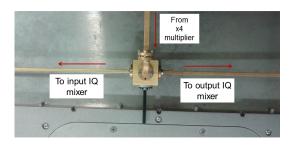

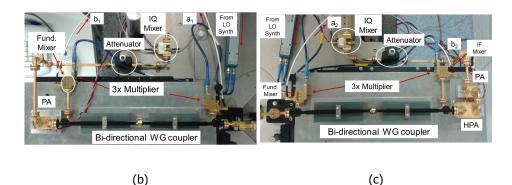

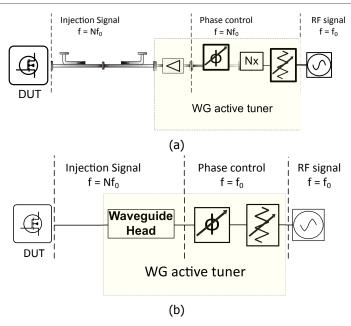

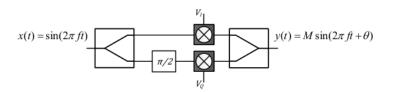

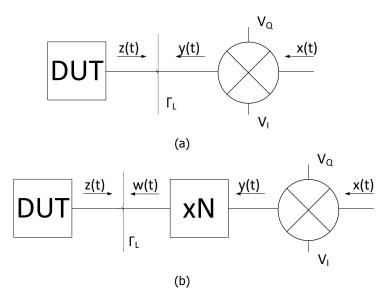

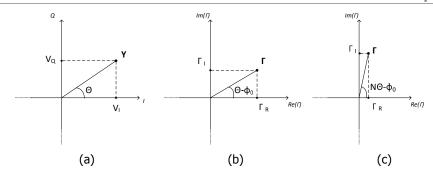

- 2. Connect ports 1 and 2 together to obtain  $e_{22}$  and  $e_{10}e_{32}$ .