**Delft University of Technology**

## A Switched-Capacitor DC-DC Converter Powering an LC Oscillator to Achieve 85% System Peak Power Efficiency and -65 dBc Spurious Tones

Urso, Alessandro; Chen, Yue; Staszewski, Robert Bogdan; Dijkhuis, Johan F.; Stanzione, Stefano; Liu, Yao-Hong; Serdijn, Wouter A.; Babaie, Masoud

**DOI** 10.1109/TCSI.2020.3012106

Publication date

Document Version Accepted author manuscript Published in

IEEE Transactions on Circuits and Systems I: Regular Papers

## Citation (APA)

Urso, A., Chen, Y., Staszewski, R. B., Dijkhuis, J. F., Stanzione, S., Liu, Y.-H., Serdijn, W. A., & Babaie, M. (2020). A Switched-Capacitor DC-DC Converter Powering an LC Oscillator to Achieve 85% System Peak Power Efficiency and -65 dBc Spurious Tones. *IEEE Transactions on Circuits and Systems I: Regular Papers*, *67*(11), 3764-3777. https://doi.org/10.1109/TCSI.2020.3012106

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

#### Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A Switched-Capacitor DC-DC Converter Powering an LC Oscillator to Achieve 85% System Peak Power Efficiency and -65 dBc Spurious Tones

Alessandro Urso<sup>®</sup>, *Student Member, IEEE*, Yue Chen<sup>®</sup>, *Student Member, IEEE*, Robert Bogdan Staszewski<sup>®</sup>, *Fellow, IEEE*, Johan F. Dijkhuis, *Member, IEEE*, Stefano Stanzione<sup>®</sup>, *Member, IEEE*, Yao-Hong Liu<sup>®</sup>, *Senior Member, IEEE*, Wouter A. Serdijn<sup>®</sup>, *Fellow, IEEE*, and Masoud Babaie<sup>®</sup>, *Member, IEEE*

Abstract—In this paper, we propose a new scheme to directly power a 4.9–5.6 GHz LC oscillator from a recursive switched-capacitor DC-DC converter. A finite-state machine is integrated to automatically adjust the conversion ratio and switching frequency of the converter such that its DC output voltage is within  $\pm 5\%$  of the desired 1V across input voltage range 1.3–2.2 V and <2 mA load current conditions. A gate-driver circuit is embedded in each switch of the converter to guarantee constant on-resistance across PVT variations without sacrificing device reliability. Furthermore, a spur reduction block (SRB) is embedded in the oscillator to suppress the ripple induced spurs by stabilizing its tail current. Both the converter and the oscillator are implemented in 40-nm CMOS technology. The measured peak power efficiency of the converter is 87%, while its spot noise is  $<1.5 \,\mathrm{nV}/\sqrt{\mathrm{Hz}}$ , which does not degrade the phase noise of the oscillator. The SRB suppresses the spur to < -65 dBc under the 30 mV<sub>pp</sub> ripple of the converter.

*Index Terms*—Switched-capacitor DC-DC converter, LDO replacement, gate-driver circuit, LC oscillator, spur reduction block, phase noise, voltage controlled oscillator (VCO).

## I. INTRODUCTION

THE Internet-of-Things (IoT) is constantly spanning new applications [1]. IoT devices are mostly powered from energy stored in supercapacitors or batteries. However, their output voltage fluctuates due to the availability of energy sources and the environment in which they are placed. Consequently, a DC-DC buck converter cascaded with a linear

Manuscript received March 14, 2020; revised June 5, 2020 and July 6, 2020; accepted July 20, 2020. This work was supported by the Netherlands Organization for Scientific Research (NWO) under Project 13598 and Project 17303. This article was recommended by Associate Editor Y. Qin. (*Corresponding author: Alessandro Urso.*)

Alessandro Urso, Yue Chen, Wouter A. Serdijn, and Masoud Babaie are with the Microelectronics Department, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: alessandro01.urso@gmail.com).

Robert Bogdan Staszewski was with the Microelectronics Department, Delft University of Technology, 2628 CD Delft, The Netherlands. He is now with the School of Electrical and Electronic Engineering, University College Dublin, Dublin 4, Ireland.

Johan F. Dijkhuis, Stefano Stanzione, and Yao-Hong Liu are with the Holst Centre, imec-NL, 5656 AE Eindhoven, The Netherlands.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2020.3012106

(b)

Fig. 1. System diagram of: (a) conventional cascade of a buck converter with an LDO to power up an oscillator, and (b) proposed solution, which avoids the use of the LDO.

low drop-out (LDO) regulator is customarily used to generate a 'clean' and stable nominal supply voltage of  $\sim 1 \text{ V} V_{\text{DD}}$ to supply nanoscale CMOS circuits and systems, as shown in Fig. 1 (a) [2]–[5]. Note that the intermediate DC-DC converter is invariably required, otherwise the large voltage drop across the LDO would severely degrade the system efficiency when the LDO is directly connected to the storage element.

Full system integration favors switched-capacitor (SC) buck converters over the traditional inductor-based structures [6]. However, SC converters operate at much higher switching frequencies, thus forcing to increase the LDO's bandwidth and its quiescent current [7]. On the other hand, the equivalent input noise of the LDO's error amplifier and its feedback resistors, directly appears at the output and it can only be filtered at frequencies above the output pole [8]. To minimize the LDO noise, the quiescent current of its error amplifier should increase. Moreover, its feedback resistors should be reduced while keeping their ratio constant, which, in turn, increases the current flowing through them. Hence, there exists a trade-off between the LDO's noise and current efficiency. Considering a so-called cap-less LDO (i.e. no external capacitor at the LDO output), a larger value of the power supply rejection (PSR) forces the output non-dominant pole to be

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

further away from the dominant one to ensure the LDO's stability [9]. Hence, the size of the LDO pass transistor must be reduced accordingly, thus increasing the drop-out voltage, leading to the decrease of power efficiency. Therefore, another trade-off exists between the LDO's PSR and power efficiency. The aforementioned trade-offs are even more critical in RF oscillators where the LDO output noise and ripple can easily pollute the oscillator spectral purity.

Since the LDOs are noisy, bulky and inefficient [8], [10]-[12], it would appear beneficial for the IoT circuitry to be connected directly to the buck converter. However, the LDO elimination would impose several challenges on the design of the DC-DC converter and the LC oscillator. First, in face of a wide range of input voltage  $(V_{\rm IN})$  and load current  $(I_L)$  variations, the converter needs to provide a relatively accurate and constant DC voltage  $(1 V \pm 5\%)$  for the oscillator. Second, the converter's noise should be low enough in order not to degrade the inherent phase noise performance of the oscillator. Third, due to the lack of LDO isolation, the converter's ripple is up-converted and appears at the oscillator's output spectrum, degrading its spectral purity. Hence, new techniques should be adapted in the oscillator biasing circuit to reduce its supply pushing factor.

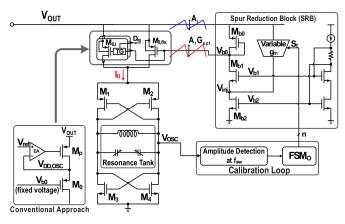

Fig. 1 (b) shows the block diagram of the proposed solution, in which the use of the LDO is avoided, and the DC-DC converter directly powers up the LC oscillator but without degrading its spectral purity. To keep the output voltage of the converter ( $V_{OUT}$ ) relatively constant against  $V_{IN}$  or  $I_L$  variations, a finite state machine (FSM)-based conversion ratio (CR) and switch frequency ( $f_{SW}$ ) modulation is introduced, which also allows having a predictable spectrum of the converter output voltage. To have an almost constant spot noise at  $V_{OUT}$ , a new gate-driver circuit is embedded in all converter's switches to guarantee minimum switch on-resistance across the process variations and the entire input voltage range. Finally, to mitigate the effects of ripples generated by the DC-DC converter, a spur reduction block (SRB) is embedded into the oscillator biasing network to suppress its supply sensitivity.

The paper is organized as follows: Section II derives the requirements on the conversion ratio and introduces a recursive switched-capacitor (RSC) topology along with an analysis of its output resistance and losses and a FSM-based digital control. A novel gate-driver circuit to drive the switches is proposed in Section III. In Section IV, the noise level required by  $V_{OUT}$  is derived such that it will not affect the inherent spectral purity of the oscillator. Based on the converter ripple, the required supply pushing of the oscillator is derived in Section V, and a spur reduction block based on our previous published LC oscillator [13] is presented. Section VI presents the measurement results as well as a comparison with the state of the art.

#### II. DC-DC CONVERTER DESIGN

In this section, the required conversion ratio (CR) range and resolution are derived. A converter topology that meets the CR requirement is then presented along with its output

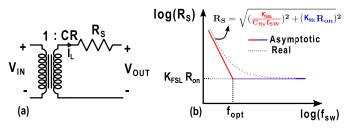

Fig. 2. (a) Equivalent model of an SC DC-DC converter; and (b) its equivalent output resistance versus switching frequency.

resistance analysis. To continuously adjust the CR, a digital FSM-based control is introduced. Finally, the losses of the resulting converter topology are analyzed, to determine the optimal switch sizes.

#### A. Requirements on Conversion Ratio Range and Resolution

Fig. 2(a) shows the equivalent model of an SC DC-DC converter. Its output voltage can be written as

$$V_{\rm OUT} = V_{\rm IN} \cdot {\rm CR} - R_S \cdot I_L, \tag{1}$$

where  $R_S$  is the equivalent output resistance of the converter and  $I_L$  is the load current. During the operation, the CR and/or  $R_S$  must be adaptively adjusted for  $V_{\rm IN}$  and  $I_L$ variations to keep the output voltage within the  $\pm 5\%$  of the oscillator nominal supply voltage (i.e.,  $V_{\rm OUT} = 1$ V).  $R_S$  can be modulated through the switching frequency ( $f_{\rm SW}$ ) or the converter capacitance ( $C_{\rm fly}$ ). However, the former requires to modulate  $f_{SW}$  by several orders of magnitude [14]–[17], making it difficult for the oscillator to keep the spur level low enough over the entire  $f_{\rm SW}$  range. The latter involves a significant reduction of  $C_{\rm fly}$  [18], [19], resulting in larger ripples, further worsening the oscillator spurs. Consequently, in this design, we *mainly* modulate the conversion ratio to simplify the converter control but still to obtain a predictable  $f_{SW}$ , facilitating its direct connection to the oscillator.

With the aid of Eq. (1), and considering the targeted  $V_{OUT}$  accuracy (i.e.,  $\pm 5\%$ ), and  $V_{IN}$  and  $I_L$  ranges, one can easily calculate the lowest and the highest CR by

$$\begin{cases} CR_{\min} = \frac{0.95V_{OUT} + R_S I_{L,\min}}{V_{IN,\max}} \\ CR_{\max} = \frac{1.05V_{OUT} + R_S I_{L,\max}}{V_{IN,\min}}. \end{cases}$$

(2)

On the other hand, at a constant input voltage, the difference between the output voltage corresponding to two consecutive CRs should be finer than the targeted  $V_{OUT}$  accuracy. Consequently,

$$V_{OUT,i+1} - V_{OUT,i} < 0.1 V_{OUT}.$$

(3)

Considering the worst case scenario ( $V_{IN} = V_{IN,max}$ ,  $I_L = I_{L,min}$ ), Eq. (3) can be written as

$$V_{IN,max}(CR_{,i+1} - CR_i) - (R_{S_{i+1}} - R_{S_i})I_{L,min} < 0.1V_{OUT}.$$

(4)

Assuming a constant  $R_S$ , the required CR resolution can be estimated by

$$CR_{res} = (CR_{i+1} - CR_i) < \frac{0.1V_{OUT}}{V_{IN,max}}.$$

(5)

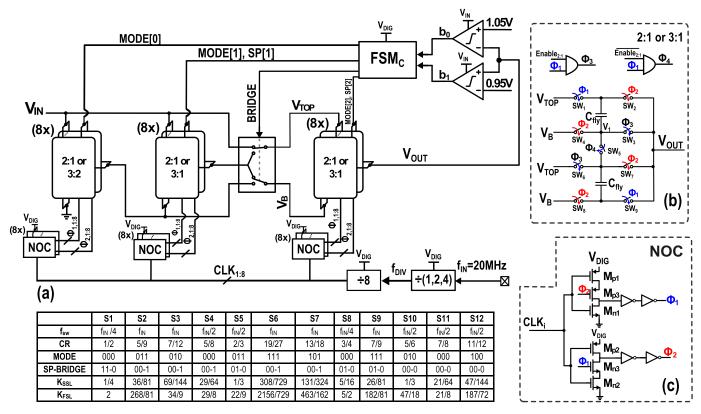

Fig. 3. (a) Detailed block diagram of the three-stage recursive switched capacitor (RSC) DC-DC converter with a table showing the control signals for all the converter states; (b) detailed representation of a 2:1 or 3:1 stage and (c) the non-overlapping clock (NOC) generator.

Eq. (5) indicates that the CR resolution should be improved if a larger input voltage or a finer  $V_{OUT}$  accuracy is targeted. This increases the total number of CRs, which, in turn, adversely impacts on the complexity of the converter and its power efficiency.

With  $R_S$  of  $50 \Omega$ ,  $1.3 V < V_{IN} < 2.2 V$ , and  $0.5 \text{ mA} < I_L < 2 \text{ mA}$ , the resulting CR varies from 0.5 to 0.9 with a resolution of 0.045. Considering the side effects of the converter ripple, the number of CRs has been increased from 9 to 12.

## B. Topology Definition

Several SC topologies have already been published in literature that could meet the CR range and resolution requirements discussed above. In particular, a Successive Approximation Register (SAR) SC converter presented in [20] offers a resolution of  $V_{IN}/2^N$  (where N is the number of stages), but it suffers from a limited power density as a flying capacitance of 2.24 nF is required to deliver a current < 0.3 mA. An asymmetric shunt SC converter was presented in [21] that increases the number of CRs even further but at a cost of increasing the losses in the slow switching limit (SSL) region. A recursive switched-capacitor (RSC), introduced in [14], offers the same resolution as the SAR but with a lower SSL loss for the same number of stages. However, to achieve our required resolution, it would require *five* 2:1 stages, thus degrading the converter's output impedance and efficiency.

To cover the required CRs, while minimizing the SSL losses and avoiding cascading many RSC stages as in [14],

we propose a 3-stage RSC topology but with two CR options (2:1, 3:2 or 3:1) per each stage. The implemented three-stage RSC converter is shown in Fig. 3. Since  $CR_{min}$  is about 0.5, the first stage does not need the 3:1 configuration and its output should always be connected to the bottom voltage of the second stage, thereby allowing for a higher CR. The second and third stages operates only in the 2:1 and 3:1 modes with one set of bridge switches placed between them. This allows connecting the output of the second stage to either the top or the bottom voltage of the third stage.

Each stage of the converter is divided into eight smaller interleaved units. This allows to avoid the need for an output capacitor and to reduce the switching losses of the converter [22]. Moreover, each unit embeds the non-overlapping clock (NOC) circuit. The clock  $f_{IN} = 20$  MHz is provided externally, while the frequency division (of 1, 2 or 4) to generate  $f_{DIV}$  is implemented internally by means of a flipflop-based frequency divider. Then, the eight interleaved clock phases ( $CLK_{1:8}$ ) are generated by further dividing  $f_{DIV}$  [23]. The NOC embedded in each unit generates the two non-overlapped phases ( $\Phi_1$  and  $\Phi_2$ ).

#### C. Charge Flow and Impedance Analysis

To always guarantee  $V_{OUT} = 1 \text{ V} \pm 5\%$ , while  $V_{IN} \in \{1.3 - 2.2\} \text{ V}$ , the stages of the RSC converter are rearranged in a series/parallel configuration. This has an impact on the charge flow of each stage, and therefore, the output impedance of the converter.

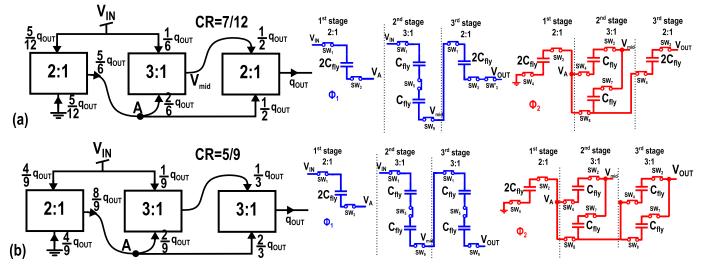

Fig. 4. Charge flow through the inter-stage connections for a conversion ratio of: (a) 7/12, and (b) 5/9, along with the their equivalent circuits for 1 of the 8 units during  $\Phi_1$  and  $\Phi_2$ .

Figs. 4 (a) and (b) illustrate two configurations which realize CRs of 7/12 and 5/9, along with their equivalent circuits for 1 of the 8 units. Please notice that node  $V_A$  during  $\Phi_1$  ( $V_{mid}$  during  $\Phi_2$ ) is not floating as it is connected to the other four units operating in the opposite phase.

In Fig. 4 (a), the last stage loads half of the output charge  $q_{OUT}$  from the second stage. Given that the second stage has a CR of 3:1 ( $V_{mid} = \frac{V_{IN} + 2V_A}{3}$ ), the charge taken from the node A ( $\frac{2}{6}q_{OUT}$ ) is twice that from  $V_{IN}$  ( $\frac{1}{6}q_{OUT}$ ). Applying KCL at node A, the charge delivered by the first stage is found to be  $\frac{5}{6}q_{OUT}$ , and it is equally divided between its top and bottom voltages ( $V_A = \frac{V_{IN}}{2}$ ). Fig. 4(b) shows a similar example of charge flow for CR = 5/9.

In the conventional RSC topology with only 2:1 stages, irrespective of the converter configuration, the output current of each stage is a binary-weighted fraction of the load current (i.e.,  $I_L/2^{N-i}$ ), thus the switches and capacitors are sized based on the current flowing through them. However, in our topology, the charge flow of each stage depends on the particular configuration, as shown in the two previous examples. Hence, in our design, all the stages are sized identically.

The equivalent output impedance of the converter,  $R_S$ , can be modeled by the well-known equation reported below [24]:

$$R_{S} = \sqrt{R_{SSL}^{2} + R_{FSL}^{2}} = \sqrt{\left(\frac{K_{SSL}}{C_{fly}f_{SW}}\right)^{2} + \left(K_{FSL}R_{on}\right)^{2}}.$$

(6)

$R_{SSL}$  and  $R_{FSL}$  are the resistances in the slow and fast switching limit (SSL, and FSL), respectively.  $K_{SSL}$  and  $K_{FSL}$ are topology-dependent coefficients valid respectively in the SSL and FSL regions [24]. Fig. 2(b) shows a sketch of Eq (6) versus the switching frequency. In the SSL region, the charge-sharing mechanism dominates the losses, whereas, in the FSL region, the finite on-resistance of the switches is the main source of inefficiency.

To compute  $R_{SSL}$  and  $R_{FSL}$ , one can use the charge multiplier vectors  $\mathbf{a_c}$  and  $\mathbf{a_s}$  which can be directly computed from the charge flow analysis and represent the charge flowing

through each capacitor and each switch, respectively [6], [14], [21], [24]. Assuming that all the switches have the same  $R_{on}$ , the resistances in the slow and fast switching limits can be written as

$$R_{SSL} = \sum_{i=1}^{N} \frac{\mathbf{a}_{c,i}^2}{f_{SW}C_i},\tag{7}$$

and

$$R_{FSL} = \sum_{i=1}^{N} \sum_{j=1}^{switches} 2\mathbf{a}_{\mathbf{s},\mathbf{i},\mathbf{j}}^{2} R_{on}, \qquad (8)$$

where the summation over *i* accounts for the number of stages N, while the summation over *j* accounts for the number of switches in each stage.  $C_i$  is the flying capacitance of  $i^{th}$  stage. In the example shown in Fig. 4 (a), the charge multiplier vectors are

$$\mathbf{a_{c}} = \begin{bmatrix} \frac{5}{12} & \frac{1}{6} & \frac{1}{6} & \frac{1}{2} \end{bmatrix}$$

$$\mathbf{a_{s,i}} = \begin{bmatrix} \frac{5}{12} & \frac{1}{6} & \frac{1}{2} \end{bmatrix}^{T}, \tag{9}$$

while for the example shown in Fig. 4(b) the charge multiplier vectors are

$$\mathbf{a_{c}} = \begin{bmatrix} \frac{4}{9} & \frac{1}{9} & \frac{1}{9} & \frac{1}{3} & \frac{1}{3} \\ \mathbf{a_{s,i}} = \begin{bmatrix} \frac{4}{9} & \frac{1}{9} & \frac{1}{3} \end{bmatrix}^{T}.$$

(10)

When a stage is used in the 3:1 or 3:2 configuration, two flying capacitors and seven switches are operated, leading to two identical elements in the vector  $\mathbf{a_c}$ .

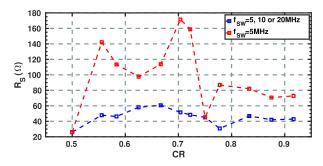

With the aid of the charge multiplier vectors and Eqs. (7)–(8), the output resistance of the proposed converter versus CR is calculated at  $f_{SW} = 5$  MHz and depicted in Fig. 5. As can be gathered from the red line,  $R_S$  greatly varies with the particular configuration used, dramatically affecting the converter efficiency. Moreover, even with a constant load current, moving towards a higher CR might lead to a lower output voltage due to the  $R_S$  increase. It is therefore

URSO et al.: SWITCHED-CAPACITOR DC-DC CONVERTER POWERING AN LC OSCILLATOR

Fig. 5. Calculated output resistance of the converter with fixed (red) and adaptive (blue) switching frequency.

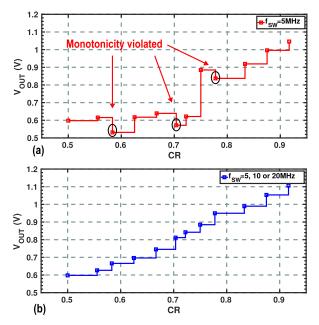

Fig. 6. Output voltage of the converter versus CR with (a) fixed and (b) adaptive switching frequency, when  $V_{IN} = V_{IN}^{min}$ ,  $I_L = I_L^{max}$ .

necessary to guarantee the monotonicity of the output voltage as a function of CR. This condition can be modeled by the following equation

$$V_{OUT,i+1} - V_{OUT,i} > 0, \quad \forall i \in \{CRs\}.$$

$$(11)$$

Considering the worst-case scenario for the monotonicity  $(V_{IN} = V_{IN,min}, I_L = I_{L,max})$ , Eq. (11), can be rewritten as

$$V_{IN,min}(CR_{i+1} - CR_i) - (R_{S_{i+1}} - R_{S_i})I_{L,max} > 0.$$

(12)

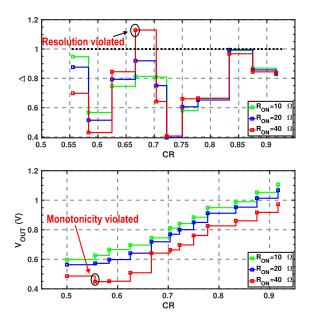

Fig. 6 (a) plots  $V_{OUT}$  for different CRs with  $V_{IN} = V_{IN,min}$ and  $f_{SW} = 5$  MHz.  $V_{OUT}$  should always increase when moving from one CR to the next higher one. However, for CR of  $\frac{7}{12}$ ,  $\frac{19}{27}$  and  $\frac{7}{9}$ ,  $V_{OUT}$  decreases, proving that in those two configurations the monotonicity condition is violated.

On the other hand, large  $R_S$  variations can also violate the resolution requirement imposed by Eq. (4). To better investigate the resolution requirement, a parameter  $\Delta$  is introduced and defined as the voltage difference of the output voltages corresponding to two consecutive CRs normalized to the resolution. Hence,  $\Delta$  can be written as

$$\Delta = \frac{V_{OUT,i+1} - V_{OUT,i}}{0.1 V_{OUT}}.$$

(13)

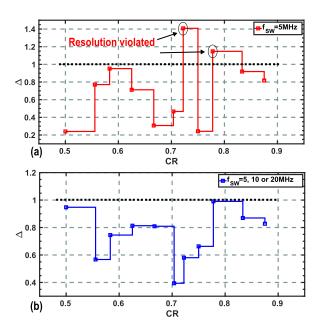

Fig. 7. Calculated resolution of the converter in the worst-case scenario  $(V_{IN} = V_{IN}^{max}, I_L = I_L^{min})$  for (a) fixed, and (b) adaptive switching frequency.

Fig. 7 (a) plots the parameter  $\Delta$  versus CRs for a fixed  $f_{SW} = 5$  MHz. As can be seen, at CR  $= \frac{13}{18}$  and  $\frac{7}{9}$ ,  $\Delta > 1$ , thereby violating the resolution requirement.

To overcome the above mentioned problems, the switching frequency in the configurations with a higher  $R_S$  can be modulated by a factor of  $2 \times$  or  $4 \times$ , resulting in the resolution and monotonicity conditions being always met (see Figs. 7(b) and 6(b)). Moreover, Fig. 5 shows that by adapting  $f_{SW}$  to the particular configuration, the output resistance of the RSC converter can be kept fairly constant, thereby maximizing the power efficiency.

Finally, as a general design guide, Eqs. (4) and (12) can be combined into Eq. (14), which provides a compact expression for the two main requirements of SC converters, namely resolution and monotonicity.

$$\begin{cases} V_{IN,max}(CR_{i+1} - CR_i) - (R_{S_{i+1}} - R_{S_i}) \\ I_{L,min} < 0.1 V_{OUT} \\ V_{IN,min}(CR_{i+1} - CR_i) - (R_{S_{i+1}} - R_{S_i}) \\ I_{L,max} > 0. \end{cases}$$

(14)

## D. FSM-Based Digital Control

During the operation,  $V_{OUT}$  is compared with two reference levels, 0.95 V and 1.05 V, at a rate of 1 MHz. Two bits (b<sub>0,1</sub>) are generated to indicate whether  $V_{OUT}$  is within the range, higher or lower. The converter's FSM (FSM<sub>C</sub>) then decides to keep the same state or move to the next higher/lower one. Each state has a unique set of control signals (MODE, SP, BRIDGE), which determines  $f_{SW}$ , the series or parallel connection of stages, and the CR of each stage. The table in Fig. 3(b) reports all the converter's states and their control signals.

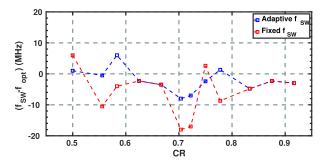

Fig. 8. Difference between the frequency at which the converter is operated and the optimum one in case of fixed and adaptive switching frequencies.

#### E. Steady-State Loss Analysis

SC DC-DC converters suffer from several losses that impact their power efficiency. The two main sources of such losses are due to the dynamic operation of the switches (switching losses) and due to the output resistance of the converter (conduction losses). Those two contributions can be modeled with the following equation:

$$P_{LOSS} = nC_g V_{sw}^2 f_{SW} + R_S I_L^2, \tag{15}$$

where *n* is the number of switches operating at  $f_{SW}$  with a clock voltage swing of  $V_{sw}$ , and  $C_g$  is the equivalent gate capacitance of each switch. To maximize the power efficiency, it is required that the converter operates at the boundary between the fast and slow switching limits. Hence, the contribution of the two resistances in the two regions should be the same (i.e.,  $R_{SSL} = R_{FSL}$ ), with the optimal  $f_{SW}$  being equal to

$$f_{SW} = f_{opt} = \frac{\sum_{i=1}^{N} \frac{\mathbf{a}_{c,i}^2}{C_i}}{R_{FSL}} = \frac{\rho}{R_{FSL}}.$$

(16)

Fig. 8 (a) shows the difference between the frequency at which the converter is operated and  $f_{opt}$ . By modulating the switching frequency by only a factor of  $2 \times$  or  $4 \times$ , the DC-DC converter can be operated relatively close to its optimal  $f_{SW}$ .

By substituting Eq. (16) into Eq. (15), the power loss can be written as

$$P_{LOSS} = \frac{n \cdot C_g \cdot V_{sw}^2 \cdot \rho}{K_{FSL} R_{on}} + \sqrt{2} K_{FSL} R_{on} (I_{L,max})^2.$$

(17)

As can be gathered from Eq. (17), the power loss depends on the particular configuration of the converter  $(n, K_{SSL}, K_{FSL})$ and the switch width  $(C_g, R_{on})$ . By introducing the capacitance and on-resistance of a unit-width transistor as  $\overline{C_g} = \frac{C_g}{W}$  and  $\overline{r_{on}} = R_{on}W$ , Eq. (17) can be rewritten as

$$P_{LOSS} = \frac{n \cdot \overline{C_g} \ V_{SW}^2 \ W^2 \ \cdot \rho}{K_{FSL} \overline{r_{on}}} + \sqrt{2} \ \overline{\frac{r_{on}}{W}} \ K_{FSL} \Big( I_{L,max} \Big)^2.$$

(18)

The optimal switch width  $(W_{opt})$  can be found by minimizing Eq. (18) with respect to W, leading to

$$W_{opt} = \left(\frac{\sqrt{2}K_{FSL}^2 \overline{r_{on}^2} \left(I_{L,max}\right)^2}{2n\overline{C_g}\rho V_{SW}^2}\right)^{\frac{1}{3}}.$$

(19)

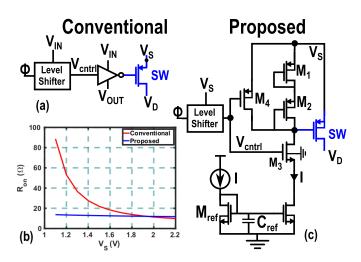

Fig. 9. (a) Schematic of a conventional gate-driver circuit, with (b) the equivalent series resistance versus the supply voltage, and (c) the proposed gate driver circuit, resulting in a constant  $R_{on}$ .

Using thin-oxide, minimum channel-length transistors,  $\overline{r_{on}}$  and  $\overline{C_g}$  equal  $1 \cdot 10^3 \Omega \cdot \mu m$  and  $1 \cdot 10^{-15} \frac{\text{F}}{\mu \text{m}}$ , respectively. After the circuit optimization, the implemented switch width was chosen to be  $W = 130 \,\mu \text{m}$ .

## **III. GATE-DRIVER DESIGN**

In this section, a new gate-driver circuit is introduced, which offers constant on-resistance across PVT variations without compromising the reliability of the whole converter.

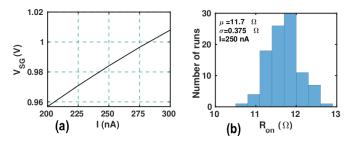

In nanometer CMOS technology, the breakdown voltage of a thin-oxide device is well below the maximum input voltage of the converter. To resolve this issue, prior arts apply different supply rails (e.g.,  $V_S$  and  $V_S/2$  in Fig. 9(a)) as the high and low voltage levels for driving the switch gates. However, as  $V_{IN}$  (i.e.,  $V_S$ ) decreases, the gate-source voltage,  $|V_{GS}|$ , of the switches approaches  $|V_{th}|$ , leading to an exponential increase in their on-resistance, significantly increasing  $R_{FSL}$ , as depicted in Fig. 9(b). This impacts the converter power efficiency, the monotonicity and the resolution conditions. To further investigate it, Fig. 10 plots  $\Delta$  and  $V_{OUT}$  versus CR for different  $R_{on}$ . When  $R_{on} \ge 40 \Omega$ , changing CR from 0.5 to 0.55 (moving from S1 to S2 in the table of Fig. 3) reduces the output voltage, thereby violating the converter's monotonicity condition. Similarly, the resolution when moving from S4 to S5 is greater than the required output voltage accuracy, thereby violating Eq. (5).

To resolve the aforementioned issues, we propose a gate-driver circuit [25], as shown in Fig. 9(b). When the control voltage  $V_{cntrl}$  for the switch SW is high, the bias current I flows through two cascaded diode-connected transistors,  $M_{1,2}$ , to generate the desired  $|V_{GS}|$  (e.g.,  $\sim 1 V$ ) for the switch.  $M_{1,2}$  are minimum-width but long-length devices to achieve a higher resistance, minimizing the bias current and avoiding the efficiency degradation. However, when  $V_{cntrl}$  goes 0 to turn off the switch, the time constant associated with the discharging process of the gate-to-source capacitance of the switch is high due to this large resistance, slowing down the discharging process. Consequently,  $M_4$  is added to provide a low-impedance path for speeding up the discharging

Fig. 10. Resolution and monotonicity conditions versus CR for different values of  $R_{on}$ .

Fig. 11. (a)  $V_{SG}$  of the switch SW when a biasing current variation of  $\pm 30\%$  is applied; (b) Monte Carlo simulation of its  $R_{on}$ .

procedure.  $M_{3,4}$  are thick-oxide devices, thus contributing to an increase in the dynamic losses. However, their size is much smaller than that of the switch, leading to a negligible power-efficiency degradation. In the proposed circuit,  $M_{1,2}$  and switch SW are of the same type. Hence, their  $V_{th}$  changes in the same direction with PVT variations, leading to an almost constant  $|V_{GS}| - |V_{th}|$  and ON-resistance of the channel. This has been verified by means of a Monte Carlo simulation with 100 samples, as shown in Fig. 11(b). Moreover, by providing a constant overdrive voltage to all the switches, the switching losses of the converter merely depend on the number of switches being operated.

To properly drive the gates of  $M_{3,4}$ , a level shifter (LS) is required since the clock signal  $\Phi$  is in the low-voltage domain. However, the LS only drives  $M_{3,4}$ , which are much smaller than the main switch SW. In the worst-case scenario, the LS output swings from 0 to  $V_{IN} = V_{INmax} = 2.2$  V, while consuming ~ 104 nW. There is a total of 240 switches, of which, in the worst-case scenario (State S6), only 168 are operated simultaneously with a 50% duty-cycle, leading to a power overhead of 17.5  $\mu$ W, which is negligible when compared to the delivered output power. Moreover, the non-overlapping condition after the LS is still guaranteed, as its propagation delay (hundreds of ps) is much smaller than the non-overlapping time (several ns).

#### A. Practical Design Considerations

The transistor type, its terminals connections, and especially the body-diode direction of the converter's main switches are of relevant interest to the designer. In this design, the body and source terminals of a PMOS switch are connected, as shown in in Fig. 9 (c). Therefore, to guarantee that the body-diode is always reverse biased, the potential of the source terminal,  $V_S$ , must always be higher than the drain voltage,  $V_D$ . However, when either the second or third stage works in the 3:1 mode, the use of a single PMOS switch as SW3 in Fig. 3 (b) cannot satisfy this requirement. To resolve that, SW3 comprises here two cascaded PMOS switches whose drain terminals are connected. This ensures that when the stage operates in the 3:1 mode, at least one of the two switches is always off. Moreover, both switches follow  $\Phi_1$  during the 2:1 mode.

With the conventional gate-driver circuit (see Fig. 9 (a)), the switches in each converter's stage operate in different voltage domains. Therefore, it becomes challenging to guarantee the non-overlapping condition between two clock phases over the entire input voltage range, potentially affecting the functionality and performance of the converter. With the proposed gate-driver circuit, the realization of the non-overlapping clocks is simplified as all switches operate in the same voltage domain and are powered by the stable output voltage of the converter ( $V_{OUT} = 1$  V). The non-overlapping clock generator circuit is shown in Fig. 3(c). By adding transistors  $M_{n3}$  and  $M_{p3}$ , each phase of the clock can change state only when the other phase has already altered, thus guaranteeing the non-overlapping condition.

## **IV. NOISE REQUIREMENTS**

In this section, the requirement on the power supply noise is first derived; then the main noise sources of the DC-DC converter are analyzed and discussed.

## A. Supply Noise Requirements

The voltage noise on the power supply can significantly degrade the oscillator's spectral purity [26]. In this subsection, the noise requirements of the DC-DC converter are derived such that it will not significantly affect the oscillator performance. The inherent phase noise of LC oscillator can be calculated by [27]:

$$\mathcal{L}(\Delta f) = 10 \log_{10} \left( \frac{kT(1+\gamma)}{2Q^2 P_{DC} \alpha_I \alpha_V} \left( \frac{f_0}{\Delta f} \right)^2 \right), \qquad (20)$$

where k is the Boltzman' constant, T is the absolute temperature expressed in Kelvin,  $\gamma$  is the excess noise factor of the transistors, Q is the tank quality factor, and  $P_{DC}$  is the oscillator power consumption.  $\alpha_I$  is the current efficiency, defined as a ratio of the magnitude of the fundamental current harmonic over the oscillator DC current, and  $\alpha_V$  is a voltage efficiency, defined as the ratio of the oscillation amplitude over the oscillator power supply.  $f_0$  and  $\Delta f$  are the carrier and offset frequencies with respect to the main tone, respectively.

On the other hand, the phase noise induced by the noise on the power supply can be estimated as

$$\mathcal{L}_{sup}(\Delta f) = 10 \log_{10} \left( \frac{K_V^2}{\Delta f^2} V_{n,supply}^2(\Delta f) \right)$$

(21)

where  $V_{n,supply}^2(\Delta f)$  is the power spectral density (PSD) of the supply noise and  $K_V$  is the supply pushing factor of the oscillator. To avoid degradation of the inherent PN of the oscillator, it is required that  $\mathcal{L}_{sup}(\Delta f) \ll \mathcal{L}(\Delta f)$ , leading to

$$V_{n,supply}^2 \ll kT(1+\gamma)2Q^2 P_{DC}\alpha_I \alpha_V \left(\frac{f_0}{K_V}\right)^2.$$

(22)

Assuming  $P_{DC} = 1 \text{ mW}$ ,  $K_V = 40 \text{ MHz/V}$ ,  $\gamma = \frac{2}{3}$ ,  $f_0 = 5 \text{ GHz}$ ,  $\alpha_I = \frac{4}{\pi}$ ,  $\alpha_V = 0.5$ , Q = 10 for a complementary oscillator, the maximum supply noise should be  $< 23 \text{ nV}/\sqrt{\text{Hz}}$ . Note that oscillators with better phase noise (i.e., higher Q or  $P_{DC}$ ) impose even more stringent noise requirements on their supply voltage.<sup>1</sup>

Note that the reported spot noise of LDOs with high current efficiency (i.e., > 90%) is much higher than the supply noise tolerated by the oscillator [11], [12], [28], [29]. To reduce the output noise of the LDO, its quiescent current should be increased, which leads to a severe current efficiency degradation (e.g., 70% in [30]) or an external filtering capacitor must be used [8].

#### B. Noise Analysis of the DC-DC Converter

The three main noise sources of the proposed converter are the transistors in the current mirror of the gate driver circuit, the two comparators and the on-resistance of the switches of the DC-DC converter.

Transistor  $M_{\text{ref}}$  in Fig. 9 generates current noise  $I_n$  that is mirrored at the source terminal of  $M_3$  and modulates the gate-to-source voltage of the main switch, thereby modulating its on-resistance. Its noise contribution can be filtered by the capacitor  $C_{ref}$  when

$$Z_{C_{\rm ref}} \ll \frac{1}{g_{\rm m,ref}}.$$

(23)

Hence, the minimum value of  $C_{ref}$  should be

$$C_{ref} \gg \frac{I}{f\pi(V_{GS} - V_{th})}.$$

(24)

To filter the noise at frequencies above f = 10 kHz,  $C_{ref} \approx 100 \text{ pF}$  is required, which is negligible when compared to the total on-chip flying capacitance.

The comparators' outputs directly drive the  $FSM_C$ . Hence, when the  $FSM_C$  does not change state, the gain from the output of the comparators to the converter's output is zero, resulting in a null noise contribution of the comparators.

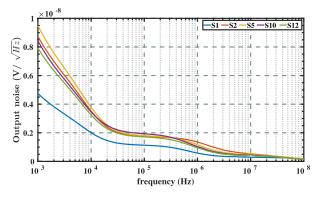

The SC converter acts as an *RC* circuit from a noise point of view. Consequently, its integrated output noise is  $\propto kT/C_{fly}$ , whereas its spot noise is  $\propto R_{on}$ . By employing the gate driver proposed in the previous section, the noise spectral density of the proposed converter is more predictable and well-behaved against PVT. Fig. 12 shows the simulated output noise in different converter states. At lower frequencies (f < 10 kHz), the output noise is dominated by the flicker noise component of  $M_{ref}$ . As the frequency increases, its noise contribution is filtered by the capacitor  $C_{ref}$ , while the total output noise is dominated by the thermal noise of the switches' on-resistance.

<sup>1</sup>For example, with a Q = 15,  $V_{n,supply} < 15 \,\text{nV}/\sqrt{\text{Hz}}$

Fig. 12. Output noise of the DC-DC converter when operated in different configurations.

It is worth mentioning that, contrary to the LDO approach, such low noise is achieved without consuming any additional current or using any external components.

## V. RIPPLE REQUIREMENTS

The voltage ripple on the DC-DC converter's output is up-converted and appears at the oscillator's output spectrum, degrading its spectral purity. In this section, the requirements on the supply sensitivity of the oscillator are firstly derived, followed by discussion on the implementation of the spur reduction block (SRB) in the oscillator.

#### A. Oscillator's Supply Pushing Factor

A sinusoidal ripple on the supply voltage of the oscillator (with a peak-to-peak amplitude  $V_m$ ) induces spurious tones around the carrier, whose amplitude ( $S_{spur}$ ) with respect to the carrier can be calculated by

$$S_{\rm spur} = 10 \, \log_{10} \left( \frac{K_V V_m}{4 f_{SW}} \right)^2 dBc.$$

(25)

The peak-to-peak amplitude of the SC DC-DC converter's ripple can be expressed as

$$V_{rip} = \frac{I_L^{max}}{C_{\rm fly} f_{SW}}.$$

(26)

Eq. (25) can be rewritten into Eq. (27) which highlights the maximum  $K_V$  that the oscillator should have to meet certain spectral requirements.

$$K_V < \frac{4f_{SW}^2 C_{\rm fly}}{I_{L,max}} \cdot 10^{\left(S_{\rm spur}\right)/20}.$$

(27)

For  $S_{\text{spur}} = -65$  dBc,  $f_{SW} = 20$  MHz,  $C_{fly} = 2.7$  nF and  $I_{L,max} = 2$  mA, the maximum supply pushing of the oscillator is  $K_V = 2.4$  MHz/V.

Typically, oscillators have a much higher supply pushing factor ( $K_V \approx 100 \text{ MHz}/V$  for class-D oscillator [31] and  $K_V \approx 18 \text{ MHz}/V$  for class-F oscillator [32]). To solve this issue, we previously presented an LC oscillator which brings the supply pushing factor to as low as  $K_V \approx 100 \text{ KHz}/V$  [13]. The next subsection describes the SRB circuit in more detail.

URSO et al.: SWITCHED-CAPACITOR DC-DC CONVERTER POWERING AN LC OSCILLATOR

Fig. 13. Detailed implementation of the oscillator with the spur reduction block (SRB) based on [13].

#### B. Spur Reduction Block

When an LDO is used to stabilize the oscillator supply in the conventional approach, the tail transistor  $M_0$ , biased by a fixed voltage, is cascaded with the pass transistor of the LDO,  $M_p$ , to adjust the oscillator current,  $I_0$  (see Fig. 13). By removing the LDO, the voltage headroom consumed by  $M_p$  is avoided, improving the system efficiency. At the same time,  $M_0$  consists of a bank of unit transistors  $M_{0,i}$ , each of which could be switched on separately by a transmission gate (TG in Fig.13) to set the desired DC level of  $I_0$ . As shown in [13],  $I_0$ , and the corresponding oscillation amplitude  $V_{osc}$ , should be stabilized to reduce the oscillator's supply pushing, since the variation of the oscillation frequency mainly stems from the variation of the equivalent value of the voltage-dependent parasitic capacitance of the core transistors. To accomplish this, the supply ripple is replicated on the gate terminal of  $M_0$  through the SRB. To account for the finite output resistance of  $M_0$ , the gain of the replica is properly tuned by varying the control code of the variable  $g_m$  stage. The optimal code is automatically found with the on-chip calibration loop that sweeps the control code using an FSM (FSM<sub>O</sub>). For each control code setting, the amplitude detector estimates the variation of the oscillation amplitude at  $f_{SW}$ . When this variation reaches its minimum, the code is deemed optimal and fixed by FSM<sub>0</sub>. Note that the calibration is only performed in one of the converter states and used during the entire operation.

Considering the SRB's finite bandwidth, a phase shift between the supply ripple and its replica at high ripple frequencies would result in residue variations of  $I_0$ , degrading the spur levels. The capacitive load at  $V_{b0}$  and the SRB current are optimized based on the highest  $f_{SW}$  of the converter (20 MHz). At lower  $f_{SW}$ , the oscillator inherently suffers from a lower spur suppression due to a higher tank impedance, requiring tighter  $I_0$  variations. Thus, the SRB gain resolution is designed for the lowest  $f_{SW}$  (5 MHz) to guarantee a low enough spur over the  $f_{SW}$  range. The SRB is effective as long as  $M_0$  stays in the saturation region. Thanks to the CR adjustment of the converter, the DC level of the oscillator supply only varies by  $\pm 50$  mV, which is low enough to keep  $M_0$  safely in saturation. Since the SRB is fully integrated into the oscillator biasing network, only the noise of its extra variable  $g_m$  stage degrades

Fig. 14. Die micrographs of the DC-DC converter (left), the oscillator (right), and photo highlighting their direct connection (middle).

the oscillator phase noise (PN) by a negligible amount (i.e.,  $\sim 0.06 \,\text{dB}$ ). Moreover, the current consumed by the SRB is only 20  $\mu$ A, which leads to a current efficiency degradation of 98%. A more detailed description of the SRB circuit can be found in [13].

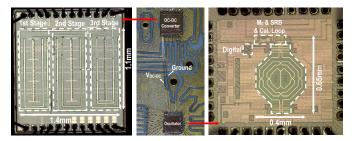

#### VI. EXPERIMENTAL RESULTS

The proposed DC-DC converter and the oscillator are fabricated in the same standard 40-nm CMOS process. Their chip micrographs, as well as a photo highlighting the direct connection of the converter's output to the oscillator supply rail, are shown in Fig. 14. They occupy an active area of  $1.54 \text{ mm}^2$  and  $0.23 \text{ mm}^2$ , respectively. The total on-chip capacitance of the DC-DC converter  $C_{\text{fly}} = 2.7 \text{ nF}$  is equally divided among the three stages, as discussed in Section II.B.

#### A. DC-DC Converter Measurements

Fig. 15 (a) shows the line regulation of the converter for  $I_L = 1 \text{ mA}$  along with the state of the FSM<sub>C</sub>. Figures 15 (b) and (c) show that as  $V_{\text{IN}}$  decreases (or increases), both CR and  $f_{SW}$  change accordingly to keep  $V_{OUT}$  within the desired range.

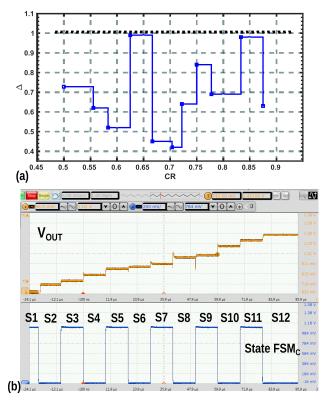

Fig. 16(a) shows that the parameter  $\Delta$ , as defined in Section II.C, in the worst-case scenario ( $V_{IN} = V_{INmax} =$ 2.2 V and  $I_L = I_{Lmin} = 0.5$  mA) is always lower than 1, proving that the first condition imposed by Eq.(14) is met. Fig. 16(b) illustrates the output voltage of the converter (orange line) and the signal (blue line) that changes the state of FSM<sub>C</sub>. As CR rises,  $V_{OUT}$  increases monotonically, proving that, in the worst-case scenario for the monotonicity ( $V_{IN} = V_{INmin} = 1.3$  V and  $I_L = I_{Lmax} = 2$  mA), the second condition imposed by Eq.(14) is also met.

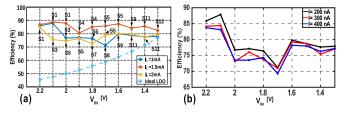

Fig. 17 (a) shows the converter's power efficiency versus  $V_{\rm IN}$  for different load currents. The power efficiency of an ideal LDO is added as a comparison. The converter's efficiency stays >80% across the entire 1.3–2.2 V input voltage range for  $I_L = 1.5$  mA. Fig. 17 (b) shows that inaccuracy of the biasing current of the gate-driver circuit, I = 300 nA  $\pm 30\%$ , leads to a negligible degradation of its power efficiency, proving that the static current consumed by the gate driver circuit has negligible effects on the power efficiency, as explained in Section III. For  $V_{IN} > 2$  V, the power efficiency is the highest, since the converter operates at the lowest CR = 1/2, in which it exhibits the lowest output resistance due to the lowest number of operating switches, as discussed in Section II .C.

Fig. 15. (a) Measured output voltage of the DC-DC converter versus  $V_{IN}$  for  $I_L = 1 \text{ mA}$ ; (b) transient waveform of  $V_{OUT}$  for descending and (c) ascending  $V_{IN}$  values along with the signal, that triggers the change in the FSM.

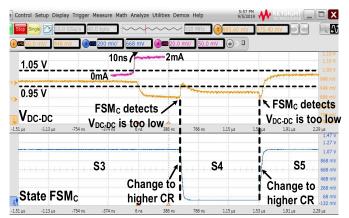

Fig. 18 shows that the converter can recover back to the desired range right after two  $FSM_C$  clock cycles (i.e.,  $2 \mu s$ ) while facing a 0–2 mA current step with a 10 ns rise time.

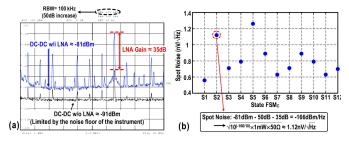

The measurement of the output noise of the DC-DC converter is limited by the noise floor of the spectrum analyzer. Hence, an LNA with a gain of 35 dB is placed after the DC-DC converter. The resulting spectrum is shown in Fig. 19 (a) (blue curve) for the FSM<sub>C</sub> in State S2. When the LNA is used, the amplitude of the peaks is amplified by 35 dB, whereas the noise is amplified by only 10 dB, proving that the measurement is no longer limited by the noise floor of the spectrum analyzer. At around 6 MHz, the measured noise integrated over the

Fig. 16. Measurement results of (a) the resolution of the converter for  $V_{IN} = V_{INmax} = 2.2$  V and  $I_L = I_{Lmin} = 0.5$  mA; (b) the monotonicity of the converter for  $V_{IN} = V_{INmin} = 1.3$  V and  $I_L = I_{Lmax} = 2$  mA.

Fig. 17. Measured power efficiency versus  $V_{IN}$  for different values of (a) load current, and (b) biasing current of the gate driver circuit.

Fig. 18. Response of the converter (orange line) to a current step from 0-2 mA (purple line) along with the signal that triggers the change in the FSM<sub>C</sub> (blue line).

resolution bandwidth of the spectrum analyzer (100 kHz) is  $\approx -81 \text{ dBm}$ . As a result, the spot noise at around 6 MHz is  $-81 \text{ dBm} - 35 \text{ dB} + 10 \log_{10}(100 \text{ kHz}) = -166 \text{ dBm/Hz} \approx 1.12 \text{ nV}/\sqrt{\text{Hz}}$ . Furthermore, the output spot noise level at

URSO et al.: SWITCHED-CAPACITOR DC-DC CONVERTER POWERING AN LC OSCILLATOR

Fig. 19. (a) Spectrum of the output voltage of the DC-DC converter with (blue line) and without (black line) the use of an LNA; (b) spot noise of the converter across different  $FSM_C$  state.

TABLE I Comparison With DC-DC Architectures

|                                  | This work         | [20]<br>JSSC16      | [14]<br>JSSC14 | [39]<br>JSSC17          | [21]<br>TPE19         | [38]<br>JSSC19               |

|----------------------------------|-------------------|---------------------|----------------|-------------------------|-----------------------|------------------------------|

| Topology                         | 3b<br>Multiratio  | 7b<br>SAR           | 4b<br>binary   | 2-/3- Phase<br>SC Conv. | Asymmetrical<br>Shunt | Algebraic<br>Series/Parallel |

| CMOS tech                        | 40 nm             | 180 nm              | 250 nm         | 130 nm                  | 250nm                 | 65nm                         |

| V <sub>IN</sub> (V)              | 1.3-2.2           | 3.4-4.3             | 2.5            | 1.6-3.3                 | 3.3                   | 0.25-1                       |

| Vout(V)                          | 1                 | >0.45               | 0.1-2.2        | 0.5-3.0                 | 0.4-2.8               | 1                            |

| lout(mA)                         | <2                | <0.3                | <2             | <250                    | <10                   | <20.1                        |

| η <sub>мах</sub> (%)             | 87                | 72                  | 85             | 91                      | 87                    | 80                           |

| f <sub>sw</sub> (MHz)<br>(Range) | 5,10,20<br>(X4)   | 0.08-2.7<br>(X34)   | 0.2-9<br>(X45) | <10<br>(>X1)            | NA                    | NA                           |

| #CR                              | 12<br>(Theory,22) | 117<br>(Theory,127) | 15             | 6                       | 187                   | 7                            |

| C <sub>fly</sub> (F)             | 2.7n              | 2.24n               | 3n             | 2x(1µ)                  | 10n                   | 3n                           |

| Cout(F)                          | 0                 | NA                  | 0              | 1μ                      | 0                     | 0                            |

| Power<br>density<br>(mW/mm²)     | 1.3               | 0.27                | 0.95           | -                       | 1.01                  | 22.7                         |

~ 6 MHz is also measured over different converter states and shown in Fig. 19 (b). The noise is always  $< 1.5 \text{ nV}/\sqrt{\text{Hz}}$ which is well below the supply noise requirement of the oscillator ( $V_n < 23 \text{ nV}/\sqrt{\text{Hz}}$ ), as discussed in Section IV.

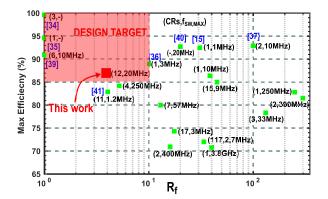

Table I provides a comparison with other DC-DC converters targeting a high number of conversion ratios. Fig. 20 reports the peak power efficiency of state-of-the-art DC-DC converters versus the ratio of maximum-to-minimum switching frequency  $(R_f = \frac{f_{SW,max}}{f_{SW,min}})$  required for the voltage regulation.  $R_f$  should normally be limited to relax the design complexity of the SRB and to avoid lowering the power efficiency, as discussed in Section V.B. At the same time, the number of CRs should be large enough to provide a *fairly* constant output voltage in the face of input voltage and load current variations. As can be gathered from Fig. 20, our work achieves one of the highest peak efficiencies with 12 CRs and an  $R_f$  as low as 4. References [15], [34]–[37] achieve higher power efficiency, but with a very limited number of CRs (e.g., 1-3). [39] implements 6 different CRs by using two off-chip flying capacitors of 1  $\mu$ F each, making the whole converter bulky.  $R_f$  of [15], [37] and [40] is also much larger than in our work, leading to a more complex system design.

#### **B.** System-Level Measurements

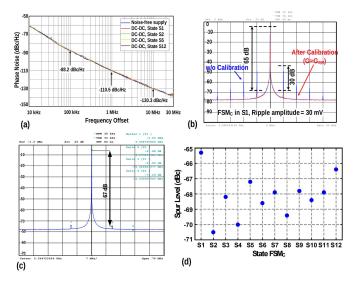

Fig. 21 (a) shows the phase noise of the oscillator when powered from a noise-free supply and from the DC-DC converter in different  $FSM_C$  states for the oscillator frequency

Fig. 20. Peak power efficiency of state-of-the-art DC-DC converters versus the ratio of maximum-to-minimum switching frequency ( $R_f = \frac{f_{SW,max}}{f_{SW,min}}$ ). The number of implemented CRs, and  $f_{SW,max}$  are reported in the parenthesis.

Fig. 21. (a) Measured oscillator PN performance at f = 5.5 GHz and (b) its spectrum before and after calibration of the SRB with FSM<sub>C</sub> in State S1 and (c) State S5; (d) spur level across different converter states when the oscillator is calibrated only at State S1.

of 5.5 GHz. The inherent PN of the oscillator is not degraded, proving that the condition imposed by Eq. (22) is met and the supply does not limit the oscillator performance. Fig. 21 (b) shows the spectrum of the oscillator before and after calibration when powered from the DC-DC converter with a ripple amplitude of  $\sim 30 \text{ mVpp}$ . The spur level is reduced by 30 dB and reaches -65 dBc after the calibration, which is 15 dB lower than the IoT requirements. A similar measurement is also performed while the oscillator is powered by the DC-DC converter in state S5, and the spectrum is depicted in Fig. 21 (c). Fig. 21 (d) shows the spurious level of the oscillator across all the states of the FSM<sub>C</sub> when the SRB of the oscillator is only calibrated in State S1. The spur level always stays below -65 dBc.

Table II summarizes the performance of the whole system and compares it with prior art. Our work is more suitable for a full system integration by avoiding external components and demonstrates the highest system peak power efficiency thanks to the removal of the LDO voltage headroom. Since the SRB is always engaged, the equivalent PSR of our approach is 12

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS

TABLE II

COMPARISON WITH SYSTEMS POWERING UP LC OSCILLATORS

|                                      |        | This work         | [2]      | [7]               | [8]     | [30]    |

|--------------------------------------|--------|-------------------|----------|-------------------|---------|---------|

| System Architecture                  |        | DC-DC+            | DC-DC+   | DC-DC+            | LDO+    | LDO+    |

|                                      |        | OSC               | LDO+OSC" | LDO <sup>††</sup> | OSC     | OSC     |

| CMOS tech                            |        | 40 nm             | 55 nm    | 65 nm             | 250 nm  | 65 nm   |

| V <sub>IN</sub> (V)                  |        | 1.3-2.2           | 1.6-3.3# | 2.4-2.6           | -       | -       |

| VIN-LDO (V)                          |        | х                 | 1.4      | 1.05              | 2-2.5   | 0.6     |

| Vout-ldo (V)                         |        | 1.0               | 1.2      | 1                 | 1.5-2   | 0.4     |

| V <sub>LDO,DROP</sub> (mV)           |        | 0                 | 200      | 50                | 500     | 200     |

| <b>η</b> dc-dc (%)                   |        | 87                | 92       | 80.3              | -       | -       |

| η∟⊳о(%)                              |        | Х                 | <85.7    | <94.9             | <79     | <60     |

| η <sub>ѕкв</sub> (%)                 |        | 98                | х        | х                 | Х       | х       |

| ητοται(%)                            |        | 85                | <79      | <76.2             | <79     | <60     |

| #ext. comp                           |        | 0                 | 2        | 0                 | 1       | 0       |

| Osc. supply noise (nV/ $\sqrt{Hz}$ ) |        | 1.26 (S5)         |          | 14.1#             | 32      | 22.4*** |

|                                      |        | @10MHz            | -        | @10MHz            | @100KHz | @10MHz  |

| C <sub>LDO</sub> (F)                 |        | Х                 | -        | 41p               | 50n     | 390p    |

| Quiescent Current<br>(µA)            |        | 20                | -        | 10                | 120     | 500     |

| PSR<br>(dB)                          | @5MHz  | 48.9 <sup>*</sup> | 20       | 12.8 <sup>†</sup> | 35      | 31†     |

|                                      | @10MHz | 43*               | 20       | 12.8 <sup>†</sup> | -       | 26†     |

<sup>\*</sup>PSR of the SRB \*\*Oscillator is part of the whole transceiver †Simulated value

#Extracted from the measurement result ++Can be used to power up an oscillator \*\*\*Calculated from phase noise with K<sub>SUP</sub>=50 MHz/V X=Not needed

calculated in this table from the difference (in dB) between the spur level measured at the optimum setting and the calculated one based on the simulated  $K_V$  of the oscillator without the SRB. Compared to the systems with LDOs, our fully passive SC converter exhibits >10× lower supply noise and our SRB shows >15 dB higher power supply rejection, preserving the oscillator's spectral purity for IoT applications.

#### VII. CONCLUSION

This paper presents an LC oscillator directly powered by a recursive switched-capacitor (RSC) DC-DC converter without using any LDOs or external components. By automatically adjusting the conversion ratio (CR), the DC variations of the converter output are kept within  $\pm 5\%$  of the desired voltage. A gate-driver circuit is proposed to guarantee a constant low  $R_{on}$  of the converter's switches, thereby meeting the resolution and monotonicity requirements while avoiding efficiency degradation. The converter output noise is  $<1.5 \text{ nV}/\sqrt{\text{Hz}}$ , and does not degrade the oscillator phase noise, while the spur reduction block (SRB) embedded in the oscillator suppresses the ripple-induced spurs to < -65 dBc, satisfying the requirement of IoT applications.

#### REFERENCES

- [1] K. Shafique, B. A. Khawaja, F. Sabir, S. Qazi, and M. Mustaqim, "Internet of Things (IoT) for next-generation smart systems: A review of current challenges, future trends and prospects for emerging 5G-IoT scenarios," *IEEE Access*, vol. 8, pp. 23022–23040, 2020.

- [2] J. Prummel et al., "A 10 mW Bluetooth low-energy transceiver with on-chip matching," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 3077–3088, Dec. 2015.

- [3] H. Abbasizadeh et al., "260-µW DCO with constant current over PVT variations using FLL and adjustable LDO," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 6, pp. 739–743, Jun. 2018.

- [4] Y. Zhang, X. Liu, W. Rhee, H. Jiang, and Z. Wang, "A 0.6 V 50-to-145 MHz PVT tolerant digital PLL with DCO-dedicated  $\sigma \delta$  LDO and temperature compensation circuits in 65 nm CMOS," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2017, pp. 1–4.

- [5] T.-H. Lin, R.-L. Hsu, C.-L. Li, and Y.-C. Tseng, "A 5 GHz, 192.6 dBc/Hz/mW FOM, LC–VCO system with amplitude control loop and LDO voltage regulator in 0.18 μm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 10, pp. 730–732, Oct. 2007.

- [6] M. D. Seeman and S. R. Sanders, "Analysis and optimization of switched-capacitor DC–DC converters," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 841–851, Mar. 2008.

- [7] Y. Lu, W.-H. Ki, and C. P. Yue, "An NMOS-LDO regulated switchedcapacitor DC–DC converter with fast-response adaptive-phase digital control," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1294–1303, Feb. 2016.

- [8] W. Oh, B. Bakkaloglu, C. Wang, and S. K. Hoon, "A CMOS low noise, chopper stabilized low-dropout regulator with current-mode feedback error amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 10, pp. 3006–3015, Nov. 2008.

- [9] G. A. Rincon-Mora and P. E. Allen, "A low-voltage, low quiescent current, low drop-out regulator," *IEEE J. Solid-State Circuits*, vol. 33, no. 1, pp. 36–44, Jan. 1998.

- [10] Q.-H. Duong *et al.*, "Multiple-loop design technique for highperformance low-dropout regulator," *IEEE J. Solid-State Circuits*, vol. 52, no. 10, pp. 2533–2549, Oct. 2017.

- [11] J. Jiang, W. Shu, and J. S. Chang, "A 65-nm CMOS low dropout regulator featuring >60-dB PSRR over 10-MHz frequency range and 100-mA load current range," *IEEE J. Solid-State Circuits*, vol. 53, no. 8, pp. 2331–2342, Aug. 2018.

- [12] Y. Lim *et al.*, "An external capacitor-less ultralow-dropout regulator using a loop-gain stabilizing technique for high power-supply rejection over a wide range of load current," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 25, no. 11, pp. 3006–3018, Nov. 2017.

- [13] Y. Chen *et al.*, "A supply pushing reduction technique for LC oscillators based on ripple replication and cancellation," *IEEE J. Solid-State Circuits*, vol. 54, no. 1, pp. 240–252, Jan. 2019.

- [14] L. G. Salem and P. P. Mercier, "A recursive switched-capacitor DC-DC converter achieving  $2^N 1$  ratios with high efficiency over a wide output voltage range," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2773–2787, Dec. 2014.

- [15] D. O. Larsen, M. Vinter, and I. Jorgensen, "Switched capacitor DC-DC converter with switch conductance modulation and pesudo-fixed frequency control," in *Proc. ESSCIRC-43rd IEEE Eur. Solid State Circuits Conf.*, Sep. 2017, pp. 283–286.

- [16] U.-F. Chio *et al.*, "An integrated DC–DC converter with segmented frequency modulation and multiphase co-work control for fast transient recovery," *IEEE J. Solid-State Circuits*, vol. 54, no. 10, pp. 2637–2648, Oct. 2019.

- [17] H.-P. Le, J. Crossley, S. R. Sanders, and E. Alon, "A sub-ns response fully integrated battery-connected switched-capacitor voltage regulator delivering 0.19W/mm<sup>2</sup> at 73% efficiency," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 372–373.

- [18] S. Bang, J.-S. Seo, L. Chang, D. Blaauw, and D. Sylvester, "A low ripple switched-capacitor voltage regulator using flying capacitance dithering," *IEEE J. Solid-State Circuits*, vol. 51, no. 4, pp. 919–929, Apr. 2016.

- [19] I. Bukreyev, C. Torng, W. Godycki, C. Batten, and A. Apsel, "Four monolithically integrated switched-capacitor DC–DC converters with dynamic capacitance sharing in 65-nm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 6, pp. 2035–2047, Jun. 2018.

- [20] S. Bang, D. Blaauw, and D. Sylvester, "A successive-approximation switched-capacitor DC–DC converter with resolution of  $V_{IN}/2^N$  for a wide range of input and output voltages," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 543–556, Feb. 2016.

- [21] Y.-T. Lin *et al.*, "A fully integrated asymmetrical shunt switchedcapacitor DC–DC converter with fast optimum ratio searching scheme for load transient enhancement," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 9146–9157, Sep. 2019.

- [22] H.-P. Le, S. R. Sanders, and E. Alon, "Design techniques for fully integrated switched-capacitor DC-DC converters," *IEEE J. Solid-State Circuits*, vol. 46, no. 9, pp. 2120–2131, Sep. 2011.

- [23] N. Pourmousavian, F.-W. Kuo, T. Siriburanon, M. Babaie, and R. B. Staszewski, "A 0.5-V 1.6-mW 2.4-GHz fractional-N all-digital PLL for Bluetooth LE with PVT-insensitive TDC using switchedcapacitor doubler in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2572–2583, Sep. 2018.

- [24] M. D. Seeman, "A design methodology for switched-capacitor DC-DC converters," EECS Dept., UC Berkeley, Berkeley, CA, USA, Tech. Rep. UCB/EECS-2009-78, 2009. [Online]. Available: https://www2.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-78. html

- [25] A. Urso and W. A. Serdijn, "A switched capacitor DC-DC buck converter for a wide input voltage range," in *Proc. IEEE Int. Symp. Circuits Syst.* (*ISCAS*), May 2018, pp. 1–5.

- [26] I. Galton and C. Weltin-Wu, "Understanding phase error and jitter: Definitions, implications, simulations, and measurement," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 1, pp. 1–19, Jan. 2019.

- [27] M. Babaie and R. B. Staszewski, "An ultra-low phase noise Class-F<sub>2</sub> CMOS oscillator with 191 dBc/Hz FoM and long-term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

- [28] X. L. Tan, S. S. Chong, P. K. Chan, and U. Dasgupta, "A LDO regulator with weighted current feedback technique for 0.47 nF–10 nF capacitive load," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2658–2672, Nov. 2014.

- [29] C. Park, M. Onabajo, and J. Silva-Martinez, "External capacitor-less low drop-out regulator With 25 dB superior power supply rejection in the 0.4–4 MHz range," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 486–501, Feb. 2014.

- [30] L. Fanori, T. Mattsson, and P. Andreani, "A class-D CMOS DCO with an on-chip LDO," in *Proc. ESSCIRC-40th Eur. Solid State Circuits Conf.* (*ESSCIRC*), Sep. 2014, pp. 335–338.

[31] L. Fanori and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid*-

- [31] L. Fanori and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [32] M. Babaie and R. B. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [33] L. G. Salem and P. P. Mercier, "A 45-ratio recursively sliced seriesparallel switched-capacitor DC-DC converter achieving 86% efficiency," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2014, pp. 1–4.

- [34] A. Sarafianos and M. Steyaert, "A true two-quadrant fully integrated switched capacitor DC-DC converter supporting vertically stacked DVSloads with up to 99.6% efficiency," in *Proc. Symp. VLSI Circuits*, Jun. 2017, pp. C210–C211.

- [35] N. Butzen and M. S. J. Steyaert, "Scalable parasitic charge redistribution: Design of high-efficiency fully integrated switched-capacitor DC–DC converters," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2843–2853, Dec. 2016.

- [36] F.-Y. Xie, B.-C. Wu, and T.-T. Liu, "A ripple reduction method for switched-capacitor DC–DC voltage converter using fully digital resistance modulation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 9, pp. 3631–3641, Sep. 2019.

- [37] T. Sai, Y. Yamauchi, H. Kando, T. Funaki, T. Sakurai, and M. Takamiya, "2/3 and 1/2 reconfigurable switched capacitor DC–DC converter with 92.9% efficiency at 62 mW/mm<sup>2</sup> using driver amplitude doubler," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 11, pp. 1654–1658, Nov. 2018.

- [38] Y. Jiang, M.-K. Law, Z. Chen, P.-I. Mak, and R. P. Martins, "Algebraic series-parallel-based switched-capacitor DC–DC boost converter with wide input voltage range and enhanced power density," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3118–3134, Nov. 2019.

- [39] J. Jiang, W.-H. Ki, and Y. Lu, "Digital 2-/3-phase switched-capacitor converter with ripple reduction and efficiency improvement," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1836–1848, Jul. 2017.

- [40] N. Butzen and M. Steyaert, "A single-topology continuously-scalableconversion-ratio fully integrated switched-capacitor DC-DC converter with 0-to-2.22 V output and 93% peak-efficiency," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2018, pp. 103–104.

- [41] A. M. Mohey, S. A. Ibrahim, I. M. Hafez, and H. Kim, "Design optimization for low-power reconfigurable switched-capacitor DC-DC voltage converter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 10, pp. 4079–4092, Oct. 2019.

Alessandro Urso (Student Member, IEEE) was born in Lecce, Italy, in 1991. He received the bachelor's and M.Sc. degrees (*cum laude*) in electronic and telecommunications engineering from the University of Ferrara, Italy, in 2013 and 2015, respectively. He is currently pursuing the Ph.D. degree with the Bioelectronics Section, Delft University of Technology, Delft, The Netherlands. His research interests include the design of power efficient neural stimulator as well as the design of switched capacitor DC-DC converter for energy harvesting application.

Yue Chen (Student Member, IEEE) received the B.Eng. degree in microelectronics and the M.Eng. degree in electronic science and technology from Xi'an Jiaotong University, Xi'an, China, in 2011 and 2014, respectively. He is currently pursuing the Ph.D. degree in electronic engineering with the Microelectronics Department, Delft University of Technology, Delft, The Netherlands. His current research interests include frequency synthesizer techniques and integrated circuits for wireless communications.

**Robert Bogdan Staszewski** (Fellow, IEEE) was born in Bialystok, Poland. He received the B.Sc. (*summa cum laude*), M.Sc., and Ph.D. degrees in electrical engineering from The University of Texas at Dallas, Richardson, TX, USA, in 1991, 1992, and 2002, respectively.

From 1991 to 1995, he was with Alcatel Network Systems, Richardson, involved in SONET cross-connect systems for fiber optics communications. He joined Texas Instruments Incorporated, Dallas, TX, USA, in 1995, where he was an elected

Distinguished Member of Technical Staff (limited to 2% of technical staff). From 1995 to 1999, he was engaged in advanced CMOS read channel development for hard disk drives. In 1999, he co-started the Digital RF Processor (DRP) group within Texas Instruments with a mission to invent new digitally intensive approaches to traditional RF functions for integrated radios in deeply-scaled CMOS technology. He was appointed as the CTO of the DRP group from 2007 to 2009. In 2009, he joined the Delft University of Technology, Delft, The Netherlands, where currently he holds a guest appointment of Full Professor (Antoni van Leeuwenhoek Hoogleraar). Since 2014, he has been a Full Professor with University College Dublin (UCD), Dublin, Ireland. He is also a Co-Founder of a startup company, Equal1 Labs, with design centers located at Silicon Valley and Dublin, Ireland, aiming to produce single-chip CMOS quantum computers. He has authored or coauthored five books, eight book chapters, 120 journal, and 200 conference publications, and holds 190 issued U.S. patents. His research interests include nanoscale CMOS architectures and circuits for frequency synthesizers, transmitters and receivers, as well as quantum computers. He was a recipient of the 2012 IEEE Circuits and Systems Industrial Pioneer Award. In May 2019, he received the title of Professor from the President of the Republic of Poland. He was the TPC Chair of 2019 ESSCIRC, Krakow, Poland.

Johan F. Dijkhuis (Member, IEEE) received the M.S. degree in electrical engineering from the University of Twente in 1998. In 1998, he was worked as an RF and Analog Design Engineer at Philips Semiconductor, NXP, ST-Ericsson, and NVIDIA. Since 2014, he has been with the Holst Centre, imec-NL. His research interests are ultra-low power RF circuit design and power management circuits for ultra-low power radios.

**Stefano Stanzione** (Member, IEEE) received the M.S. and Ph.D. degrees from the University of Pisa, Pisa, Italy, in 2006 and 2010, respectively. His Ph.D. work focused on the analog building blocks of autonomous UHF RFID tags. He joined the Holst Centre/imec, Eindhoven, The Netherlands, in 2010, where he is currently a Senior Analog IC Designer. His current research interests include ultra-low power circuits for energy harvesting and battery management. He has been a member of the Analog Technical Program Subcommittee of ISSCC from 2014 to 2018.

Yao-Hong Liu (Senior Member, IEEE) received the Ph.D. degree from National Taiwan University, Taiwan, in 2009. He was with Terax, Via Telecom (now Intel), and Mobile Devices, Taiwan, from 2002 to 2010, working on Bluetooth, Wi-Fi, and cellular wireless SoC products. Since 2010, he joined imec, The Netherlands. He currently holds a principal membership position of Technical Staff, and he is leading the development of the ultra-low power wireless IC design. His research interests include energy-efficient RF transceivers

and radar for IoT and healthcare applications. He currently serves as a Technical Program Committee of the IEEE ISSCC and RFIC Symposium.

Wouter A. Serdijn (Fellow, IEEE) was born in Zoetermeer ('Sweet Lake City'), The Netherlands, in 1966. He received the M.Sc. (*cum laude*) and Ph.D. degrees from the Delft University of Technology, Delft, The Netherlands, in 1989 and 1994, respectively.

He is currently a Full Professor of bioelectronics at the Delft University of Technology, where he heads the Bioelectronics Section, and a Medical-Delta Honorary Professor at the Delft University of Technology and the Erasmus Medical Center, Rotterdam.

He teaches analog integrated circuit design, active implantable biomedical microsystems, and bioelectronics. He is a co-editor and coauthor of ten books, eight book chapters, and more than 300 scientific publications and presentations, and holds four patents. His research interests include integrated

biomedical circuits and systems for biosignal conditioning and detection, neuroprosthetics, transcutaneous wireless communication, power management, and energy harvesting as applied in, e.g., cardiac pacemakers, cochlear implants, neurostimulators, bioelectronic medicine, and electroceuticals.

Dr. Serdijn is a Distinguished Lecturer of the IEEE and a mentor of the IEEE. He received the IEEE Circuits and Systems Meritorious Service Award in 2016 and the Electrical Engineering Best Teacher Award in 2001, 2004, and 2015. He has served as the General Co-Chair for the IEEE ISCAS 2015 and the IEEE BioCAS 2013, the Technical Program Chair for the IEEE BioCAS 2010 and the IEEE ISCAS 2010, 2012, and 2014, as a member of the Board of Governors (BoG) of the IEEE Circuits and Systems Society from 2006 to 2011, as the Chair of the Analog Signal Processing Technical Committee of the IEEE Circuits and Systems Society, and as the Editor-in-Chief for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS from 2010 to 2011. He is currently the Chair of the Steering Committee and an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS (T-BioCAS).

**Masoud Babaie** (Member, IEEE) received the Ph.D. degree (*cum laude*) in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 2016.

In 2006, he joined Kavoshcom Research and Development Group, Tehran, where he was the CTO from 2009 to 2011. He was involved in designing wireless communication systems at that company. From 2014 to 2015, he was a Visiting Scholar Researcher with the Berkeley Wireless Research Center, Berkeley, CA, USA. In 2016, he joined the

Delft University of Technology, where he is currently a tenured Assistant Professor. His current research interests include RF/millimeter-wave integrated circuits and systems for wireless communications, and cryogenic electronics for quantum computation.

Dr. Babaie has been a Committee Member of the Student Research Preview (SRP) of the IEEE International Solid-State Circuits Conference (ISSCC) since 2017. He was a co-recipient of the 2015–2016 IEEE Solid-State Circuits Society Pre-Doctoral Achievement Award and the 2019 IEEE ISSCC Best Demo Award. In 2019, he also received the Veni award from the Netherlands Organization for Scientific Research (NWO). He is currently serving on the Technical Program Committee of the IEEE European Solid-State Circuits Conference (ESSCIRC).