# Open-source IP cores for space

# A processor-level perspective on soft errors in the RISC-V era

Di Mascio, Stefano; Menicucci, Alessandra; Gill, Eberhard; Furano, Gianluca; Monteleone, Claudio

10.1016/j.cosrev.2020.100349

**Publication date**

**Document Version** Final published version

Published in Computer Science Review

Citation (APA)

Di Mascio, S., Menicucci, A., Gill, E., Furano, G., & Monteleone, C. (2021). Open-source IP cores for space:

A processor-level perspective on soft errors in the RISC-V era. *Computer Science Review, 39*, Article 100349. https://doi.org/10.1016/j.cosrev.2020.100349

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

ELSEVIER

Contents lists available at ScienceDirect

# **Computer Science Review**

journal homepage: www.elsevier.com/locate/cosrev

# Review article

# Open-source IP cores for space: A processor-level perspective on soft errors in the RISC-V era

Stefano Di Mascio <sup>a,\*</sup>, Alessandra Menicucci <sup>a</sup>, Eberhard Gill <sup>a</sup>, Gianluca Furano <sup>b</sup>, Claudio Monteleone <sup>b</sup>

#### ARTICLE INFO

# Article history: Received 4 August 2020 Received in revised form 4 December 2020 Accepted 9 December 2020 Available online 24 December 2020

Keywords: Processors Fault tolerance Space

#### ABSTRACT

This paper discusses principles and techniques to evaluate processors for dependable computing in space applications. The focus is on soft errors, which dominate the failure rate of processors in space. Error, failure and propagation models from literature are selected and employed to estimate the failure rate due to soft errors in typical processor designs. A similar approach can be followed for applications with different radiation environments (e.g. automotive, servers, experimental instrumentation exposed to radiation on ground), by adapting the error models. This detailed white-box analysis is possible only for open-source Intellectual Property (IP) cores and in this work it will be applied to several open-source IP cores based on the RISC-V Instruction Set Architecture (ISA). For these case studies, several types of redundancy described in literature for space processors will be evaluated in terms of their cost-effectiveness and expected final in-orbit behavior. This work provides a comprehensive framework to assess efficacy and cost-effectiveness of redundancy, instead of listing and categorizing the techniques described in literature without assessing their relevance to state-of-the-art designs in space applications.

© 2020 The Author(s). Published by Elsevier Inc. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/).

#### Contents

| 1. | Introd  | 1uction                                                                               | 3  |

|----|---------|---------------------------------------------------------------------------------------|----|

|    | 1.1.    | Objective                                                                             | 3  |

|    | 1.2.    | Objective                                                                             | 3  |

|    | 1.3.    | Outline                                                                               | 4  |

| 2. | Identif | fying and modeling threats                                                            | 4  |

|    | 2.1.    | Fault and error models                                                                | -4 |

|    |         | 2.1.1. Upsets                                                                         | 4  |

|    |         | 2.1.2. Single event transients (SETs)                                                 | 6  |

|    |         | 2.1.1. Upsets 2.1.2. Single event transients (SETs) 2.1.3. Errors in SRAM-based FPGAs | 6  |

|    |         | 2.1.4. Model adopted                                                                  | 7  |

|    | 2.2.    | Error propagation to the service interface                                            | 7  |

|    | 2.3.    | Service interface and error tolerance                                                 | 7  |

|    |         | 2.3.1. Intrinsic error tolerance                                                      | 7  |

|    |         | 2.3.2. Explicit error tolerance                                                       | 8  |

| 3. | Model   | ling the vulnerability of processors                                                  | 8  |

|    | 3.1.    | AVF decomposition                                                                     | 8  |

|    |         | 3.1.1. Vulnerability in time: ACE analysis                                            | 9  |

|    | 3.2.    | Impact of the microarchitecture on the failure rate                                   | 9  |

|    |         | 3.2.1. Design explorations                                                            | 10 |

|    | 3.3.    | Impact of other factors on the failure rate                                           | 12 |

|    |         | 3.3.1. Dependence on performance and compiler flags                                   | 12 |

E-mail addresses: s.dimascio@tudelft.nl (S. Di Mascio), a.menicucci@tudelft.nl (A. Menicucci), e.k.a.gill@tudelft.nl (E. Gill), gianluca.furano@esa.int (G. Furano), claudio.monteleone@esa.int (C. Monteleone).

<sup>&</sup>lt;sup>a</sup> Delft University of Technology, 2629 HS Delft, The Netherlands

<sup>&</sup>lt;sup>b</sup> European Space Agency, 2200 AG Noordwijk, The Netherlands

<sup>\*</sup> Corresponding author.

|    |        | 3.3.2.     | Dependence on software                                      | 12 |

|----|--------|------------|-------------------------------------------------------------|----|

|    |        | 3.3.3.     | Dependence on software  Dependence on the fraction of MBUs  | 13 |

|    |        | 3.3.4.     | Uncertainty due to the estimation method employed           | 13 |

|    | 3.4.   | Limitatio  | ons of the AVF decomposition                                | 13 |

|    |        | 3.4.1.     | Sub-unit vulnerability                                      | 13 |

|    |        | 3.4.2.     | Propagation to specific signals at the service interface    | 13 |

|    |        | 3.4.3.     | Propagation time                                            |    |

|    |        | 3.4.4.     | Error accumulation                                          | 14 |

| 4. | Applyi | ing cost-e | ffective redundancy                                         | 14 |

|    | 4.1.   | Choice of  | of redundancy for cache arrays                              |    |

|    |        | 4.1.1.     | Layout solutions                                            | 15 |

|    |        | 4.1.2.     | Refreshing                                                  | 15 |

|    |        | 4.1.3.     | Cost-effective redundancy for cache arrays                  | 15 |

|    | 4.2.   | Choosin    | g the redundancy for the rest of the processor              | 17 |

|    |        | 4.2.1.     | Choosing the redundancy for the RFs                         | 17 |

|    |        | 4.2.2.     | Choosing the redundancy for mixed logic                     |    |

|    |        | 4.2.3.     | Protecting simultaneously small SRAM arrays and mixed logic | 18 |

| 5. | Expect | ted in-orb | pit behavior and validation                                 | 19 |

|    | 5.1.   |            | on                                                          |    |

|    | 5.2.   | Summai     | 'У                                                          | 21 |

| 6. | Conclu | usion      |                                                             | 21 |

|    |        |            | competing interest                                          |    |

|    | Ackno  | wledgme    | nts                                                         | 22 |

|    | Refere | ences      |                                                             | 22 |

|    |        |            |                                                             |    |

| List of abbreviation | ons                                     |

|----------------------|-----------------------------------------|

| AC                   | Average Criticality                     |

| ACE                  | Architecturally Correct Execution       |

| ALU                  | Arithmetic-Logic Unit                   |

| ASIC                 | Application-Specific Integrated Circuit |

| AVF                  | Architectural Vulnerability Factor      |

| BP                   | Branch Prediction                       |

| CC                   | Clock Cycle                             |

| CI                   | Cell Interleaving                       |

| CL                   | Criticality Level                       |

| COTS                 | Commercial-Off-The-Shelf                |

| CPI                  | Cycles Per Instruction                  |

| CSR                  | Control and Status Registers            |

| CU                   | Constant Utilization                    |

| CVF                  | Cache Vulnerability Factor              |

| CW                   | Constant Workload                       |

| DC                   | Data Cache                              |

| DMR                  | Double Modular Redundancy               |

| DUE                  | Detected Uncorrectable Error            |

| ECC                  | Error Correcting Code                   |

| EDAC                 | Error Detection and Correction          |

| EDC                  | Error Detecting Code                    |

| FDSOI                | Fully-Depleted Silicon-On-Insulator     |

| FF                   | Flip Flop                               |

| FI                   | Fault Injection                         |

| FinFET               | Fin Field-Effect Transistor             |

| FPGA                 | Field Programmable Gate Array           |

| FPU                  | Floating Point Unit                     |

| FRF                  | Floating Register File                  |

| FT                   | Fault-Tolerant                          |

| GCR                  | Galactic Cosmic Rays                    |

| GEO                  | Geostationary Orbit                     |

| GP                   | General Purpose                         |

| НС                   | High Criticality                        |

| НРС  | High-Performance Computing     |

|------|--------------------------------|

| IB   | Instruction Buffer             |

| IC   | Instruction Cache              |

| ID   | Interleaving Distance          |

| IF   | Instruction Fetch              |

| II   | Instruction Issue              |

| IOD  | In-Orbit Demonstration         |

| IP   | Intellectual Property          |

| IPC  | Instructions Per (clock) Cycle |

| IRF  | Integer Register File          |

| ISA  | Instruction Set Architecture   |

| IU   | Integer Unit                   |

| L1   | Level 1                        |

| L2C  | Level 2 Cache                  |

| LC   | Low Criticality                |

| LEO  | Low Earth Orbit                |

| LET  | Linear Energy Transfer         |

| LLC  | Last-Level Cache               |

| LSU  | Load and Store Unit            |

| M/D  | Multiplier and Divider         |

| MBU  | Multiple Bit Upset             |

| MCU  | Multiple Cell Upset            |

| MD   | MBU Dominated                  |

| MLP  | Memory Level Parallelism       |

| MPEG | Moving Picture Experts Group   |

| MTTE | Mean Time To Event             |

| MTTF | Mean Time To Failure           |

| OBC  | On-Board Computer              |

| 000  | Out-of-Order                   |

| OS   | Operating System               |

| QoS  | Quality of Service             |

| RF   | Register File                  |

| RHBD | Radiation-Hardened By Design   |

| ROB  | ReOrder Buffer                 |

|      |                                |

| RR     | Register Rename                    |

|--------|------------------------------------|

| RTI.   | Register Transfer Level            |

|        |                                    |

| SAA    | South Atlantic Anomaly             |

| SBF    | Single Bit Flip                    |

| SBU    | Single Bit Upset                   |

| SD     | SET Dominated                      |

| SECDED | Single Error Correction and Double |

|        | Error Detection                    |

| SED    | Single Error Detection             |

| SER    | Soft Error Rate                    |

| SET    | Single Event Transient             |

| SEU    | Single Event Upset                 |

| SNR    | Signal-to-Noise Ratio              |

| SoC    | System-on-Chip                     |

| SOI    | Silicon-On-Insulator               |

| SRAM   | Synchronous Random Access Memory   |

| TID    | Total Ionizing Dose                |

| TMR    | Triple Modular Redundancy          |

| UT     | Unexpected Termination             |

| WB     | Write-Back                         |

| WT     | Write-Through                      |

|        |                                    |

#### 1. Introduction

Space systems rely on digital electronics for on-board data handling and processing, and processors are key elements (along with memories and interfaces) to achieve such functionalities [1]. When selecting a processor for satellite data systems, typically two choices are available: either a space-grade processor with long flight heritage and well-characterized behavior (e.g. LEON processors [2]), or a proprietary Commercial-Off-The-Shelf (COTS) processor employed as a black box (sometimes after adequate radiation test [3,4]). The latter is preferred to the former when the performance required cannot be met with space-grade processors [5], which typically lag behind their commercial counterparts in terms of performance [6]. The recent availability of opensource Intellectual Property (IP) cores for terrestrial applications, mainly based on the RISC-V Instruction Set Architecture (ISA) [7], allows for a better understanding of their vulnerability, avoiding black-box characterization (typical of proprietary COTS components) and allowing a trade-off between the two approaches. A better modeling of the inner working of processors can both help choosing the best IP core and its configuration. For instance, in [8] the lack of public Register Transfer Level (RTL) models (typical of proprietary processors) is identified as the main issue when trying to characterize the effects of upsets in a microarchitecture (mainly because it is not possible to estimate the exact number of sequential elements). Furthermore, the authors of [9] suggest that the failure rate measured with beam experiments is much larger than the one estimated by Fault Injection (FI) due to unknown proprietary parts of the real physical hardware platform compared to the virtual platform where the FI was carried out.

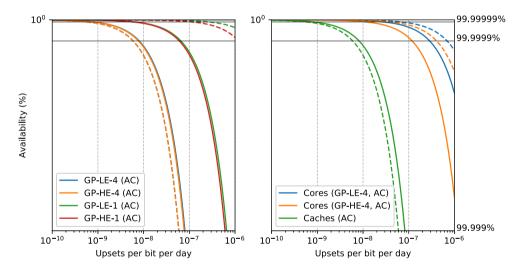

Once the vulnerability of a processor is estimated, it can be reduced employing redundancy. Redundancy typically comes with significant area, power and performance overhead. Therefore, assessing its cost-effectiveness is crucial. However, the amount and type of optimal redundancy can change drastically depending on the requirements in terms of dependability (i.e. reliability, availability, safety [10]) and performance as well as on the target environment. For instance, in automotive the focus of the standard ISO-26262 [11] is on functional safety. For this reason,

several Application-Specific Integrated Circuits (ASICs) for automotive employ two processors executing instructions in lockstep, so that errors can be detected comparing the outputs of the two replicas and the processors are restarted in case of mismatch [3]. A similar approach can reduce availability, as for instance even benign differences at the outputs of the processors will cause a reset. Furthermore, as long as the safety requirements are met, availability is not a primary concern in automotive. This is not the case for space applications, as dependable processors in space are expected to provide a certain service without interruptions over a certain span of time, hence the focus is instead on availability. For example, in the case of a geostationary telecommunication satellite the time span of a mission could be more than 15 years in which the whole space system is expected to provide a certain service 99.9% of the time [12]. Therefore, the unavailability budget for the On-Board Computer (OBC) is even tighter. Furthermore, when the processor is intended for usage in space, the presence of ionizing radiation makes soft errors far more likely and the amount of redundancy must be carefully evaluated as power and area available in space data systems are typically very limited. On the other hand, loss of performance in space data systems can be easily tolerated in most cases. In High-Performance Computing (HPC) the constraints are the opposite, as the amount of loss in terms of performance that can be tolerated is typically very limited [13].

# 1.1. Objective

The objective of this paper is to introduce readers familiar with processors and typical performance/power/area trade-offs in digital electronics [14] to consider also dependability with quantitative tools, taking as a relevant example the extreme case of space applications. This work develops a comprehensive framework at processor-level<sup>1</sup> to assess and mitigate the soft error vulnerability of processors in a cost-effective way. The need for this work and its nature of a survey, instead of a completely experimental paper (like for instance [16]), is given by the fact that most of the works in literature describe in great detail specific aspects of the vulnerability of specific hardware structures and how to address soft error vulnerability of specific units in a processor (e.g. register files [17], data [18] and tag [19] array in caches). This sub-processor approach is dictated by the extensive work required to build a relevant test setup and to the number of experiments required to get meaningful statistics. In this paper we will complement these works by putting their results together, using them to develop a comprehensive framework that the reader can reuse and readapt to its own designs or when evaluating an open-source IP core. Although using several extrapolations and approximations, this approach allows the reader to have a complete view of the specific challenges involved in the design of a dependable processor for space and to estimate the effects of a different environment/technology/microarchitecture/redundancy given limited experimental data.

# 1.2. Scope and related works

The techniques to increase dependability reported in this work are those typically employed for space processors such as LEON [2], TCLS [20] and those developed by Boeing [21]. Therefore, this work can be read as a survey of state-of-theart techniques to evaluate and design processors for dependable

<sup>&</sup>lt;sup>1</sup> That is, including caches but excluding peripherals, interconnects, interfaces, off-chip memories and main memory. However, processors are typically included in a System-on-Chip (SoC) together with peripherals and memories. To further extend this framework, the reader can refer to the work in [15], which estimates the impact of other subsystems of SoCs.

space applications. For readers interested in a wider range of applications, there are instead some related works in literature. A survey listing techniques to model and improve reliability of computing systems was published in [22]. From there, additional techniques not included in this work (both because they are not relevant to space processors and for sake of brevity) can be included in our framework. An introduction to the soft error problem in processors was published in [23], covering soft error mitigation techniques at device, circuit, microarchitectural and software level. In this work, we will develop further all the aspects related to the microarchitecture and will establish a model built putting together results from literature. This will give more insights on how to evaluate open-source IP cores and how to enhance their dependability in a cost-effective way. For instance, only 10 out of 132 references of this paper are used also in [23] and some of them are only necessary to introduce the topic (e.g. [10], which proposes a nomenclature for dependable systems). Other comprehensive frameworks were proposed in recent years (2016–2019) [24,25]. The present framework differs for three reasons: it is built from a survey of the literature, it has a wider scope (e.g. comprising definition of threat models from the space environment, and considerations on availability and validation) and it is described step by step to the reader (see Table 15). The reader can therefore implement the framework for its own designs and contribute to its extension in a straightforward way.

# 1.3. Outline

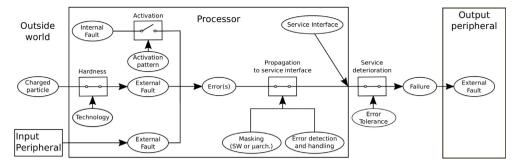

To introduce the reader to the problem, the first part of this paper follows the error from its generation to the occurrence of the service failure (as shown in Fig. 1). In Section 2.1, typical faults in space processors are identified and an error model is associated to each of them, in Section 2.2 the outcomes of the defined error models are analyzed up to the service interface, and in Section 2.3 the application-dependent effects of errors at the service interface are analyzed.

The second part of the paper follows instead the steps of a typical design flow for a fault-tolerant processor. In Section 3.1 a quantitative model to identify the most vulnerable units of processors is presented and in Section 3.2 it is applied to four different processor designs. Section 4 then analyzes several types of redundancy and discusses their cost-effectiveness. Section 5 discusses aspects related to validation and in-orbit expected behavior. Finally, Section 6 draws conclusions.

# 2. Identifying and modeling threats

Fig. 1 shows how threats<sup>2</sup> interact with a processor. A failure is a deviation from the expected behavior of the service provided at the service interface [10], and it is caused by one or more deviations from the correct state of the system (errors). The cause of the error is called fault [10]. Changes in the charge stored in nodes due to particle strikes are typical faults in space processors (external faults in Fig. 1), and they are called soft errors as they can be removed simply overwriting them with the correct value [26]. This is not the case for hard errors [27], where the distinction between fault (e.g. defective gate) and error (e.g. wrong result of a calculation) is needed for correct recovery (e.g. to replace a defective unit with a spare unit).

#### 2.1. Fault and error models

Regardless of the specific threats due to the space environment, processors in space have to be first of all robust against faults common to processors in terrestrial applications.<sup>3</sup> For instance, simulations for a 32 nm ASIC technology show that the data propagation delay of Flip Flops (FFs) increases less than 5% in 5 years of stress conditions due to aging [28]. This can be taken into account during design by applying larger margins on the maximum allowed frequency. Aging and hard faults due to imperfections or wear out can be classified as internal faults in Fig. 1, for which environmental conditions and specific activation patterns are required in order to generate errors. Despite hard errors, soft errors due to radiation typically dominate the failure rate of processors already in terrestrial environments. In [29] the ratio of soft errors to hard errors for Synchronous Random Access Memory (SRAM) arrays in processors ranges from 77 to 735, and in [30] 99.36% of the errors in an SRAM array are soft errors while 0.64% are hard errors. Soft errors in space are even more predominant, as in this case charged particle strikes are more common (outside the Earth atmosphere the flux of particles is higher) and different particles are present (heavy ions and protons instead of neutrons) [31].

Furthermore, our focus in this paper is on faults capable of generating functional errors and we will not consider faults which generate electrical failures like Single Event Latchups [32] and increase of absorbed current due to Total Ionizing Dose (TID) effects [33]. The reason is that those are typically not addressed at microarchitectural level but at technology and electrical level instead.

# 2.1.1. Upsets

Ionizing particles can change the value stored in a single or more sequential elements. In the first case, the terms Single Event Upset (SEU) or Single Bit Upset (SBU) are employed. In the second case, the term Multiple Bit Upset (MBU) can be used.<sup>4</sup>

The upset rate  $\lambda_{ev}$  mainly depends on the radiation environment (including also shielding), the technology<sup>5</sup> and the choice of the sequential and combinational elements in the processor within the same technology. The upset rate can be either estimated with environmental models or measured on the field [34]. In the first case, a standard approach is to carry out a radiation test composed of several test runs with particles with different Linear Energy Transfer (LET)<sup>6</sup> and measure the respective cross section.<sup>7</sup> Afterwards, tools like SPENVIS [36] are used to calculate the differential LET spectrum which can be obtained from the

<sup>&</sup>lt;sup>2</sup> In [10], the term 'threats' refers to faults, errors, and failures.

$<sup>^3</sup>$  In our discussion we do not include systematic failures due to bugs that should not be considered part of dependability but of normal engineering practice (verification).

<sup>&</sup>lt;sup>4</sup> Sometimes the term Multiple Cell Upset (MCU) is employed instead, while MBU is reserved to cases where the multiple upsets are in the same Error Detection and Correction (EDAC)-protected word. Furthermore, the notation MBU(n) will be employed to indicate MBUs causing n upsets with a single particle strike.

<sup>&</sup>lt;sup>5</sup> Several factors can be included in the technology. For instance, the error rate per bit on a specific technology depends on the voltage chosen (in [16] decreasing the voltage from 1.2 V to 0.8 V results in an increase of the error rate by a factor 1.5x up to 3x, depending on the radiation source). However, as shown in [16], this does not change the ratio between errors from combinational and sequential logic.

<sup>&</sup>lt;sup>6</sup> The LET represents the energy loss of the particle when it travels a unit distance in the semiconductor [35]. It is typically normalized to the density of the material and given in MeVcm<sup>2</sup>/mg.

<sup>&</sup>lt;sup>7</sup> The device cross section for a given LET is defined as the quantity that multiplied by the particle flux produces the SEE rate of that flux of particles. It is typically given as  $cm^2/device$  or  $cm^2/b$  [35].

Fig. 1. Typical interactions of threats with a processor providing a service to an output peripheral.

particle differential energy spectra in a certain orbit [35]. The upset rate can be then found with the following integral [35]:

$$\lambda_{ev} = \int_0^{\inf} \int_{-1}^1 \int_0^{2\pi} f(L, \theta, \phi) \, \sigma(L, \theta, \phi) \, d\phi \, d\cos(\theta) \, dL \tag{1}$$

where the differential flux f and the cross section per bit  $\sigma$  depend on the LET L and the incidence and rotation angles ( $\theta$  and  $\phi$ ) [35].

Data from [37] shows for a commercial 28 nm Fully-Depleted Silicon-On-Insulator (FDSOI) SRAM an in-orbit SEU rate of  $4.66 \times$ 10<sup>-9</sup> upsets/bit/day for solar minimum in Geostationary Orbit (GEO). From data in the same work, an estimation of  $5 \times 10^{-7}$ for worst week in GEO and  $5 \times 10^{-10}$  upsets/bit/day for Low Earth Orbit (LEO) can be taken (three orders of magnitude less than GEO worst conditions). Data from [38] show that considering different time spans will have different worst cases, e.g. the upset rate for the worst case of an SRAM array for one week in GEO is one order of magnitude lower than the worst case for 5 min, the latter reaching an upset rate of around 10<sup>-2</sup> upsets/bit/day (similar values are given in [39], some of them even reaching  $10^{-1}$ upsets/bit/day). Furthermore, the upsets are not homogeneously distributed in a certain orbit. For instance, all reboots in [40] (LEO) due to upsets happened in the South Atlantic Anomaly (SAA) and over the poles, where the level of radiation is higher due to the lower magnetic field shielding. To provide a comparison with processors in terrestrial environment, the upset rates at sea level in [41] is assumed to be  $2.7 \times 10^{-11}$  upsets/bit/day, which is four orders of magnitude less than for the 28 nm FDSOI in GEO (worst

The radiation environment experienced by the processor depends also on the amount of shielding, which cannot be controlled by the designer of the processor. In [38] it is shown that the reduction of upset rate due to an ideal aluminum sphere going from 0.1 mm to 2.5 mm is of 4 orders of magnitude for a 45 nm Silicon-On-Insulator (SOI) SRAM in the case of trapped protons, typical of LEO [42]. Considering an electronic box in a spacecraft brings the upset rate down of roughly another order of magnitude. However, in [38] it is shown that Galactic Cosmic Rays (GCR) are insensible to shielding depths. This causes a plateau of  $8.64 \times 10^{-7}$  upsets/bit/day for the SRAM technology considered in [38], where adding more shielding does not improve the radiation tolerance of the part which must be addressed exclusively at semiconductor level.

In a similar manner, different technologies exhibit different upset rates in the same radiation environment. A typical Radiation-Hardened By Design (RHBD) SRAM memory based on a 250 nm technology has been reported in [34] to operate in GEO with an average of  $1.8 \times 10^{-10}$  upsets/bit/day. A commercial SRAM based on 65 nm bulk technology in [43] is reported to experience an average of  $1.5 \times 10^{-7}$  upsets/bit/day in LEO, and in GEO would show an even higher upset rate. Space-grade processors are currently based on 65 nm (e.g. GR740 [1]) or even

180 nm (e.g. GR716 [2]) RHBD ASIC technologies, while typical processors for terrestrial application are typically below 28 nm (e.g. [44]). These newer technologies are expected to be more vulnerable: when scaling from 65 nm to 14 nm the upset rate increases from around  $10^{-12}$  to around  $10^{-11}$  upsets/bit/day for planar bulk technologies, while it increases from  $10^{-11}$  to  $10^{-10}$  upsets/bit/day for FDSOI and Fin Field-Effect Transistor (FinFET) technologies [45] (all of them measured at ground altitudes). For all three types of technologies the increase happens when going beyond 28 nm, while from 65 to 28 nm the upset rate is constant or slightly decreasing.

Even in the same technology, different sequential elements composing the processor can have different upset rates. For instance, the OpenSPARC T2 in [46] (65 nm) is mainly composed of SRAM arrays optimized for density (for caches) with an upset rate ranging between  $8.58 \times 10^{-13}$  and  $1.14 \times 10^{-12}$  upsets/bit/day, less-dense and higher-performance SRAM arrays (for register files) with an upset rate per bit of half or less and FFs with an upset rate per bit of one-third or less compared to the SRAM array optimized for density. However, as [47] shows, this is not always the case and several technologies (especially newer ones) show the opposite situation. As a matter of fact, the ratio of the upset rate of FFs to SRAM cells in [47] is 0.44 for 130 nm, 1.96 for 90 nm, 1.75 for 65 nm and 1.15 for 40 nm technologies.

The differentiation between FFs and SRAM arrays is also required because FFs have temporal masking, which is not present in SRAM arrays. If we consider an upstream sequential element connected to a downstream element through combinational logic, an upset happening in the upstream element between  $t = t_{samp}$  $T_{prop}$  and  $t = t_{samp}$  (where  $t_{samp}$  is the sampling instant given by the clock and  $T_{prop}$  is the time required for the correct sampling of a signal propagating from the upstream to the downstream element) will not propagate to the sequential elements downstream. A sampling factor can be defined as  $SF_{FF} = 1 - \frac{T_{prop}}{T_{clk}}$ , where  $T_{clk}$  is the clock period for the FFs. This implies that the fraction of temporally masked errors in FFs actually increases with the frequency [16]. Despite this masking, typical models used in literature assume a constant failure rate for FFs when changing frequency [48], while more refined analyses find that there is an increase of the failure rate due to a Single Event Transient (SET) mechanism in the combinational logic between master and slave [49]. Data provided in [49] show that this increase is very small, when considering a single FF the maximum found is  $5 \times 10^{-15}$  errors/bit/day/MHz. Considering a design going from 100 MHz to 1 GHz, the error rate increases by 4.5  $\times$  $10^{-12}$  errors/bit/day, which is of orders of magnitude less even compared to the less vulnerable technologies for space (around  $10^{-10}$  upsets/bit/day). However, as mentioned in [16], testing shift registers where  $T_{prop}$  is close to zero fails to take into account temporal masking, and  $SF_{FF}$  is close to one for practical values of frequency. On the other hand, when testing a circuit with both sequential and combinational logic, understanding which of the

two generated the error sampled in an FF to validate the temporal masking model is a daunting task. According to the model in [16], temporal masking instead can have a considerable impact. In [16] an average  $SF_{FF}$  of 66.6% is given. When lowering the frequency on the same design the sampling factor increases, until for 100 MHz the sampling factor gets to 96.66%.

Even the same type of sequential element can come in different sizes for the right performance/power/area trade-off. Data from [50] shows that FFs for a 65 nm commercial bulk technology have upset rates ranging between  $1.6 \times 10^{-7}$  upsets/bit/day (fastest FF) and  $4.1 \times 10^{-7}$  upsets/bit/day (slowest FF, 2.56x more vulnerable). Rad-hard (radiation-hardened) versions of the same technology have upsets rates ranging from  $8.12 \times 10^{-8}$  to  $1.82 \times 10^{-9}$  upsets/bit/day (2.24x increase of vulnerability with a 3x increase in drive strength). From [51] it can be seen that a rad-hard version of a FF on commercial technology can achieve a reduction of upset rate of 350x. In [16] several frequency targets (ranging from 100 MHz to 900 MHz) are set when synthesizing a processor, generating implementations with different mix of FFs. This increases vulnerability up to 10% (i.e.  $RV_{FF} = 1.1$ ) taking the less vulnerable as reference. This increase follows a regular pattern, growing with the difference between the target frequency (e.g. 900 MHz) and the real clock frequency (e.g. 100 MHz).

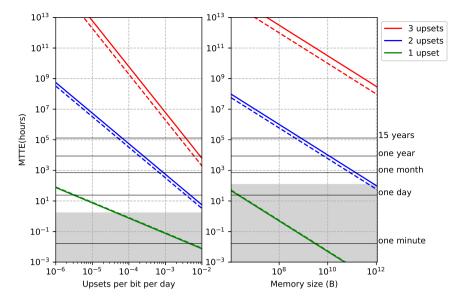

The upset rate  $\lambda_{ev}$  is typically assumed constant [52] (i.e. interarrival times of raw errors in a component are independent [52]) and therefore the reliability function is exponential for each sequential element, i.e.  $R_b(t) = e^{-\lambda_{ev} \times t}$ . The use of the exponential distribution implies that the error rate of a series of elements becomes the sum of the error rates and the probability of not having an upset in the processor is  $R_{SEU}(t) = e^{-SER_{SEU} \times t}$ , where the Soft Error Rate (SER) due to SEUs is:

$$SER_{SEU} = \lambda_{ev} \times (N_{SRAM} \times RV_{SRAM} + N_{FF} \times RV_{FF} \times SV_{FF})$$

(2)

where  $N_{SRAM}$  and  $N_{FF}$  are respectively the number of SRAM cells and FFs.  $RV_{SRAM}$  and  $RV_{FF}$  are the average vulnerability of respectively SRAM cells and FFs employed relatively to a reference sequential element with event rate  $\lambda_{ev}$ .

When considering MBUs, they can be measured as fraction of the total events. This means that if two events happen, one generating a SBU and one a MBU, the fraction of MBU is 50% regardless of the number of errors due to the MBU. Data from [53] show that for SRAM arrays in a 90 nm ASIC technology 95% of events cause a SBUs, 4% cause a MBU(2) and 1% cause MBU(3). For 65 nm SRAM arrays the situation reported in [53] is quite different: 45% are SBUs, 18% are MBU(2), 10% are MBU(3) and 27% are MBU( $\geq$ 4). As a pessimistic estimation for Ultra Deep Sub Micrometer (UDSM) technologies data from [54] for a 32 nm SRAM array<sup>8</sup> can be taken: in this case the fraction of SBUs is 24%, the fraction of MBU(2) is 52%, the fraction of MBU(3) is 3% and the fraction of MBU( $\geq$ 4) is 21%.

# 2.1.2. Single event transients (SETs)

A single particle hitting a combinational node is able to cause a transient voltage pulse [55]. This pulse can be latched by the sequential elements downstream and can be either seen as a single error or multiple errors in sequential elements by the user (e.g. software level). Even if the user is not able to distinguish between SETs and upsets, SETs have different generation mechanisms that require different redundancy techniques compared to SBUs and MBUs. As a matter of fact, SETs have additional levels

of masking (electrical and logical) [56]. Furthermore, they have a different temporal masking mechanism: if the pulse reaches the sequential element outside from the sampling window, then the spike is not sampled and the error not generated. This implies that the contribution of SETs increases with the increase of the frequency. The reason is that when frequency increases, the sampling window becomes a larger fraction of the total time.

In relatively old technologies (e.g. technology nodes larger than 90 nm), SETs are not predominant as they are attenuated by large capacitance (electrical masking) and the low clock frequencies make the sampling unlikely (temporal masking) [57]. In more recent technologies instead, capacitance is reduced and the clock frequency is higher. For this reason, the probability that a spike is latched increases [57]. In [58] a comparator, an FF chain and an inverter chain are tested to compare the contribution of SETs and SEUs on a 45 nm bulk technology. The chain of inverters in [58] has a depth (12 stages) to emulate the highest electrical masking available typically in designs and accounts only for electrical and temporal masking, while the comparator also account for logical masking. As logical masking depends upon the input combination, in [58] a best, average and worst case are given. The worst case counts around twice the SETs compared to the best case. Furthermore, in [58] errors due to combinational logic (inverter chain) are less than one eighth of errors in sequential elements up to 100 MHz, around half at 500 MHz and uncertainties overlaps for 1 GHz (even if the expected value is still at half the sequential elements). The crossover frequency is around 1.5 GHz for the inverter chain and between 1.7 and 5 GHz for the comparator. However, considering that the vulnerability of FFs decreases with frequency, the contribution of sequential logic would be higher and the crossover frequency lower. This shows how increasing frequency does not necessarily increase the error rate, but certainly increases the relative vulnerability of combinational logic in the design, making optimal redundancy for low frequency not fit for higher frequencies, as it will be shown in Section 4. The SER due to SETs can be written as:

$$SER_{SET} = \lambda_{ev} \times \frac{A_{comb}}{A_b} \times SF_{SET} \times RV_{comb}$$

(3)

where  $A_{comb}$  is the area of the combinational logic,  $A_b$  the area of the reference sequential element associated with  $\lambda_{ev}$ , and  $SF_{SET}$  is the sampling factor of SET pulses (indicating how many pulses are actually sampled by the sequential elements downstream). In [59] the overall probability of a SET being latched given a strike is 16.55% for 45 nm, 21.31% for 32 nm, 26.27% for 22 nm and 28.71% for 16 nm. We will consider a best case with  $SF_{SET} =$ 0%, an average case with  $SF_{SET} = 15\%$  and a worst case with  $SF_{SET} = 30\%$ . Also in this case we defined a  $RV_{comb}$  that keeps into account different frequency targets that will imply the choice of different combinational elements. Data from [16] show that different timing targets (e.g. 100 MHz) can increase the failure rate of combinational logic by 2x compared to the timing target minimizing the failure rate (900 MHz), when running both implementations at the same frequency (100 MHz). It should be noted that in the case of combinational logic, as opposed to sequential elements, smaller gates are more sensitive to SETs [16].

# 2.1.3. Errors in SRAM-based FPGAs

The correct behavior of processors implemented on SRAM Field Programmable Gate Arrays (FPGAs) is dependent on large configuration memories. An interesting finding in [60] is that the percentage of bit flips in the configuration memory normalized to the resource utilization (fraction of sensitive bits in the configuration memory divided by the fraction of slices utilized in the FPGA) is roughly independent from the specific IP core (ranging from around 3% to around 6%). However, the impact of soft errors on the microarchitecture is similar to those of hard errors (e.g. stuck-at [61]) and therefore they will not be included in this framework.

<sup>&</sup>lt;sup>8</sup> It is not possible to define worst cases and best cases that will be always such for each type of redundancies explored in the following sections. So as a metric to define the best, average and worst case in Table 1, the total percentage of MBUs is considered.

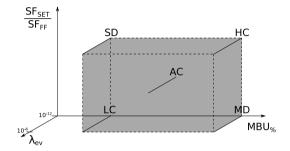

**Table 1**Error models for soft errors identified for space processors (data derived from [16,53,54,59]) for different types of technology defined in Section 2.1.4: Low Criticality (LC), Average Criticality (AC), High Criticality (HC), SET Dominated (SD) and MBU Dominated (MD).

| Technology             | LC  | AC  | HC  | SD  | MD  |

|------------------------|-----|-----|-----|-----|-----|

| SF <sub>SET%</sub>     | 0%  | 15% | 30% | 30% | 0%  |

| SF <sub>FF%</sub>      | 97% | 82% | 67% | 67% | 97% |

| SBU <sub>%</sub>       | 95% | 45% | 24% | 95% | 24% |

| $MBU(2)_{\%}$          | 4%  | 18% | 52% | 4%  | 52% |

| $MBU(3)_{\%}$          | 1%  | 10% | 3%  | 1%  | 3%  |

| $MBU (\geq 4)_{\%}$    | 0%  | 27% | 21% | 0%  | 21% |

| MBU(even) <sub>%</sub> | 4%  | 45% | 73% | 4%  | 73% |

Fig. 2. Technology space considered in this work, delimited by dashed lines. 'Edge' and 'average' technologies in black solid lines.

# 2.1.4. Model adopted

Given the discussion in previous sections, the SER of the processor will be estimated as  $SER = SER_{SEU} + SER_{SET}$ , which can be rewritten as:

$$SER = \lambda_{ev} \times N_{eq} \tag{4}$$

where  $N_{eq}$  is the number of reference sequential elements that would produce the same SER given a certain  $\lambda_{ev}$ . In our model (Eqs. (2) and (3)):

$$N_{eq} = N_{SRAM} \times RV_{SRAM} + N_{FF} \times RV_{FF} \times SV_{FF} + \frac{A_{comb}}{A_b} \times SF_{SET} \times RV_{comb}$$

(5)

Finally, the effect of the fraction of MBUs on the final failure rate will be taken into account as described in Section 3.3.3. In Table 1 the parameters of the proposed model for 5 different types of technologies are reported. These parameters describe a three-dimensional space of technologies, as shown in Fig. 2. Four of the selected technologies (LC stands for Low Criticality, MD stands for MBU Dominated, HC stands for High Criticality, and SD stands for SET Dominated) are edges of a solid in this space and one is the average case (AC stands for Average Criticality). As a matter of fact, technologies not only affect  $\lambda_{ev}$  (quantity of events), but with the relative contribution of SEUs, SETs and MBUs (quality of events) they also determine which redundancy is more effective. The rest of the edges of the solid are defined considering only a finite range of  $\lambda_{ev}$  (10<sup>-12</sup> - 10<sup>-6</sup>), defined according to average values experienced during several missions (Section 2.1.1), while considerations on extreme conditions such as worst week and worst 5 minutes in GEO will be carried out in Section 4.1.2.

# 2.2. Error propagation to the service interface

Errors generated by a fault not masked at the technology level can be masked during their propagation to the service interface (even when not considering redundancy) at the microarchitectural level (e.g. the error does not influence the behavior of the processor) and at the software level (e.g. an error which affects a bit in an unused instruction or is used only by a dynamically dead instruction<sup>9</sup>), as shown in Fig. 3. When the error is masked, the application terminates normally and output pins (and files) do not differ from the fault-free execution.<sup>10</sup>

When redundancy is employed, along with the intrinsic microarchitectural and software masking, error detection and handling are also possible. The capability of a processor to avoid an error to turn into a failure is referred to as "fault tolerance" [10]. The possible outcomes of error detection and handling are:

- Correctable error: the error detection and handling mechanism proceeds to correct the error (correction). However, when more errors than expected are present, the correction can be wrong (miscorrection [64]).

- Detected Uncorrectable Error (DUE): the error detection and handling mechanism is able to detect the error and to prevent it from propagating to the service interface [65]. The reaction to a detected DUE (e.g. rollback) may cause penalties in terms of availability.

- Unexpected Termination (UT): its effect on the error propagation is the same as a DUE, but it is typically caused by the Operating System (OS) and software [66] instead of hardware. For instance, a process may terminate abnormally thanks to built-in protections (memory access violation, kernel panic, and arithmetic exception) triggered by an anomalous behavior [67].

- Undetected: in this case the redundancy employed fails at detecting the error during its propagation and no action is taken.

# 2.3. Service interface and error tolerance

The system service defines the service interface at which the service is to be provided and which outputs of the software (e.g. variables directly mapped to a failure) and hardware (e.g. signals to other subsystems) will be able of propagating the errors. An error, when propagated to the service interface, can generate wrong data, wrong commands or unavailability of the system (Fig. 3). The unavailable state can be expanded in a case where the unavailability is due to the intrinsic vulnerability of the processor (i.e. hang) and a case where it is due to error handling.

# 2.3.1. Intrinsic error tolerance

In many works, wrong data and wrong commands on the output are both assumed to be a failure, calling this Silent Data Corruption (following the terminology of [65]). However, this is not always the case, as some services are inherently tolerant to wrong data at the service interface. In [68] a system is defined as error tolerant with respect to a service, if the system produces acceptable results to the end user according to a certain Quality of Service (QoS) even when errors are propagated to the outputs of the system. The system fails due to insufficient QoS instead when the QoS is below a certain threshold (QoSthr). For instance, in a system providing edge detection for images, the QoS is defined in [69] as the peak Signal-to-Noise Ratio (SNR) when comparing the corrupted and correct images and the QoSthr is set to 10 dB. More complex services have a more complex definition of acceptable quality. For instance, in Moving Picture Experts Group (MPEG) encoding there are three types of frames: *I* frames,

<sup>&</sup>lt;sup>9</sup> A dynamically dead instruction is an instruction which outputs are not used by any other instructions and that does not actually influence the output of the processor [62].

<sup>&</sup>lt;sup>10</sup> In [63], masked cases are instead classified in two different categories depending on whether the final architectural status is different from a fault-free execution (referred to as *Output Not Affected*) and those where it is the same (referred to as *Vanished*).

Fig. 3. Propagation of errors to the service interface and effects on the system service.

*P* frames and *B* frames [69]. In general, the loss of *B* and *P* frames can be compensated by the decoder, while the loss of an I frame will result in a substantial quality degradation. In [69] a frame is considered bad if the SNR (compared to the correct frame) is more than 2 dB for I frames, 4 dB for P frames and 6 dB for B frames. The OoS in [69] is then defined as the percentage of good frames and QoS<sub>thr</sub> is then set to 10% of bad frames. An example of even more complex service is inference for image classification. In this case the QoSthr is defined as the difference in confidence of the top ranked element compared to the top ranked element of the faultfree execution [70]. In addition, the concept of OoS is introduced also for the catastrophic failures, which in this case is when the top ranked element differs from the golden execution. As a matter of fact, a differentiation is done between the case where the top ranked element is at least a 'good candidate' (i.e. one of the first 5) in the fault-free execution and the opposite case.

In [69] it is shown that in order to fully exploit the concept of error-tolerance, control operations (defined as those which can change the control flow in the software and therefore potentially generate wrong commands at the outputs) must be identified and protected. As a matter of fact, catastrophic failures are avoided both for Susan (edge detection) and MPEG (MPEG encoding) when errors are not injected in control operations (while some other benchmarks have catastrophic failure rates up to 19% even when errors are not injected in control operations). When control operations are protected, more than 100 errors per second had to be injected in Susan to show any frame loss due to the SNR being too low. MPEG had instead about 2% loss at 10 errors per second. Both error rates are pessimistic for space, as the error rate in this case is several order of magnitude lower (in Section 3.2 the maximum SER found is around three errors per day at the highest upset rate considered). MPEG crashes disabling protection for control operation, while for Susan disabling protection leads to very poor fidelity of output. This can be attributed to the relatively small number of control instructions (less than 9%) in Susan compared to the higher percentage in MPEG (around 50%) [69].

# 2.3.2. Explicit error tolerance

Once models of failures at the service interface are defined, explicit techniques of error tolerance can be employed. One of the most commonly used is the watchdog timer, namely a counter that if not periodically reset by the processor will reset the processor itself [71]. This is represented in Fig. 3 with *Timeout* and it is based on the simple model of *Hang* of the processor at the service interface. However more complex models can be employed, and in [71] also a smart watchdog is proposed. Similarly, in [72] a symptom-based mechanism is employed to reduce the failure rate by 20x over a baseline design without explicit error tolerance.

# 3. Modeling the vulnerability of processors

Once the models for the threats are defined, the following step is to build a model to identify the most vulnerable parts of the design. A common model in literature is the Architectural Vulnerability Factor (AVF) decomposition [41].

# 3.1. AVF decomposition

In order to take into account the masking effects due to software and microarchitecture, in [73] the AVF of a unit is defined as the probability that a fault in that unit of the processor will cause a failure at the outputs of the processor. For this reason, the AVF depends on which event of those described in Section 2.3 are considered as failures. In this work, we will use the definitions of failures as indicated in Fig. 3 (at the service interface).

The rate of occurrence of a failure f for the unit i can be modeled as  $\lambda_{i,f} = SER_i \times AVF_{i,f}$ . In order to have a correct execution, all the units of the AVF decomposition are required to not propagate an error to the outputs of the processor. As a result, units in an AVF decomposition can be thought as a series of components in a reliability block diagram [41]. Assuming that the masking is uniform (therefore not changing the distribution of events) and assuming that failures in different components are independent of each other, the total reliability is given by the product of the reliability of the units composing the processor. The processor-level failure rate for the failure f  $\lambda_f$  is then given by:

$$\lambda_f = \sum_{i} SER_i \times AVF_{i,f} = SER \times AVF_f \tag{6}$$

As  $SER = \lambda_{ev} \times N_{eq}$ , the effects of failures on a service for space applications (relatively high  $\lambda_{ev}$  and low  $N_{eq}$ ) can be sometimes compared to the effects on services for application with lower  $\lambda_{ev}$  and higher  $N_{eq}$  (e.g. servers) [41]. Eq. (6) can also be written as  $\lambda_f = \lambda_{ev} \sum_i \hat{\lambda}_{i,f}$ , where  $\hat{\lambda}_{i,f} = N_i \times AVF_{i,f}$  is the failure rate normalized to the upset rate per bit. For failures causing wrong outputs or data, the failure rate  $\lambda_w$  (Fig. 3) is enough to estimate their effect on the service. <sup>11</sup>

The impact on the service interface of failures causing unavailability  $^{12}$  instead is also determined by the duration of the unavailability  $T_{u,i}$  they cause each time they manifest. Different types of events causing unavailability can be observed:

- Timeout (λ<sub>h</sub>): these events are due to residual AVF<sub>u</sub> not protected by redundancy. We assume they are addressed employing a watchdog timer that triggers a hard reset (power cycle) when it expires. An order of magnitude for T<sub>u,h</sub> can be found in [74], where it is assumed to last 5 min, as extensive checking (e.g. memory) is required.

- UT ( $\lambda_{eh,ut}$ ): when a process is terminated, a possible solution is to use an interrupt service routine for diagnostic and restart of the process. These have typically lower impact than a reset. The work in [75] shows that a process can be restarted with a latency on the order of 10 ms.

$<sup>^{11}</sup>$  Sometimes, instead of the failure rate, the Mean Time To Failure (MTTF) is employed to indicate how often a failure will happen on average. The use of an exponential reliability function simplifies further the calculations, as  $MTTF_w = 1/\lambda_w$ .

<sup>12</sup> If a system is unavailable for a total  $T_{Unavailable}$  during a certain  $T_{Mission}$ , the unavailability is then defined as  $U = \frac{T_{Unavailable}}{T_{Mission}}$  and the availability as Availability = 1 - U.

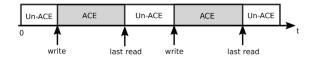

**Fig. 4.** Fraction of time a location in the RF is in ACE (gray) and un-ACE (white). Between *write* and *last read* an arbitrary number of reads can happen.

- DUE in data without valid copies (\(\lambda\_{eh,hr}\)): in this case, e.g. errors in Write-Back (WB) caches, a DUE requires at least a soft reset (i.e. ending the current processes and booting again). From the work in [76], a penalty of 45 s can be assumed for a soft reset, composed of end time and boot time.

- Rollback to an up-do-date value ( $\lambda_{eh,rb}$ ): when the corrupted data is available in the most up-to-date value, the loss in terms of availability is minimal. For instance, in case of a DUE in a Level 1 (L1) cache with Write-Through (WT) policy the data can be read from the Level 2 Cache (L2C), with a penalty of a cache miss [77]. As can be seen in [77], 150 Clock Cycles (CCs) can be taken as a pessimistic estimation for a cache miss and even in this case, assuming a clock frequency of 100 MHz, the penalty is in the order of microseconds (which is in most cases negligible).

- Correction ( $\lambda_{eh,c}$ ): the latency in this case is very short. For instance, the LEON2FT checks the EDAC code on the Register File (RF) during the execution phase, writes back errors in the RF with the correct value, flushes the pipeline and restarts from the instruction that reads the operand with the error [78]. This procedure causes typically minimum penalty in terms of stalling (in this case just 5 CCs).

- Device-specific rollback ( $\lambda_{eh,ds}$ ): some devices save the old status to rollback to it in case of DUE [79] or they compare the output of three processors and restore the correct status from one of the golden replica [20]. In these cases the penalty in terms of availability is implementation-specific. We will discuss this aspect further in Section 4.

The unavailability due to each type of these events i can be expressed as:

$$U_{i} = \frac{N_{u,i} \times T_{u,i}}{T_{Mission}} = \frac{(T_{Mission} \times \lambda_{u,i}) \times T_{u,i}}{T_{Mission}}$$

(7)

where  $N_{u,i}$  is the number of times the events i happened during the mission and  $T_{Mission}$  is the total mission time. Therefore, the unavailability of the processor considering all the possible sources i of unavailability is:

$$U = T_{u,h} \times \lambda_h + \sum_i T_{u,eh,i} \times \lambda_{eh,i} = \lambda_{ev} \times \hat{U}$$

(8)

#### 3.1.1. Vulnerability in time: ACE analysis

More insights can be gained on the meaning of the AVF by considering how AVF is estimated in [73], i.e. considering the bits required for an Architecturally Correct Execution (ACE). A bit is an ACE-bit when changing its value will cause the error to propagate to the service interface and it is an un-ACE bit otherwise. A bit typically changes from ACE to un-ACE and vice versa during program execution, as shown in Fig. 4 for a bit in a location of the RF.

At any instant in time, the AVF can be expressed as the number of ACE bits in a structure  $N_{ACE_i}$  over the total number of bits in the structure  $N_i$ :  $AVF_i(t) = \frac{N_{ACE_i}(t)}{N_i}$ . The average AVF can then be defined as the average number of ACE-bits in a certain timespan. Using Little's law [73], the average number of ACE-bits within a structure (e.g., instruction buffer or execution unit) can be written

**Table 2**Features of the cache subsystem common to LE and HE (data derived from [82]). 'Pref.' stands for 'prefetcher'.

| Unit | Size   | Block size | Associativity | Policy    | Prefetching  |

|------|--------|------------|---------------|-----------|--------------|

| DC   | 32 KiB | 64B        | 4-way         | WB        | Stride pref. |

| IC   | 32 KiB | 64B        | 4-way         | Read-only | Pref.        |

| L2C  | 1 MiB  | 64B        | 16-way        | WB        | w/o pref.    |

as the product of the arrival rate (bandwidth  $B_{ACE_i}$ ) of ACE bits and the average time of persistence in the structure (latency  $L_i$ ):

$$AVF_i = \frac{N_{ACE_i}}{N_i} = \frac{B_{ACE_i} \times L_i}{N_i} \tag{9}$$

For instance, when considering hardware structures storing or executing instructions, the rate of arrival of ACE bits is given by the number of Instructions Per (clock) Cycle (IPC). The average time these bits spend in the structure depends on the functionality of the block, which may store it for a long time (e.g. memory or buffers) leading to high AVFs or for shorter times (execution units) leading to lower AVF. Furthermore, for functional units like Arithmetic Logic Units (ALU), Eq. (9) shows that the more frequently they are used and the longer is the latency of the operation, the more vulnerable they are. For memories, it shows that the longer the average lifetime and the higher the memory utilization, the higher the AVF is.

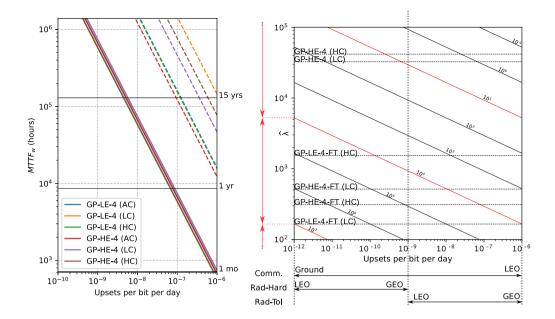

# 3.2. Impact of the microarchitecture on the failure rate

In [7] the authors provided an overview on RISC-V and proposed how to employ the RISC-V ISA in space data systems to address present and future needs. In this roadmap, several 'profiles' of processors were proposed. Here we will analyze four General Purpose (GP) profiles from the point of view of dependability as case studies for our models: GP-LE-1, GP-LE-4, GP-HE-1 and GP-HE-4.<sup>13</sup> The LE-4 can be seen as an implementation equivalent to the state of the art of space-grade components (single-issue, in-order pipeline, quad-core like the GR740 [2]), while the HE-4 can be seen as a possible future space-grade processor. These configuration will be represented by the Rocket (LE) and the BOOM processor (HE) where FI was carried out in [67]. Therefore, for units in Tables 3 and 4 we use values for AVFs from [67]. However, to provide a more comprehensive comparison of the contribution of each block in a realistic design, we also include estimations for one L1 Instruction Cache (IC) per core, one Data Cache (DC) per core, one FPU per core and L2C (one shared among the cores in LE-4 and HE-4). For the Floating Register File (FRF) we use as a pessimistic estimation the same value of the Integer Register File (IRF) of the Rocket, as data from [80] shows for FRF similar contribution to the failure rate compared to the IRF. When considering the functional part of the Floating Point Unit (FPU), [81] shows that in average (over different benchmarks) only 1.76% of errors in FPUs reach the FPU output.<sup>14</sup> For all the profiles we use the same cache configuration, i.e. the baseline of [82] that is reported in Table 2 and

<sup>13</sup> As defined in [7], "LE" stands for Low-End and "HE" stands for High-End. The following digit indicates the number of cores. In the remainder of this paper, "GP" is usually omitted as only GP processors are considered.

$<sup>^{14}</sup>$  Further data shows that AVF for control modules in the FPU is 8.9% while datapath modules have a 1.43%. The large percentage of area dedicated to the datapath in a FPU explains the low average value. Also, this is a pessimistic estimation for the AVF of a FPU in a processor as the service interface is taken at the output of the FPU and not at the output of the processor, thus neglecting the masking effect of the rest of the processor to errors coming from the FPU. These data do not differentiate between types of failure so we assume that the breakdown is similar to the one of the Arithmetic-Logic Unit (ALU) in the HE-1 in terms of  $\mbox{AVF}_{\rm w}$ ,  $\mbox{AVF}_{\rm h}$  and  $\mbox{AVF}_{\rm chut}$ .

**Table 3**AVF (from [67,80,81]) and N<sub>eq</sub> for LE-1 (without caches), decomposed in IRF, Multiplier and Divider (M/D), Instruction Buffer (IB), rest of the Integer Unit (IU), Control and Status Registers (CSR), FRF and FPU.

| LE-1             | IRF       | M/D       | IB       | IU       | CSR      | FRF      | FPU      |

|------------------|-----------|-----------|----------|----------|----------|----------|----------|

| AVF <sub>w</sub> | 3.3%      | 0.2%      | 0.5%     | 2.4%     | 5.9%     | 3.3%     | 1.0%     |

| $AVF_h$          | 1.0%      | 0.1%      | 0.3%     | 4.4%     | 8.2%     | 1.0%     | 0.2%     |

| $AVF_{eh,ut}$    | 12.2%     | 0.4%      | 1.1%     | 4.9%     | 4.3%     | 12.2%    | 0.6%     |

| $N_{eq,LC}$      | 2.65E + 3 | 2.17E + 2 | 9.9E + 1 | 1.1E+3   | 1.2E + 3 | 2.8E + 3 | 1.6E + 3 |

| $N_{eq,AC}$      | 2.65E + 3 | 5.72E + 2 | 1.4E + 2 | 1.7E+3   | 1.4E + 3 | 2.8E + 3 | 5.0E + 3 |

| $N_{eq,HC}$      | 2.65E + 3 | 9.27E + 2 | 1.8E + 2 | 2.2E + 3 | 1.6E + 3 | 2.8E + 3 | 8.5E + 3 |

**Table 4**AVF (from [67,80,81]) and N<sub>eq</sub> for HE-1 (without caches), decomposed in IRF, Register Rename (RR), Instruction Fetch (IF), Instruction Issue (II), Load and Store Unit (LSU), ReOrder Buffer (ROB), BP, ALU, CSR, FRF and FPU.

| HE-1             | IRF      | RR       | IF       | II       | LSU      | ROB      | BP       | ALU      | CSR      | FRF      | FPU      |

|------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| AVF <sub>w</sub> | 1.9%     | 2.4%     | 2.6%     | 2.4%     | 1.5%     | 1.2%     | 0.8%     | 1.2%     | 3.9%     | 3.3%     | 1.0%     |

| $AVF_h$          | 1.0%     | 3.3%     | 1.0%     | 3.1%     | 2.4%     | 2.4%     | 1.5%     | 0.4%     | 0.2%     | 1.0%     | 0.2%     |

| $AVF_{eh,ut}$    | 8.7%     | 5.7%     | 7.3%     | 0.9%     | 3.7%     | 0.8%     | 0.1%     | 0.7%     | 5.4%     | 8.7%     | 0.6%     |

| $N_{eq,LC}$      | 4.5E + 3 | 2.9E + 3 | 4.1E + 3 | 7.1E + 2 | 2.1E + 3 | 1.1E + 3 | 2.8E + 3 | 1.9E + 3 | 1.3E + 3 | 3.4E + 3 | 4.8E + 3 |

| $N_{eq,AC}$      | 6.4E + 3 | 4.1E + 3 | 5.6E + 3 | 9.8E + 2 | 2.6E + 3 | 1.2E + 3 | 3.0E + 3 | 3.7E + 3 | 1.5E + 3 | 4.3E + 3 | 7.5E + 3 |

| $N_{eq,HC}$      | 8.4E + 3 | 5.2E + 3 | 7.1E + 3 | 1.2E + 3 | 3.1E + 3 | 1.4E + 3 | 3.1E + 3 | 5.5E + 3 | 1.8E + 3 | 5.1E + 3 | 1.0E + 4 |

**Table 5** AVF (from [82]) and  $N_{eq}$  (the same for all technologies) for caches. LE-1 and HE-1 have one DC and one IC each. LE-4 and HE-4 are obtained replicating 4 times the respective single-core version and adding a L2C.

| Caches           | DC <sub>WT</sub> | DC <sub>WB</sub> | IC     | L2C <sub>WB</sub> |

|------------------|------------------|------------------|--------|-------------------|

| AVF <sub>w</sub> | 5%               | 8.8%             | 0.5%   | 0.5%              |

| $AVF_h$          | 1.3%             | 2.5%             | 5%     | 0.6%              |

| $AVF_{eh,ut}$    | 2.9%             | 4.3%             | 5.2%   | 1.7%              |

| N <sub>eq</sub>  | 5.14E+4          | 5.7E+2           | 2.0E+5 | 2.4E+6            |

with AVF values reported in Table 5. This will provide the reader with an estimation of how the same size of caches influences the failure rate in different designs (even if higher performance processors may employ larger caches). However, in Section 3.2.1 we will also provide models and considerations on scaling of cache size. For simplicity, in this section we will consider only data arrays and not tag arrays in caches. Even if tag arrays in [83] are reported to be have higher AVF than data arrays 15 (as for instance they have on average an AVF 2.76x higher than data arrays in DC), they typically are smaller (around 7 KiB, i.e. around 9 times smaller than the data array). Therefore, not including tag bits in the model can be expected to underestimate the vulnerability of caches by around 20% according to Eq. (6). Furthermore, using values for caches of a processor with a different ISA does not impact AVF of caches in a significant way, as in [84] the AVF of caches for two different ISAs (ARM and x86) for 10 MiBench benchmarks shows that the difference is small. 10

Furthermore, we assume same average values of AVF for single and quad-core versions of the same design. As a matter of fact, [85] investigates the changes in AVF in a dual-core processor where each core is running a different thread and it shows that AVF is roughly the same compared to a single core (the change in AVF is within a  $\pm 1/2$ % of the AVF single core value).

Estimations of  $N_{eq}$  are obtained with syntheses on Design Compiler on a 65 nm bulk commercial technology targeting 100 MHz and using the code available to the public of the Rocket processor<sup>17</sup> and of the BOOM processor.<sup>18</sup> However, as we do not have access to the memory compiler of the ASIC technology (as it is often the case), we will estimate the size of caches using CACTI [86].

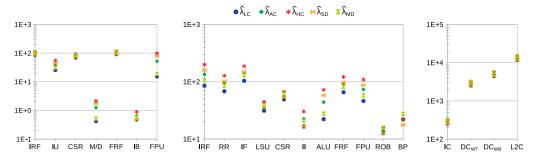

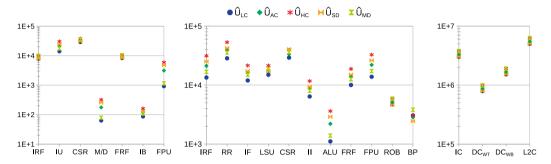

It can be noted from Figs. 5 and 6 that caches are the most vulnerable units in processors, even considering technologies with high SER from combinational logic. This was already shown in [87] with a less refined model. Most of the units have a similar relative contribution to  $\lambda_{\it w}$  and U, except the IC which has a similar impact compared to L2C in terms of unavailability but lags behind more than a order of magnitude in terms of  $\lambda_m$ . Most of the units increase their failure rate when moving from LC to SD. However, for a few of those (those with higher percentage of sequential elements like BP), the failure rate decreases due to FF temporal masking (as shown in [16]). Furthermore, microarchitectures impact the failure rate much more in terms of  $N_{eq}$ than in terms of AVF. As a matter of fact, the maximum ratio between two different designs in terms of  $N_{eq}$  with the same type of technology defined in this section (cacheless LE-1 and the HE-4) is around 100 for each technology, while the maximum ratio of AVFs found in literature due to different microarchitectures is around 4x (in [88]).

# 3.2.1. Design explorations

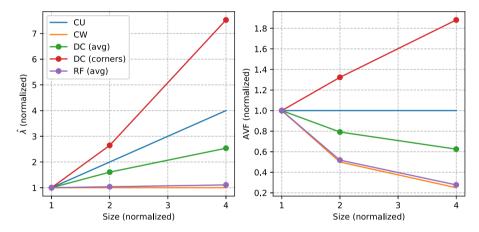

In [89] the effect of the processor width and of the number of functional units (e.g ALU and FPU) on the AVF of the functional units is investigated but no clear correlation is found. Looking at data from the literature for IRF and caches (e.g. [82]), we define two models of scaling of the failure rate for an array of sequential elements based on Eq. (9), as shown in Fig. 7:

- Constant Workload (CW): the workload for the array remains constant while increasing the size of the unit, meaning that the failure rate remains constant and the AVF decreases by the same factor as the size was increased.

- Constant Utilization (CU): the relative utilization of the array remains constant while increasing the size of the array, meaning that the AVF remains the same and the failure rate increases of the same amount the size was increased.

As shown in Fig. 7 some units show a behavior similar to CW (e.g. physical register), some lay in between CU and CW (DC on

<sup>15</sup> Also [19] shows a high value for tag arrays (32.5%).

$<sup>^{16}</sup>$  Intuitively, this is more true for L2C (-4%) and DC (+5%), while the difference is slightly larger for ICs (+24%), which store ISA-specific instructions [84].

<sup>17</sup> https://github.com/chipsalliance/rocket-chip.git.

<sup>18</sup> https://github.com/riscv-boom/boom-template.git.

Fig. 5. Normalized failure rate for wrong outputs  $\hat{\lambda}_w$  for LE-1 (cacheless), HE-1 (cacheless) and caches (from left to right). Calculations based on Eq. (6).

Fig. 6. Normalized unavailability  $\hat{U}$  for LE-1 (cacheless), HE-1 (cacheless) and caches (from left to right). Calculations based on Eq. (8).

Fig. 7. Effects of size on  $\hat{\lambda}$  (normalized to the  $\hat{\lambda}$  of the smallest size considered) and AVF for 2x and 4x increases (based on [82]).

average and IC for all benchmarks from [82]) and some other units increase their utilization when their size is increased (DC for the *corners* benchmark in [82]) and in this case we talk about "superlinear" behavior (as done in [90]).

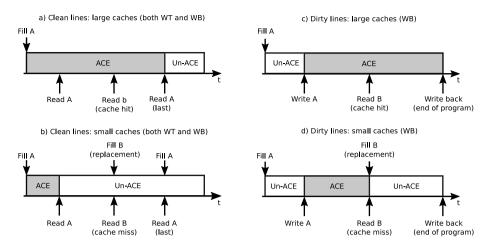

The results in [91] confirm the increase of failure rate of the DC when increasing its size. However, in this case the behavior shown is superlinear (and not in between CW and CU), as increasing its size of 16x (from 16 KiB to 256 KiB) increases its failure rate by 21x. Interestingly, they also show that increasing the size of DC by 16x has an effect on the failure rate of L2, which decreases by around 2x. The work in [92] highlights how cache arrays typically exhibit a superlinear behavior when the cache hit rate increases with the increase of the size (e.g. for the FFT and matrix multiplication benchmarks), while if the cache hit rate remain constant they typically show a CW behavior. An explanation for this is presented in [90] and reported in Fig. 8 (left). Let us consider a program that reads the variable A, then the variable B and then again the variable A. In a large cache, it is more likely that both A and B will reside in the cache. For this reason reading B does not cause a cache miss and line A is not evicted. In a small cache instead, reading *B* is more likely to cause a cache miss and a replacement of *A* with *B*, thus reducing drastically the fraction of time the location stores ACE-bits. The mechanism described happens for both WT and WB policies, while in Fig. 8 (right) it is also shown a mechanism specific of WB caches. As a matter of fact, in WB caches dirty lines also exist and those are always ACE, as they will be eventually written back to main memory. Fig. 8 (right) shows a program which writes *A* and then reads *B* and then does not act on the location until the end of the program, when the dirty lines will be written back. Also in this case, a small cache which substitute *A* with *B* can reduce the fraction of time the location stores ACE-bits considerably.

The previous discussion shows also that the write policy influences the AVF of the L2C: in [82] a value of 7% can be taken for a WB L2 cache (in [84] a similar value is given) and 4.2% for a WT L2C (1 MiB), which implies almost double the SER due to the L2C.

Furthermore, as show in [82], the AVF of the DC is roughly insensitive to the associativity (5 benchmarks out of 8), while some benchmarks (*dipeg* and *smooth*) exhibit a steep variation

Fig. 8. Examples of superlinear behavior for a location in DC storing the variable A, similarly to [90].

of AVF for a specific number of ways, and only one (*search*) shows an increase of AVF with the number of ways. IC instead decreases its AVF when the number of ways is increased [82]. Adding prefetches to the DC leaves substantially unchanged the AVF, while removing prefetchers for IC reduces the AVF, which becomes, on average, 0.67x the baseline AVF [82].

# 3.3. Impact of other factors on the failure rate

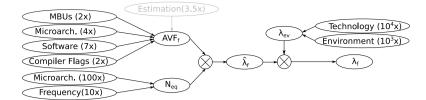

Several factors impact the failure rate. Fig. 9 summarizes these factors indicating how large is the maximum value compared to the minimum value found of the failure rate when varying a certain factor. The impact of technology (and of the environment) and of microarchitecture was already assessed in Sections 2.1 and 3.2 respectively. The remainder of this subsection quantifies the impacts of other factors.

# 3.3.1. Dependence on performance and compiler flags

The work in [93] observes a fuzzy correlation between AVF and each performance metric considered (i.e. IPC, branch prediction rate and several cache miss rates) across several SPEC2000 benchmarks. However, in [94] the use of performance throttling is proposed to lower the overall AVF of a processor. Acting both on pipeline resources and cache miss rate, a failure rate reduction up to 35% is achieved.

Another way to change performance is to employ specific compiler flags. In [95], GCC with several combinations of optimization flags for the MiBench benchmark suite are compared in terms of performance and AVF. It is shown that the optimal set of flags for AVF decreases the AVF by around 9% compared to -03 and of 8% compared to -02. Among the optimization levels, in [96] -Os is found to be better than the -00 for around 75% of the benchmarks (on a total of 25 benchmarks considered), while the lowest AVF in average is obtained with -02. Recent work [97] shows that the ratio of the AVF obtained with the worst and best sets of optimization flags is around 2x.

#### 3.3.2. Dependence on software

Error masking in a processor, like performance, depends on the software employed. For this reason, it is crucial that the set of programs employed during the estimation of the AVF is representative of the final application or is general enough to represent a wide spectrum of applications. Most works in literature use the SPEC benchmark suites [67,88], others use EEMBC suites [80] and others MiBench [82,95] for its similarities to the SPEC benchmarks in terms for instance of instruction mix. As a matter of fact, instruction mix of the software can have a significant impact on

the failure rate of certain units of the processor. For instance, data from [98] show that moving from benchmarks with low fraction of FPU instructions like *AMG2006* and *UMT* (0.03 and 0.1 per CC) to those with high fraction of FPU instructions like *LINPACK* (0.64 per CC) increases the failure rate of the FRF by 50x.