#### **RF CMOS Oscillators for Cellular Applications**

Shahmohammadi, Mina

10.4233/uuid:f7b33aaa-6b21-4f8a-9fd7-022bec55f114

**Publication date**

**Document Version** Final published version

Citation (APA)

Shahmohammadi, M. (2016). RF CMOS Oscillators for Cellular Applications. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:f7b33aaa-6b21-4f8a-9fd7-022bec55f114

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# RF CMOS Oscillators for Cellular Applications

Mina Shahmohammadi

# RF CMOS Oscillators for Cellular Applications

#### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben; voorzitter van het College voor Promoties, in het openbaar te verdedigen op

donderdag 1 december 2016 om 12.30 uur

door

Mina SHAHMOHAMMADI

Master of Science in Electrical Engineering, University of Tehran, Tehran, Iran geboren te Teheran, Iran This dissertation has been approved by the

promotor: Prof. dr. R. B. Staszewski

Composition of the doctoral committee:

Rector Magnificus chairman

Prof. dr. R. B. Staszewski Delft University of Technology

#### Independent members:

Prof. dr. ing L. C. N. de Vreede Delft University of Technology

Dr. M. Spirito Delft University of Technology

Prof. dr. ir. F. E. van Vliet University of Twente

Prof. dr. ir. A. H. M. van Roermund Eindhoven University of Technology

Prof. dr. ing. S. Heinen RWTH Aachen University, Germany

Prof. dr. P. Wambacq Vrije Universiteit Brussel, Belgium

Prof.dr. ir. A. Neto Delft University of Technology, reserve member

Mina Shahmohammadi,

RF CMOS Oscillators for Cellular Applications,

Ph.D. Thesis Delft University of Technology,

Keywords: RF, oscillator, 1/f noise up-conversion, impulse sensitivity function, wide tuning range, Colpitts oscillator, coupled oscillators, all-digital phase-locked loop (ADPLL).

ISBN 978-94-6233-477-9

Copyright © 2016 by Mina Shahmohammadi

Cover photo was taken from www.bgfons.com.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed in the Netherlands.

To Maman, Babajan, Mohammad and Kaveh

And to my dearest Masoud

# Contents

| C | ontei         | nts     |                                          | j  |

|---|---------------|---------|------------------------------------------|----|

| 1 | Inti          | oducti  | ion                                      | 1  |

|   | 1.1           | Thesis  | s Objectives                             | 3  |

|   | 1.2           | Thesis  | S Outline                                | 4  |

| 2 | $\mathbf{LC}$ | Oscilla | ator Structures                          | 9  |

|   | 2.1           | Introd  | luction                                  | 9  |

|   | 2.2           | Class-  | B Oscillator Topology                    | 12 |

|   | 2.3           | Class-  | C Oscillator Topology                    | 15 |

|   | 2.4           | Class-  | D Oscillator Topology                    | 16 |

|   | 2.5           | Class-  | F Oscillator Topologies                  | 18 |

|   |               | 2.5.1   | Class- $F_3$ Topology                    | 19 |

|   |               | 2.5.2   | Class- $F_2$ Topology                    | 20 |

|   | 2.6           | Concl   | usion                                    | 21 |

| 3 | <b>A</b> 1    | /f Noi  | se Up-Conversion Reduction Technique     | 27 |

|   | 3.1           | Introd  | luction                                  | 28 |

|   | 3.2           | Metho   | od to Reduce 1/f Noise Up-Conversion     | 31 |

|   |               | 3.2.1   | Auxiliary Resonant Frequencies           | 31 |

|   |               | 3.2.2   | Harmonic Effects on the Effective ISF    | 32 |

|   |               | 3.2.3   | Resonant Frequency at $2\omega_0$        | 37 |

|   |               | 3.2.4   | $\omega_{CM}$ Deviation from $2\omega_0$ | 38 |

|   | 3.3           | Circui  | it Implementation                        | 40 |

|   |               | 3.3.1   |                                          | 44 |

|   |               | 3.3.2   | Class- $D/F_2$ Oscillator                | 45 |

ii Contents

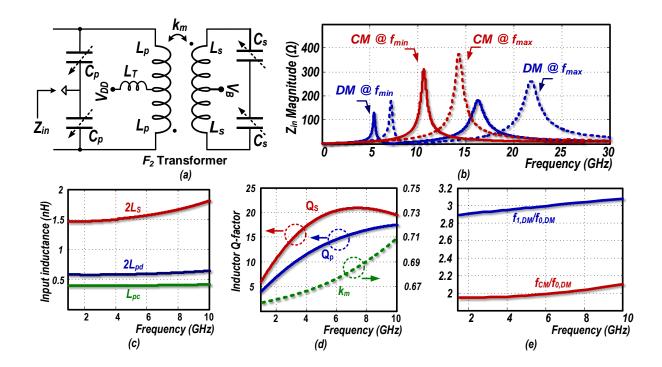

|    |                        | 3.3.3        | Transformer-Based $F_2$ Tank                                                                                                                   | 47  |

|----|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |                        | 3.3.4        | Class- $F_{2,3}$ Oscillator                                                                                                                    | 48  |

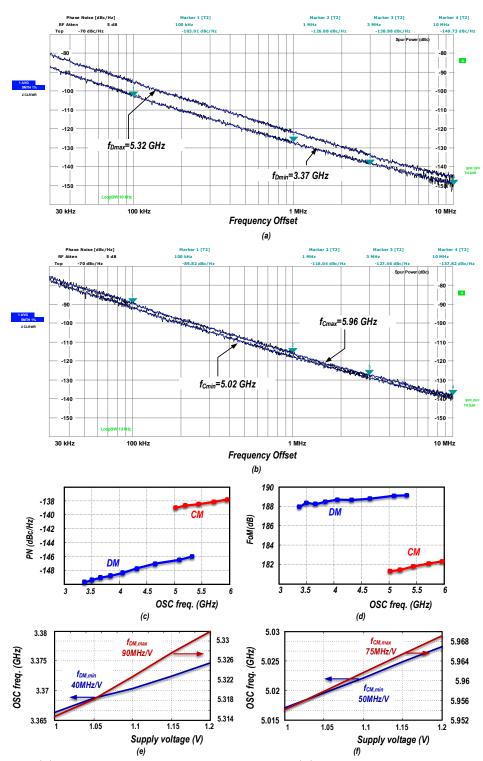

|    | 3.4                    | Experi       | mental Results                                                                                                                                 | 50  |

|    |                        | 3.4.1        | Class- $D/F_2$ Oscillator                                                                                                                      | 51  |

|    |                        | 3.4.2        | Class- $F_{2,3}$ Oscillator                                                                                                                    | 53  |

|    | 3.5                    | Conclu       | sion                                                                                                                                           | 54  |

| 4  | A V                    | ${f Vide-T}$ | uning-Range DTC-Assisted Fractional-N All-digital PLL                                                                                          | 61  |

|    | 4.1                    | Introd       | $\operatorname{uction}$                                                                                                                        | 62  |

|    | 4.2                    | Struct       | ure of the ADPLL                                                                                                                               | 64  |

|    | 4.3                    | Circuit      | Implementation                                                                                                                                 | 66  |

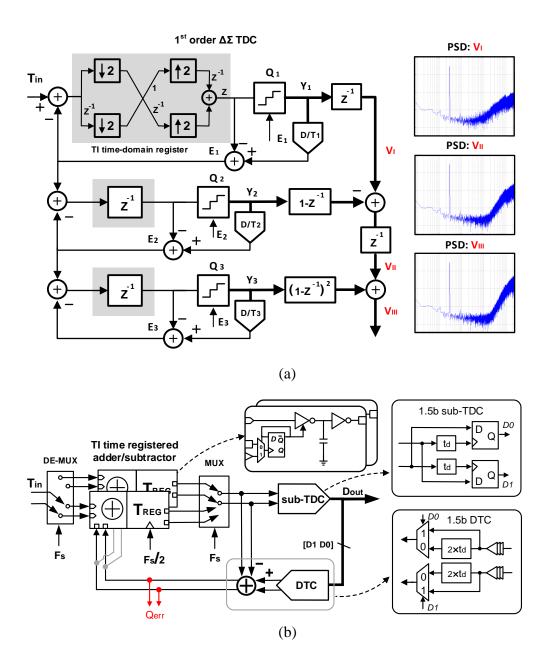

|    |                        | 4.3.1        | Implementation of MASH $\Delta\Sigma$ TDC                                                                                                      | 66  |

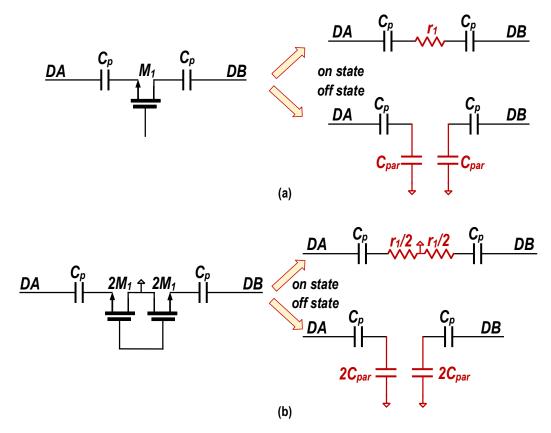

|    |                        | 4.3.2        | Implementation of Wide Tuning-Range DCO                                                                                                        | 67  |

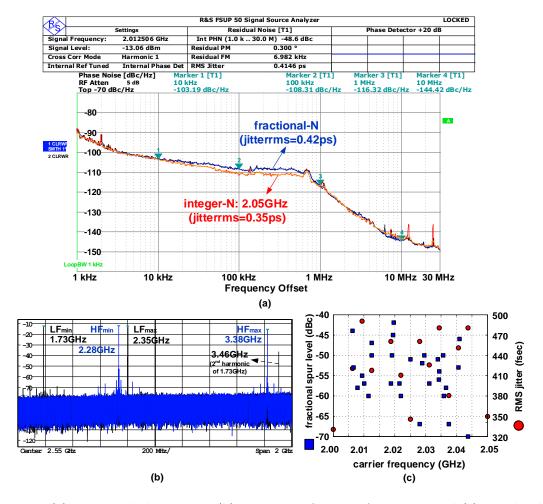

|    | 4.4                    | ADPL         | L Measurements Results                                                                                                                         | 73  |

|    | 4.5                    | Conclu       | sion                                                                                                                                           | 75  |

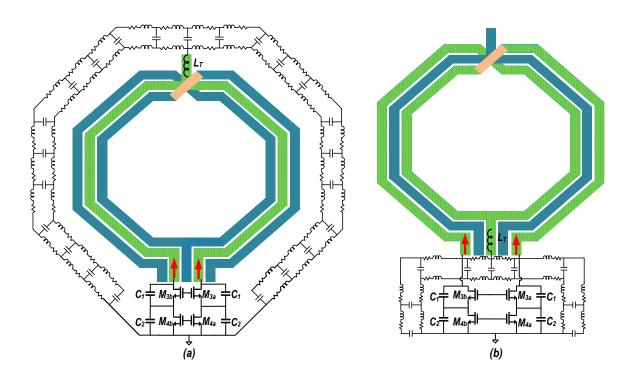

| 5  | Tun                    | ing rai      | nge extension of an oscillator through CM resonance                                                                                            | 79  |

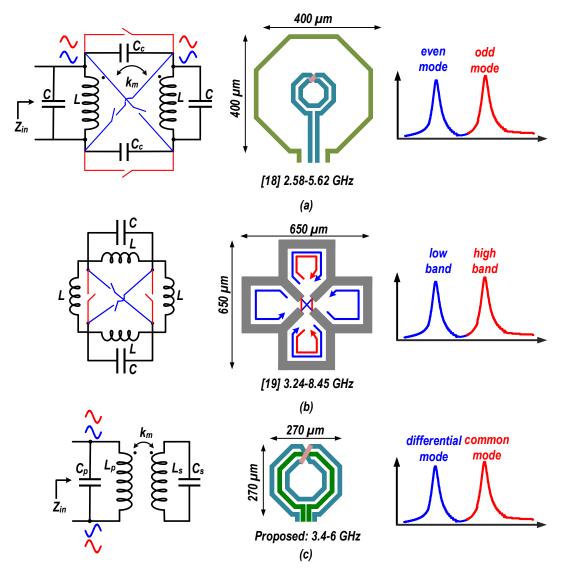

|    | 5.1                    | Introd       | $ uction \ldots \ldots$ | 80  |

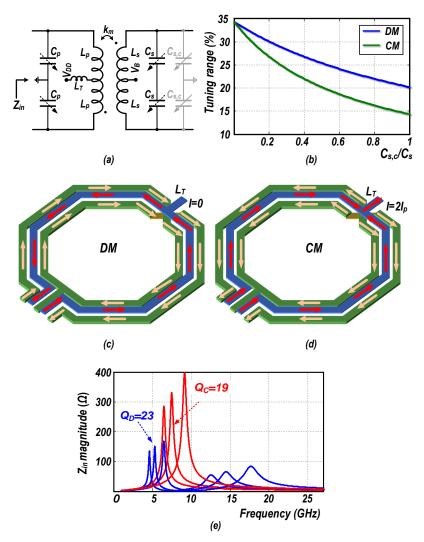

|    | 5.2                    | Comm         | on Mode Resonances                                                                                                                             | 82  |

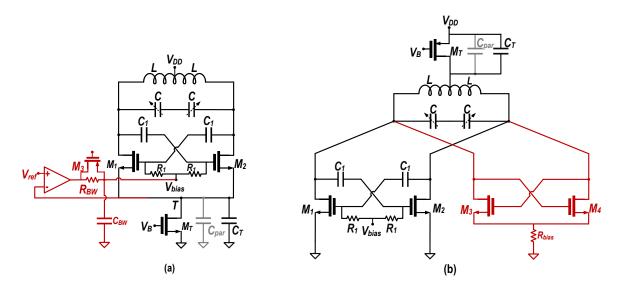

|    | 5.3                    | Propos       | sed Wide Tuning Range Oscillator                                                                                                               | 86  |

|    |                        | 5.3.1        | Dual-Core Oscillator                                                                                                                           | 86  |

|    |                        | 5.3.2        | Phase Noise Analysis                                                                                                                           | 88  |

|    |                        | 5.3.3        | Center Tap Inductance                                                                                                                          | 96  |

|    | 5.4                    | Experi       | mental results                                                                                                                                 | 97  |

|    |                        | 5.4.1        | Supply and Ground Routing Inductances and Losses $\ \ \ldots \ \ldots \ \ .$                                                                   | 99  |

|    | 5.5                    | Conclu       | sion                                                                                                                                           | 100 |

| 6  | Con                    | clusion      | 1                                                                                                                                              | 107 |

|    | 6.1                    | Thesis       | Outcome                                                                                                                                        | 107 |

|    | 6.2                    | Sugges       | tion for Future Works                                                                                                                          | 109 |

| Li | $\operatorname{st}$ of | Public       | eations                                                                                                                                        | 111 |

| Sυ | ımma                   | ary          |                                                                                                                                                | 113 |

| Sa | men                    | vatting      |                                                                                                                                                | 115 |

| Li | ${ m st}$ of           | Figure       | es                                                                                                                                             | 119 |

| Contents         | iii |

|------------------|-----|

| List of Tables   | 123 |

| Acknowledgment   | 125 |

| About the Author | 127 |

#### CHAPTER

# 1

#### Introduction

The steadily increasing growth of cellular and wireless communications motivates researchers to keep on improving the system performance, overcome limitations and face new challenges. One of the key building blocks in a wireless radio is an RF oscillator, whose purity limits the radio performance. The oscillator's phase noise in a transmit chain results in power emissions into adjacent channels. In the receive chain, downconversion of a large interferer via the noisy local oscillator (LO) causes reciprocal mixing. Furthermore, in orthogonal frequency-division multiplexing (OFDM) systems, the phase noise leads to inter-carrier interference and a degradation in bit error rate. The trade-off between oscillator's phase noise and its power consumption introduce many challenges for oscillator designers.

Table 1.1 summarizes the frequency bands and the phase noise requirement specifications for some communication standards. GSM standard's phase noise requirements is the most stringent one. Lots of efforts in the literature is dedicated to improve the RF CMOS oscillator's thermal phase noise upconversion performances to meet such requirements. New classes of oscillation and multi core oscillators are introduced to fulfill this purpose [1]- [5] that we discuss about in Chapter 2. However, the efforts on reducing flicker noise upconversion in the oscillators are not as successful. The current solutions are sacrificing the thermal noise upconversion or sacrificing die area [6]- [8]. However,

2 Introduction

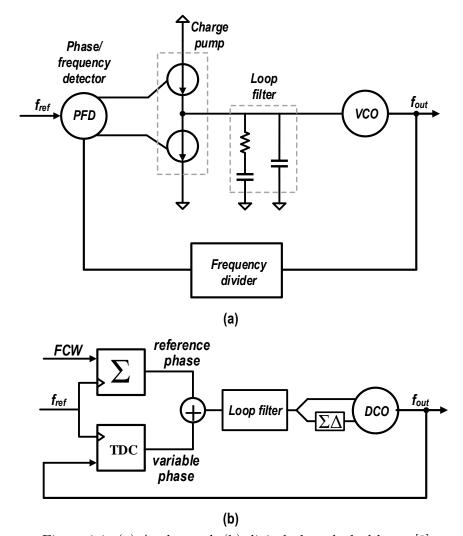

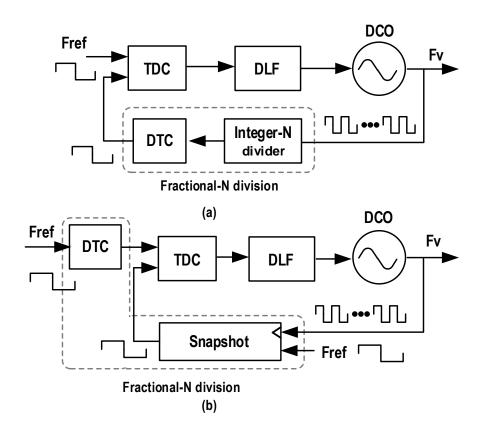

Figure 1.1: (a) Analog and; (b) digital phase locked loops [9].

since to achieve high frequency accuracy oscillators are incorporated in a phase lock loop (PLL) (as is shown in Fig. 1.1 for both analog and digital PLL), they can benefit from high pass nature of filtering of their noise by the loop. This reduction of the oscillator's low frequency noise in the synthesizer is highly dependent on the loop bandwidth. The loop bandwidth of the PLL is usually chosen to minimize the noise contribution of the frequency reference and charge pumps. However, if this bandwidth is less than the 1/f<sup>3</sup> corner of the oscillator then part of the oscillator's low frequency noise remains unfiltered.

Another challenge in the recent RF oscillator designers is to be able to design a wide tuning range oscillator while having low phase noise. The multi-standard applications that are the trend now demands for such oscillators. The trade-off between the quality factor of the switch capacitor bank that is tuning the LC oscillators and the oscillator's tuning range is the obstacle in wide tuning range oscillator design. The MOS transistor switch introduce a resistance that defines the switch capacitor bank quality factor in

1.1 Thesis Objectives 3

| Standard        | Frequency band (GHZ)                      | Required phase<br>noise (dBc/Hz)                 |

|-----------------|-------------------------------------------|--------------------------------------------------|

| Bluetooth       | 2.402-2.480                               | -84 @ 1 MHz<br>-114 @ 2 MHz<br>-129 @ 3 MHz      |

| GSM<br>900/1800 | 0.880-0.960<br>1.710-1.880                | -122 @ 0.6 MHz<br>-132 @ 1.6 MHz<br>-139 @ 3 MHz |

| UMTS            | 1.920-2.170<br>1.900-2.025                | -132 @ 3 MHz<br>-132 @ 10 MHz<br>-144 @ 15 MHz   |

| WiFi            | 2.412-2.472<br>5.150-5.350<br>5.470-5.825 | -102 @ 1 MHz<br>-125 @ 25 MHz                    |

Table 1.1: Communication standards requirements [10].

on-state, consequently a less resistance and so larger MOS transistor is required for phase noise considerations, However, in the off-state the series combination of the capacitor in the tank and the switch parasitic capacitances defines the equivalent tank capacitance. Consequently a smaller switch is preferred to increase the tuning range. This trade-off makes it impossible to meet both wide tuning range and low phase noise at the same time. For a moderate phase noise the tuning range of the oscillator can hardly go beyond 50% [11]. Some designers tried to switch inductors or transformers instead of the capacitors in order to increase tuning range, however the equivalent tanks Q-factor and consequently phase noise is degraded due to the switches in the signal path. Furthermore, due to the reduced oscillation voltage that is tolerable by the nano metric oxide thickness of advanced technologies CMOS process, low phase noise design is even more challenging.

#### 1.1 Thesis Objectives

The main objective of this dissertation is to address the requirements of RF CMOS oscillators in cellular applications. The first objective of this dissertation is to introduce a method to reduce the relatively high  $1/f^3$  PN upconversion of CMOS oscillators. Due to the trade-off between the synthesizer loop bandwidth and the incorporated oscillator's  $1/f^3$  noise, the cellular synthesizers with bandwidth of few hundred kHz cannot filter considerable amount of oscillator's low frequency noise. The introduced method reduces oscillator low frequency noise upconversion while not compromising die area or power consumption. The applicability of the method to different oscillator topologies allow the designer to choose the preferred topology and improve the low frequency noise

4 Introduction

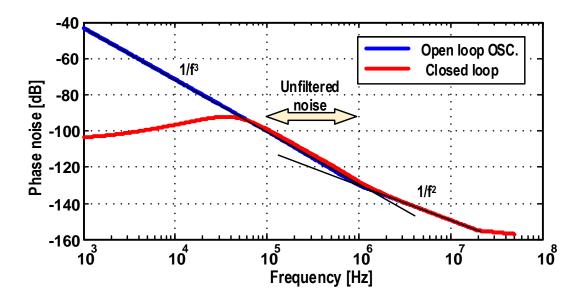

Figure 1.2: Oscillator's open loop and output frequency phase noise.

upconversion.

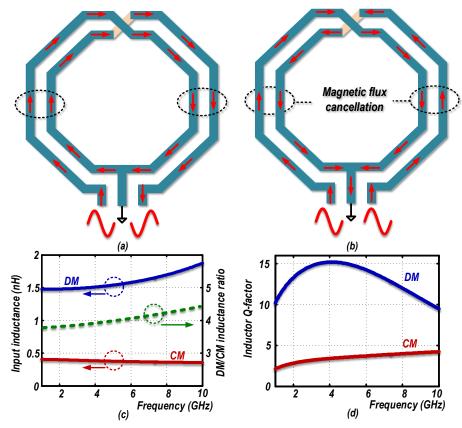

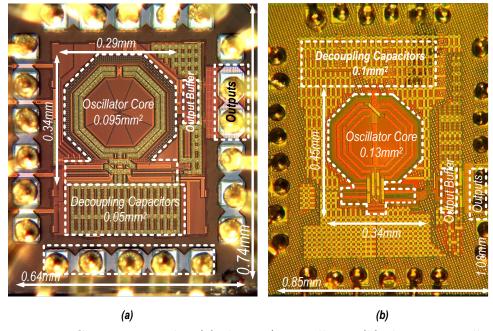

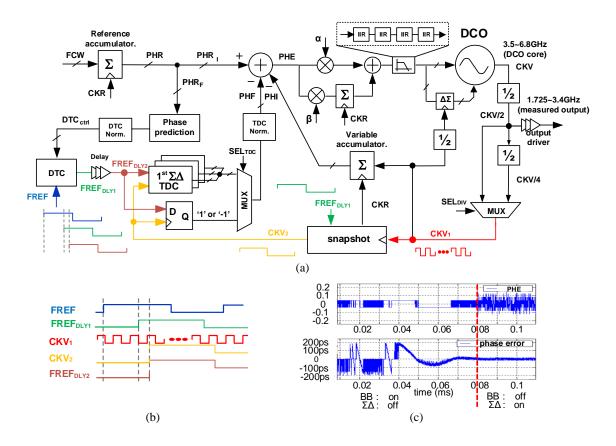

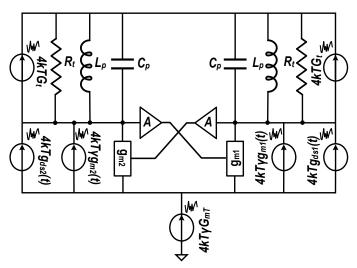

The second objective is to address the overgrowing interest in multi-standard communication devices by designing wide tuning range oscillators. The tradeoffs between tuning range, phase noise and area of mode switching oscillators are studied and one oscillator that shows promising tuning range-phase noise trade off is chosen to be incorporated in an all-digital PLL (ADPLL). Furthermore, we focused on optimizing die area of wide tuning range oscillators that seem to be missed in the literature. The ability of a transformer based tank to show different differential and common mode resonance frequencies are exploited to introduce a wide tuning range oscillator with a size of a conventional narrow tuning range oscillator for moderate phase noise applications.

#### 1.2 Thesis Outline

In Chapter 2 we briefly introduce and compare different LC oscillator structures. Then the thesis is divided in two parts. The first part in Chapter 3 elaborates a method to reduce a flicker (1/f) noise upconversion in voltage-biased RF oscillators. Excited by a harmonically rich tank current, a typical oscillation voltage waveform is observed to have asymmetric rise and fall times due to even-order current harmonics flowing into the capacitive part, as it presents the lowest impedance path. The asymmetric oscillation waveform results in an effective impulse sensitivity function (ISF) of a non-zero dc value,

1.2 Thesis Outline 5

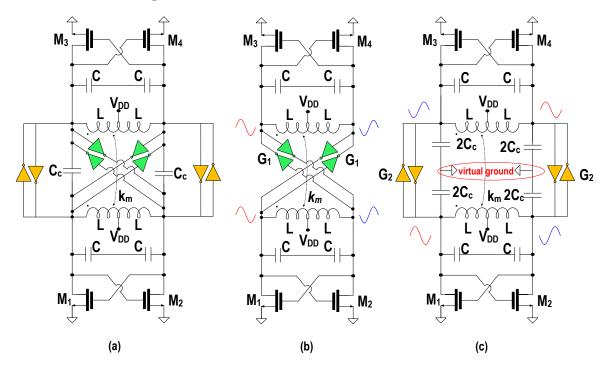

which facilitates the 1/f noise upconversion into the oscillator's  $1/f^3$  phase noise. If the  $\omega_0$  tank exhibits an auxiliary resonance at  $2\omega_0$ , then the oscillation waveform would be symmetric and the flicker noise upconversion would be largely suppressed. The second part of the thesis is focused on designing wide tuning range RF oscillators. In Chapter 4 a dual mode transformer based oscillator is designed. A digitally controlled oscillator (DCO) based on this design is incorporated in a digital to time converter (DTC)-assisted fractional-N wide-bandwidth ADPLL. This wide tuning range oscillator suffers from large die area. To tackle this problem specially in the applications that do not demand low phase noise oscillators another method to broaden a tuning range of an LC-tank oscillator without sacrificing its area is presented in Chapter 5. The extra tuning range is achieved by forcing a strongly coupled transformer-based tank into a common-mode resonance at a much higher frequency than in its main differential-mode oscillation. The oscillator employs separate active circuits to excite each mode but it shares the same tank, which largely dominates the core area but is on par with similar single-core designs.

Finally, Chapter 6 concludes this dissertation and presents suggestions for future developments.

6 Introduction

- [1] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2716–2729, Dec. 2008.

- [2] M. Babaie, and R. B. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [3] L. Fanori, and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [4] M. Babaie and R. B. Staszewski, "An ultra-low phase noise class-F<sub>2</sub> CMOS oscillator with 191 dBc/Hz FOM and long term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

- [5] S. A. R. Ahmadi-Mehr, M. Tohidian, and R. B. Staszewski, "Analysis and design of a multi-core oscillator for ultra-low phase noise," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 4, pp. 529–539, Sep. 2016.

- [6] S-J. Yun, C. Y. Cha, H. C. Choi, and S. G. Lee, "RF CMOS LC-oscillator with source damping resistors," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 9, pp. 511–513, Sep. 2006.

- [7] F. Pepe, A. Bonfanti, S. Levantino, C. Samori, and A. L. Lacaita, "Suppression of flicker noise up-conversion in a 65-nm CMOS VCO in the 3-to-3.6 GHz band," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2375–2389, Oct. 2013.

- [8] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

[9] R. B. Staszewski, "State-of-the-art and future directions of high-performance all-digital frequency synthesis in nanometer CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1497–1510, Jul. 2011.

- [10] F. Pepei, "Analysis and minimization of flicker noise up-conversion in radio-frequency LC-tuned oscillators" PhD dissertation

- [11] G. Li, L. Liu, Y. Tang, E. Afshari, "A low phase-noise wide tuning-range oscillator based on resonant mode switching," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp.1295-1308, June 2012.

#### CHAPTER

# 2

#### LC Oscillator Structures

#### 2.1 Introduction

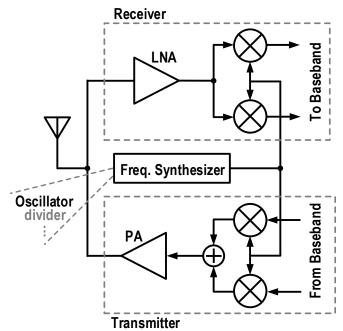

An oscillator is a key block used in both transmit and receive paths of a typical integrated transmitter/receiver (a.k.a., transceiver), see Fig. 2.1. Its spectral purity and efficiency highly affect the transceiver's performance. The phase noise of the oscillator results in reciprocal mixing in the receive path, where the blocker is mixed with the oscillator's phase noise and then can appear on top of the desired signal, thus degrading the receiver sensitivity [1]. This problem especially reveals itself in modern mobile phones that support 2G, 3G, 4G wireless standards as well as wireless connectivity (e.g., WiFi) standards with two or more very closely spaced antennas in one small handleld device [2]. It can also affect wideband CMOS receivers without off-chip SAW filters, in which powerful blockers can enter the IC without any prior attenuation [3].

In the transmit path, the oscillator phase noise gets amplified and can desensitize a nearby receiver [1]. Furthermore as one of the most power hungry blocks in the transceiver, its power consumption tends to limit the full system efficiency [2] [4]. Therefore, understanding and modeling the oscillator phase noise have been subjects of numerous studies [5]- [11]. A linear time-variant model through an impulse sensitivity function response of each noise source of the oscillator [9] is the most approached method since

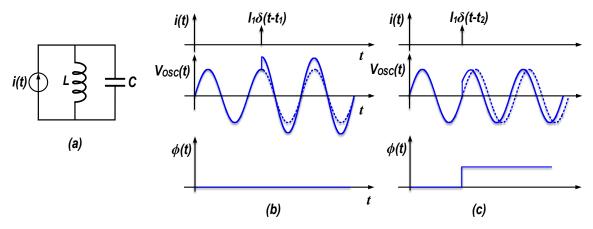

Figure 2.1: A generic RF transceiver [1].

its introduction. To understand this method, it should be noted that a current impulse injected to the tank of Fig. 2.2(a) can change the oscillating phase and/or amplitude depending of the injection time instant (see Fig. 2.2(b)-(c)). If the current impulse be injected when the oscillation waveform is at its maximum, oscillation amplitude will be disturbed but its phase will not. On the other hand, current impulses at zero crossings result in a minimum amplitude but maximum phase disturbance. The impulse response, however, is periodic with respect to the impulse injection time. The impulse sensitivity function (ISF),  $\Gamma(\omega_0\tau)$ , is a dimensionless, periodic function with period of  $2\pi$  that describes the oscillation phase shift from injected current impulses during the period [9]. ISF is a periodic function and consequently,

$$\Gamma(\omega_0 \tau) = \frac{c_0}{2} + \sum_{i=1}^{\infty} c_n \cos(n\omega_0 t + \theta_n). \tag{2.1}$$

Parasitic phase modulation is then obtained by convolving the current noise source with ISF as

$$\phi_n(t) = \frac{1}{q_{max}} \left[ \frac{c_0}{2} \int_{-\infty}^t i(\tau) + \sum_{i=1}^\infty c_n \int_{-\infty}^t i(\tau) \cos(n\omega_0 t + \theta_n) \right], \tag{2.2}$$

where,  $q_{max}$  is the maximum charge displacement at the capacitance of the node that the noise is injected.

For a current, such as  $i(t) = I_n \cos[(n\omega_0 + \Delta\omega)t]$ , the excess phase can be found as,

2.1 Introduction 11

Figure 2.2: Phase response to an impulse current [9].

$$\phi(t) \approx \frac{I_n c_n \sin(\Delta \omega)}{2q_{max} \Delta \omega}.$$

(2.3)

The modulated phase shows itself in the phase noise spectrum since we can write

$$x(t) = A\cos(\omega_0 t + \phi_n(t)) \approx A\cos(\omega_0(t)) - A\phi_n(t)\sin(\omega_0 t), \tag{2.4}$$

and, consequently, this injected current results in two sidebands at  $\omega_0 \pm \Delta \omega_0$  and  $\mathcal{L}(\Delta \omega) = 10 \log_{10} \left( \frac{I_n c_n}{4q_{max} \Delta \omega} \right)^2$ .

The same method can be generalized for random noise sources and with applying the Parseval's relation to derive the phase noise for a white power spectral density noise as

$$\mathcal{L}(\Delta\omega) = 10 \log_{10} \left( \frac{\frac{i_n^2}{\Delta f} \frac{1}{2\pi} \int_0^{2\pi} \Gamma^2(\phi) d\phi}{4q_{max}^2 \Delta\omega^2} \right)$$

(2.5)

The most accurate method to calculate ISF of each noise source is by simulation. An impulse current should be injected to a node in the circuit at a certain time. The time shift of the oscillation should be measured after a few cycles and be converted to the phase shift. By sweeping the injection time of the current impulse over one oscillation period, ISF can be measured.

If the application demands a low phase noise, an LC-tank-based oscillator is to be chosen. The thermal to phase-noise upconversion (20 dB/dec region) of these oscillators can be found as,

$$\mathcal{L}(\Delta\omega) = 10 \log_{10} \left( \frac{R_t kT}{2Q_t^2 V_{OSC}^2} \cdot F \cdot \left( \frac{\omega_0}{\Delta\omega} \right)^2 \right) = 10 \log_{10} \left( \frac{kT}{2Q_t^2 \alpha_I \alpha_V P_{DC}} \cdot F \cdot \left( \frac{\omega_0}{\Delta\omega} \right)^2 \right), \tag{2.6}$$

where,  $R_t$  is the equivalent parallel resistance of the tank, k is Boltzmann's constant, T is

the absolute temperature,  $\alpha_V = \frac{V_{osc}}{V_{DD}}$  and  $\alpha_I = \frac{I_{\omega_0}}{I_{DC}}$  are the voltage and current efficiency factors, and F is the noise factor and can be found as,

$$F = \sum_{i} \frac{R_t}{2kT} \cdot \frac{1}{2\pi} \int_0^{2\pi} \Gamma_i^2(\phi) \,\overline{i_{n,i}^2(\phi)} \,d\phi, \qquad (2.7)$$

in which  $\Gamma_i$  is the ISF of the  $i^{th}$  noise source.

#### 2.2 Class-B Oscillator Topology

The traditional class-B oscillator, shown in Fig. 2.3(a), has been widely used in RF applications due its simplicity and robustness. The noise factor in a class-B structure is ideally equal to  $\gamma + 1$  [11] if  $M_T$  tail current transistor would be an ideal current source. In this case, not only the current source does not contribute to phase noise but also provides an infinite impedance at the common source of the  $g_m$  transistors which, as we explain later, is beneficial for phase noise reduction. Let us investigate how the performance of this oscillator topology can be improved. The figure of merit (FoM) that is widely used for comparing oscillator performance is as

$$FoM = |PN| + 20\log_{10}(\omega_0/\Delta\omega) - 10\log_{10}(P_{DC}/1mW). \tag{2.8}$$

The objective is to reduce phase noise and/or power consumption of the oscillator.

Increasing the tank's quality factor, reduces the oscillator's phase noise. The tank's quality factor,  $Q_t$  depends on the both inductive and capacitive quality factors:

$$\frac{1}{Q_t} = \frac{1}{Q_L} + \frac{1}{Q_C} \tag{2.9}$$

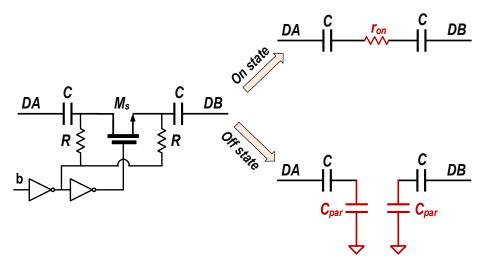

The inductor's quality factor,  $Q_L$ , which usually limits  $Q_t$ , is mostly technology dependent and does not improve with CMOS technology scaling. The capacitive quality factor,  $Q_C$ , on the other hand, depends on the tuning range of the oscillator. A switched-capacitor structure, shown in Fig. 2.4, is used nowadays to tune the oscillators. When  $M_s$  is on,  $C_{on} = \frac{C}{2}$ , and the switch on resistance,  $r_{on}$  defines  $Q_C = \frac{1}{2r_{on}C\omega}$ . To improve  $Q_c$ ,  $r_{on}$  should decrease and consequently  $M_s$  size should increase. However, larger  $M_s$ , adds to the parasitic capacitors and consequently increases the the switch capacitor equivalent capacitance when  $M_s$  is off:  $C_{off} = \frac{CC_{par}}{2(C + C_{par})}$ . Consequently,  $Q_t$  will be defined by the technology and oscillator's tuning range and is rarely a design parameter to improve phase noise.

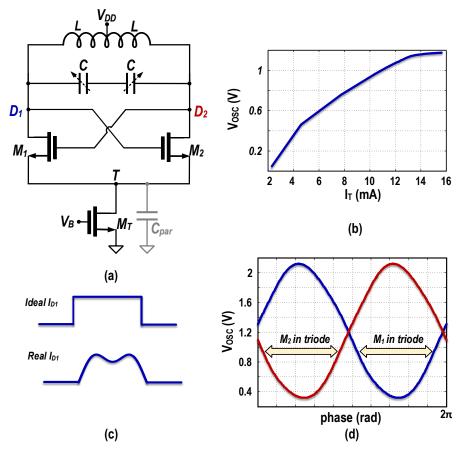

Figure 2.3: A class-B oscillator (a) schematic; (b) oscillation amplitude vs. tail current; (c) ideal and real drain current waveforms; (d) oscillation voltages waveforms.

Another approach to improve the oscillator's phase noise is reducing the tank's inductance while maintaining its quality factor. Doing so reduces  $R_t = L\omega Q_t$ ; however, it increases the power consumption  $P_{DC} = \frac{V_{OSC}^2}{\alpha_V \alpha_I R_t}$  at the same rate and so it keeps the FoM constant. Furthermore, by reducing the inductor size, the tank interconnection losses become more critical and at some point they limit its quality factor.

The class-B oscillator shows the best performance when its oscillation amplitude is around  $V_{DD}$  [13] [12] [25], and consequently  $\alpha_V = 1$ . After this point, for a typical oscillator with a tail current source  $M_T$ , the oscillation amplitude increase rate tapers off (see Fig. 2.3(b)) while its power consumption still increases linearly with the tail current, thus reducing FoM. The  $M_{1,2}$  transistors' drain current exhibits almost a square waveform when the tail current source is ideal and  $\alpha_I = \frac{2}{\pi}$  (see Fig. 2.3(c)). However, in a realistic scenario, the non-ideal current source brings up certain issues and limitations. First of all, the  $M_T$  transistor will contribute to the phase noise and increase the noise factor beyond  $1 + \gamma$ . The minimum tail node voltage,  $V_T$ , is also limited by the need to keep the  $M_T$  transistor in saturation; consequently the maximum oscillation voltage amplitude

Figure 2.4: The switched-capacitor tuning circuit in on and off states.

reduces to  $V_{DD}-V_{sat}$  and  $\alpha_V<1$  ( $\alpha_V\approx0.8$ ). The capacitance at node T tends to keep this node voltage at a constant level, consequently, for large oscillation amplitudes with  $M_{1,2}$  entering the triode region, the ideal square wave of  $M_{1,2}$  drain current experiences a dimple, as is shown in Fig. 2.3(c). As a result,  $\alpha_I$  drops from the ideal value of  $\frac{2}{\pi}$ , thus increasing the phase noise. On the other hand, when  $M_1$  or  $M_2$  transistors enter the triode region for a portion of the oscillation period, they will exhibit a low channel impedance. Furthermore, the equivalent parasitic capacitance at node T creates a low impedance path from T to ground. Therefore the tank finds a discharge path to the ground for the time that either one of these transistors are in the triode region; consequently, its quality factor drops, increasing the oscillators phase noise. The  $M_T$  transistor size is usually relatively large to reduce its flicker noise; consequently the parasitic capacitor at node T is large enough to provide such a low frequency path. However, it is also helpful in partially filtering the  $M_T$  transistor's thermal noise.

Various solutions have been proposed in the literature to improve phase noise of the class-B topology or to improve trade-offs between its phase noise and power consumption. Consequently, new classes of oscillation have been introduced. One of the most effective techniques that could improve the class-B considerably is a noise filtering technique [29]. In this technique,  $M_T$  thermal noise is filtered by a relatively large capacitor and a high impedance path is inserted between the core transistors and  $M_T$  to prevent the discharge path to the tank. Although this technique is very effective, since the high impedance path is realized by another resonator, it significantly increases the die area. Another interesting technique to improve the oscillator's phase noise is to couple N oscillator cores together [17]. This technique has been used in microwave circuits [18] and is also

Figure 2.5: (a) A class-C oscillator schematic; and (b) its voltages waveforms.

employed to improve phase noise in RF applications [19]. With coupling N cores, phase noise reduces by a factor of N while power consumption increases by the same factor. Consequently although the phase noise is reduced, the FoM remains the same. However, the die area is increased N times.

In the following sections we briefly review other oscillator topologies that attempt to improve their phase noise / power consumption trade off. In a class-C structure,  $M_{1,2}$  are biased in a way as to always remain in saturation during the whole oscillation period. In another strategy, the oscillation waveforms in class-D and class-F structures offer unique ISFs that prevent circuit noise from upconverting to phase noise.

#### 2.3 Class-C Oscillator Topology

The class-C structure [20] is shown in Fig. 2.5(a). In this class of operation the core transistor are kept in saturation, and consequently they show a high impedance during the entire oscillation period. The tank does not find a discharge path to the ground and its quality factor is thus preserved. This structure also saves 36% of the power consumption for the same phase noise by changing the square pulses of  $M_{1,2}$  drain current in the class-B operation to narrow and tall pulses with  $\alpha_I$ =1. To ensure the saturation region operation,  $M_{1,2}$  transistors' gates are decoupled from oscillation voltage and are biased to a value well below the  $V_{DD}$  voltage. A large capacitor in parallel with the  $M_T$  current source allows the class-C like tall and narrow current pulses for  $M_{1,2}$  transistors.

However, the maximum oscillation amplitude is limited in this topology. If the

Figure 2.6: (a) A class-C with dynamic generation of  $V_{bias}$  [22]; (b) a hybrid class-B/class-C oscillator [26].

oscillation amplitude gets large enough to push  $M_{1,2}$  into the triode region, not only the tank's quality factor would heavily drop due to the large  $C_T$ , but also  $M_{1,2}$  drain current will no longer feature tall and narrow pulses, thus  $\alpha_I$  would dramatically drop. Consequently, although the phase noise and power efficiency are improved for low oscillation amplitudes as compared to the class-B oscillator structure with the same amplitude, the minimum achievable phase noise here is limited. An attempt to increase the class-C swing is done by removing the current source transistor  $M_T$  and generating  $V_{bias}$  by an adaptable current mirror circuit [21]. This oscillator topology also suffers from a trade-off between its robust start-up and the maximum oscillation voltage in steady-state [22].  $V_{bias}$  should be relatively large to facilitate the start-up, but large  $V_{bias}$  values limit the steady state oscillation amplitude. It is proposed to adjust  $V_{bias}$  dynamically in a negative feedback loop [22] – [24], which consumes extra power (see Fig. 2.6(a)), or employ class-B switching transistors in parallel with the class-C ones to ensure start-up for low  $V_{bias}$  values [25] [26]. This reduces  $\alpha_I$  and consequently power efficiency (see Fig. 2.6(b)). The power efficiency of this structure has motivated designers in [27] to incorporate this oscillator topology in a Bluetooth Low Energy (BLE) transmitter.

#### 2.4 Class-D Oscillator Topology

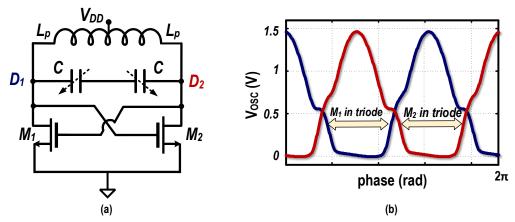

The schematic of a class-D oscillator topology is shown in Fig. 2.7(a). The tail transistor is removed, thus eliminating the overhead voltage necessary for its proper operation. Furthermore, the  $M_{1,2}$  transistor sizes are chosen large enough to become

Figure 2.7: (a) A class-D oscillator schematic; and (b) its voltages waveforms.

almost ideal switches. The relative oscillation voltage amplitude is maximized in this structure and reaches  $\sim 3V_{DD}$ . Doing so pushes  $M_{1,2}$  transistors deep into the triode region (even more than in the class-B structure) and, consequently, they generate considerable amount of noise. However, as demonstrated in Fig. 2.7(b), the oscillation voltages,  $V_1$  (at node  $D_1$ ) and  $V_2$  (at node  $D_2$ ), are forced to ground for almost half the period.  $V_1$  ( $V_2$ ) is mostly grounded when  $M_1$  ( $M_2$ ) is in the triode region, and consequently the ISF of node  $D_1$  ( $D_2$ ) is almost zero for most of this period, preventing the  $M_1$  ( $M_2$ ) noise to be upconverted to phase noise.

The idea of voltage-switching oscillators was first proposed in 1959 [28], but discrete BJT implementations have turned out not to be suitable for RF applications. However, recent CMOS technologies make excellent switches with reasonable sizes and, consequently, this structure has been attracting some interest [29]- [31]. A high oscillation amplitude in this structure makes it suitable for low-voltage low phase-noise applications [31] [32]. The product of drain current and drain voltage of MOS switches is almost zero across the oscillation period, consequently the power efficiency of this structure could be beyond 90% [30]. This oscillator structure not only can but it also must work at low voltage supplies, otherwise the  $M_{1,2}$  transistors, which should be thin-oxide devices to guarantee nearly ideal switching, will face breakdown. Another limitation of the class-D structure is its relatively severe low-frequency noise upconversion and supply frequency pushing. It has been attempted to minimize this problem by an on chip LDO in [33], which is rather power consuming. We elaborate on this problem in detail in Chapter 3 and propose a solution.

Figure 2.8: (a) Fundamental,  $V_{H1}$ ; (b)  $3^{\text{rd}}$  harmonic,  $V_{H3}$ , voltage components; (c) oscillation waveform; and (d) expected ISF. (e) Fundamental,  $V_{H1}$ ; (f)  $2^{\text{nd}}$  harmonic,  $V_{H2}$ , voltage components; (g) oscillation waveform; and (h) expected ISF.

### 2.5 Class-F Oscillator Topologies

If ISF of a certain oscillation waveform is negligible for some interval of an oscillation period, the circuit noise cannot be upconverted to phase noise during that time. This is beneficial in reducing the oscillator's phase noise. Class-F oscillators realize such oscillation waveforms by giving rise to either *third* or *second* harmonic of oscillation voltage, as we discuss in following sections.

Figure 2.9: (a) A transformer based tank class-F oscillator schematic; and (b) its voltages waveforms.

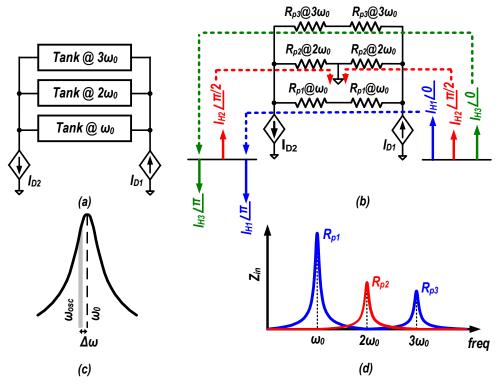

#### 2.5.1 Class- $F_3$ Topology

In this oscillator topology, a pseudo-square voltage oscillation waveform is realized by increasing the third harmonic component of the oscillation voltage and so the voltage ratio of the third harmonic to the fundamental is  $\frac{V_{H3}}{V_{H1}} \approx 0.3$  (see Fig.2.8(a)-(c)). This waveform has an ISF as shown in Fig.2.8(d), which prevents the circuit thermal-noise to phase-noise upconversion. Since the drain current in an oscillator is rich in harmonics, the voltage third harmonic could arise if we could realize another resonant peak at  $3\omega_0$  as an extra resonance to prevent filtering of the tank *current's* third harmonic component. An extra tank could be utilized for the  $3\omega_0$  resonance [34] [35]. However, although the phase noise performance of the oscillator improves, the extra tank is not area efficient. It is proposed in [6] to realize a tank with a transformer instead of an inductor. A transformer-based tank input impedance shows two resonant frequencies. The tank can be designed with the second resonant frequency to be at three times the fundamental resonance and consequently realize the pseudo-square oscillation waveform. This oscillator structure and waveforms are shown in Fig. 2.9(a). The  $M_{1,2}$  transistors in this structure spend more time in the triode region as compared to the class-B with sinusoidal oscillation waveform. Although the tank can find a discharge path to ground during this time span (see Fig. 2.9(b)), the very small ISF value there result in a reduced noise contribution of  $M_{1,2}$  to the total phase noise. Voltage efficiency  $\alpha_v$  of class-F<sub>3</sub> is about 0.8, which is similar to that in class-B, but the  $M_{1,2}$  drain currents are almost square-wave and current efficiency  $\alpha_I$  is very close to  $\frac{2}{\pi}$ . One drawback of this structure is that transformers have lower quality factor in the same technology as compared to an inductor with the same size. The promising phase noise performance of this structure has motivated the designers

Figure 2.10: (a) A transformer based tank class-F oscillator schematic; and (b) its voltages waveforms [38].

to incorporate this oscillator in a synthesizer for 4G phones [37].

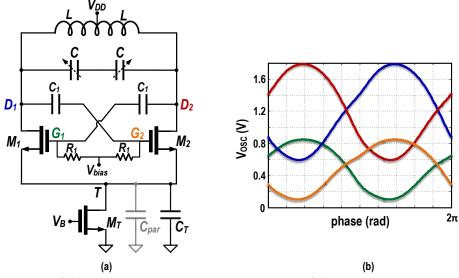

#### 2.5.2 Class-F<sub>2</sub> Topology

The time span that the core transistors are in the triode region is contributing most to the 20 dB/dec phase noise. Consequently, if the ISF were to be negligible in this time span, the phase noise would reduce (see Fig. 2.8(h)). The oscillation voltage of Fig. 2.8(g) offers such a waveform. As demonstrated in this figure, increasing the second harmonic component of the oscillation voltage with a  $\frac{V_{H2}}{V_{H1}} \approx 0.3$  constraint results in such a waveform (see Fig. 2.8(e)-(g)). As in the class-F<sub>3</sub> structure, an extra resonant peak, now at  $2\omega_0$ , prevents the current's second harmonic from being filtered and thus gives rise to a voltage harmonic component at  $2\omega_0$ . This waveform was realized in [38] with the help of two transformer-based tanks, as demonstrated in Fig. 2.10.  $\alpha_I$  is almost  $\frac{2}{\pi}$  in this structure and the tail transistor has more overhead with  $\alpha_V \approx 0.9$ . Furthermore, the tradeoff of power consumption and phase noise is improved by applying two 1:2-turn transformers, thus scaling down the equivalent resistance of the tank and oscillator's PN by a factor of 5. The drawback is, of course, the large area required to acommodate the two transformers.

2.6 Conclusion 21

#### 2.6 Conclusion

In this chapter, we briefly introduce various oscillator structures and mention their benefits and drawbacks. We overview nonidealities that the traditional class-B oscillator faces and review how each structure tries to overcome them. The class-C oscillator improves phase noise at a given power consumption but only when its oscillation amplitude is low enough to keep the core transistors in saturation. The class-D oscillator reaches low phase noise in the thermal noise region without requiring large supply voltages but it is limited in operation to low supply voltages due to reliability concerns. The class-F oscillators raise voltage harmonics to create waveforms with special ISFs that prevent circuit thermal noise to phase noise upconversion. However, they are more complex to design and need simultaneous tuning of two capacitor banks.

All these oscillator structures attempt to improve the thermal or 20 dB/dec phase noise. In the next chapter we introduce a method to reduce the low-frequency noise upconversion in LC oscillator structures.

- [1] B. Razavi, "A study of phase noise in CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 31, no. 3, pp. 331–343, Mar. 1996.

- [2] M. Mikhemar, D. Murphy, A. Mirzaei and H. Darabi, "A cancellation technique for reciprocal-mixing caused by phase noise and spurs," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3080–3089, Dec. 2013.

- [3] H. Wu, M. Mikhemar, D. Murphy, H. Darabi, and M. F. Chang, "A blocker-tolerant inductor-less wideband receiver with phase and thermal noise cancellation," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2948–3024, Dec. 2013.

- [4] J. Borremans et al., "A 40nm CMOS 0.4-6 GHz receiver resilient to out of band blockers," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1659–1671, Jul. 2011.

- [5] E. J. Baghdady, R. N. Lincoln, and B. D. Nelin, "Short-term frequency stability: Characterization, theory, and measurement," in *Proc. IEEE*, vol. 53, pp. 704–722, Jul. 1965.

- [6] L. S. Cutler and C. L. Searle, "Some aspects of the theory and measurement of frequency fluctuations in frequency standards," in *Proc. IEEE*, vol. 54, pp. 136–154, Feb. 1966.

- [7] D. B. Leeson, "A simple model of feedback oscillator noises spectrum," in *Proc. IEEE*, vol. 54, pp. 329–330, Feb. 1966.

- [8] J. Rutman, "Characterization of phase and frequency instabilities in precision frequency sources; Fifteen years of progress," in *Proc. IEEE*, vol. 66, pp. 1048–1174, Sept. 1978.

[9] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," IEEE J. Solid-State Circuits, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [10] A. Demir, A. Mehrotra, and J. Roychowdhury, "Phase noise in oscillators: a unifying theory and numerical methods for characterization," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 5, pp. 655–674, May 2000.

- [11] D. Murphy, J. J. Rael, and A. A. Abidi, "Phase noise in LC oscillators: A phasor-based analysis of a general result and of loaded Q," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 6, pp. 1187–1203, June 2010.

- [12] H. Darabi et al., "A quad band GSM/GPRS/EDGE SoC in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 870–882, Apr. 2011.

- [13] A. Hajimiri and T. Lee, "Design issues in CMOS differential LC oscillators," IEEE J. Solid-State Circuits, vol. 34, no. 5, pp. 717-724, May 1999.

- [14] J. Rael and A. Abidi, "Physical processes of phase noise in differential LC oscillators," in Proc. IEEE Custom Integr. Circuits Conf., Sept. 2000, pp. 569–572.

- [15] P. Andreani *et al.*, "A study of phase noise in Colpitts and LC-tank CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1107–1118, May 2005.

- [16] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

- [17] A. Hajimiri, "Distributed integrated circuits: An alternative approach to high-frequency design," *IEEE Commun. Mag.*, vol. 40, no. 2, pp. 168–173, Feb. 2002.

- [18] H. Chang, X. Cao, U. K. Mishra, and R. A. York, "Phase noise in coupled oscillators: Theory and experiment," *IEEE Trans. Microw. Theory Tech.*, vol. 45, no. 5, pp. 604–615, May 1997.

- [19] L. Roman, A. Bonfanti, S. Levantino, C. Samori, and A. L. Lacaita, "5-GHz oscillator array with reduced flicker up-conversion in 0.13-μm CMOS," *IEEE J. Solid-State* Circuits, vol. 41, no. 11, pp. 2457–2467, Nov. 2006.

- [20] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2716–2729, Dec. 2008.

[21] M. Tohidian, A. Fotowat-Ahmadi, M. Kamarei, and F. Ndagijimana, "High-swing class-C VCO," in *Proc. IEEE Eur. Solid-State Circuits Conf.*, Sep. 2011, pp. 495–498.

- [22] L. Fanori and P. Andreani, "Highly efficient class-C CMOS VCOs, including a comparison with class-B VCOs," *IEEE J. Solid-State Circuits*, vol. 48, no. 7, pp. 1730– 1740, Jul. 2013.

- [23] W. Deng, K. Okada, and A. Matsuzawa, "A feedback class-C VCO with robust startup condition over PVT variations and enhanced oscillation swing," in *IEEE Eur.* Solid-State Circuits Conf. (ESSCIRC), Sep. 2011, pp. 499–502.

- [24] J. Chen, F. Jonsson, M. Carlsson, C. Hedenas, and L. R. Zheng, "A low power, start-up ensured and constant amplitude class-C VCO in 0.18μm CMOS," IEEE Microw. Wireless Compon. Lett., vol. 21, no. 8, pp. 427–429, Aug. 2011.

- [25] K. Okada, Y. Nomiyana, R. Murakami, and A. Matsuzawa, "A 0.114 mW dual-conduction class-C CMOS VCO with 0.2 V power supply," in *Proc. IEEE Symp. Circuits*, Jun. 2009, pp. 228–229.

- [26] L. Fanori, A. Liscidini, and P. Andreani, "A 6.7-to-9.2 GHz 55 nm CMOS hybrid class-B/class-C cellular TX VCO," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2012, pp. 354–356.

- [27] C. Li and A. Liscidini, "Class-C PA-VCO cell for FSK and GFSK transmitters," IEEE J. Solid-State Circuits, vol. 51, no. 7, pp. 1537–1546, Jul. 2016.

- [28] P. Baxandall, "Transistor sine-wave LC oscillators. Some general considerations and new developments," *Proc. IEE-Part B: Electron. Commun. Eng.*, vol. 106, no. 16, pp. 748–758, May 1959.

- [29] L. Fanori and P. Andreani, "A 2.5-to-3.3GHz CMOS class-D VCO," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 346–347.

- [30] L. Fanori and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [31] A. G. Roy, S. Dey, J. B. Goins, T. S. Fiez, and K. Mayaram, "350 mV, 5 GHz class-D enhanced swing differential and quadrature VCOs in 65 nm CMOS," IEEE J. Solid-State Circuits, vol. 50, no. 8, pp. 1833–1447, Aug. 2015.

[32] Y. Yoshihara, H. Majima, and R. Fujimoto, "A 0.171 mW, 2.4 GHz class-D VCO with dynamic supply voltage control," in *IEEE Eur. Solid-State Circuits Conf. (ESSCIRC)*, 2014, pp. 339–342.

- [33] L. Fanori, T. Mattsson, and P. Andreani, "A class-D CMOS DCO with an on-chip LDO," in *IEEE Eur. Solid-State Circuits Conf. (ESSCIRC)*, 2014, pp. 335–338.

- [34] H. Kim, S. Ryu, Y. Chung, J. Choi, and B. Kim, "A low phase-noise CMOS VCO with harmonic tuned LC tank," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 7, pp. 2917–2923, Jul. 2006.

- [35] D. Manstretta and R. Castello, "An intuitive analysis of phase noise fundamental limits in LC oscillators", in *International Conference on Noise and Fluctuations* (ICNF), 2015.

- [36] M. Babaie, and R. B. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [37] F. W. Kuo, R. Chen, K. Yen, H. Y. Liao, C. P. Jou, F. L. Hsueh, M. Babaie, R. B. Staszewski, "A 12mW all-digital PLL based on class-F DCO for 4G phones in 28nm CMOS," in *Proceedings of IEEE VLSI Circuits Symposium*, 2014, pp. 1–2.

- [38] M. Babaie and R. B. Staszewski, "An ultra-low phase noise class-F2 CMOS oscillator with 191 dBc/Hz FOM and long term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

#### CHAPTER

# 3

# A 1/f Noise Up-Conversion Reduction Technique

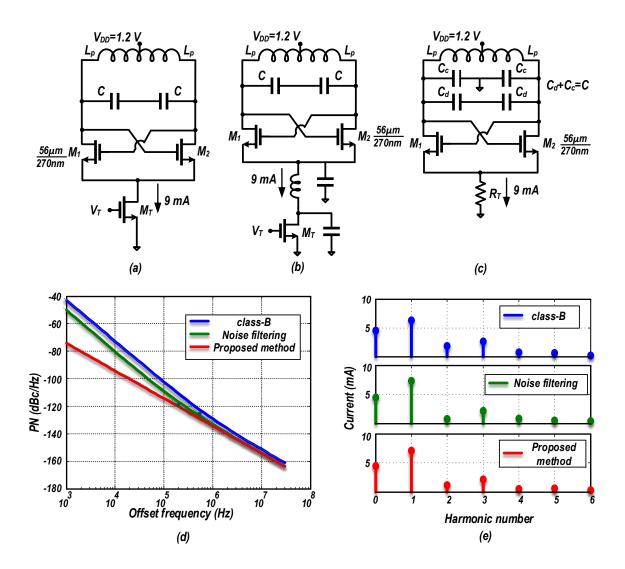

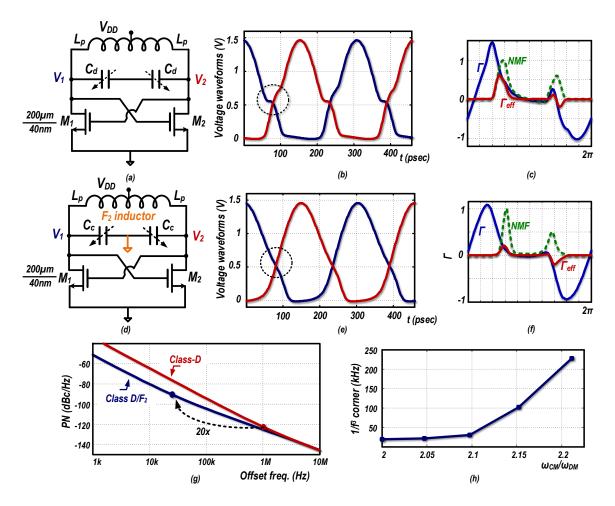

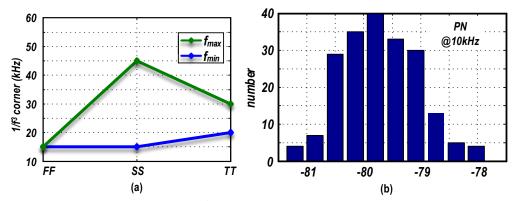

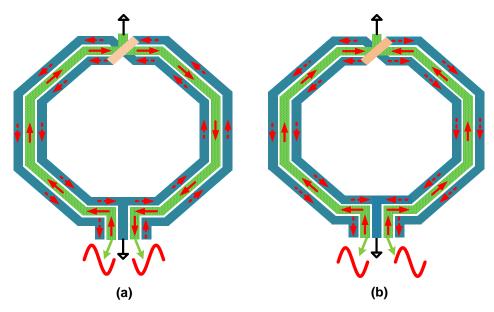

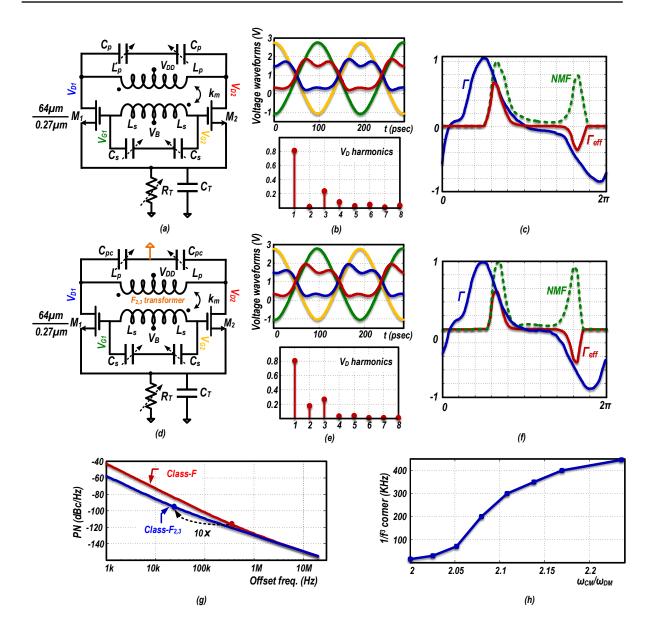

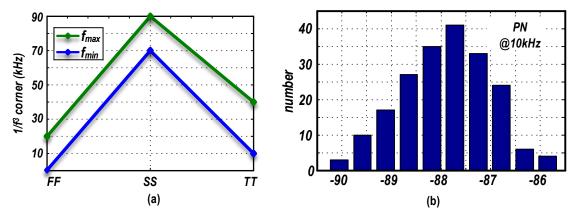

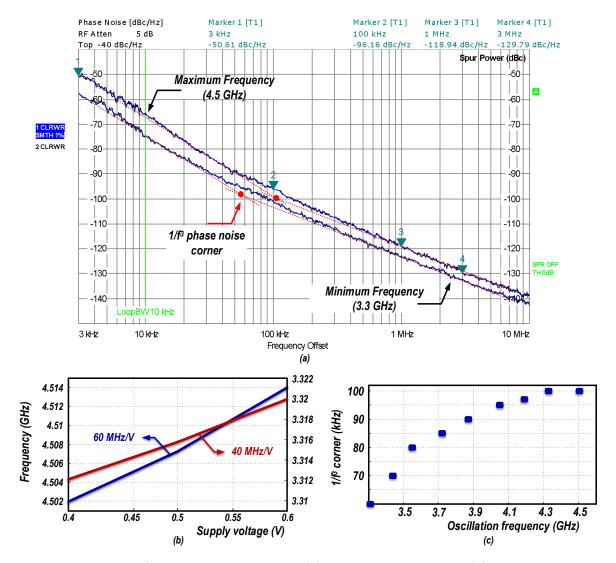

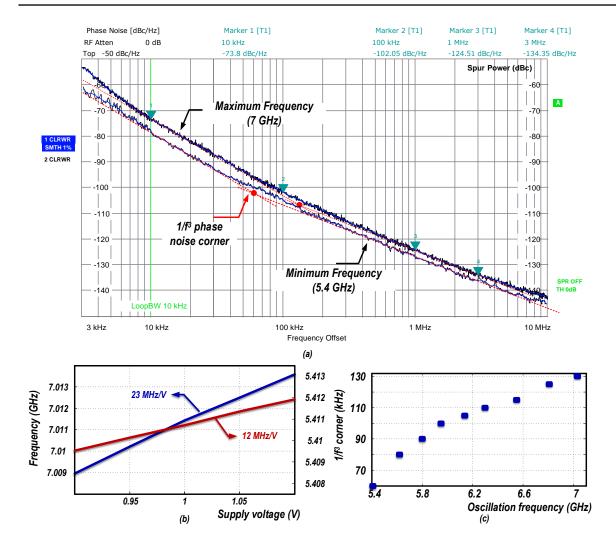

In this chapter, we introduce a method to reduce a flicker (1/f) noise upconversion in voltage-biased RF oscillators<sup>1</sup>. Excited by a harmonically rich tank current, a typical oscillation voltage waveform is observed to have asymmetric rise and fall times due to even-order current harmonics flowing into the capacitive part, as it presents the lowest impedance path. The asymmetric oscillation waveform results in an effective impulse sensitivity function (ISF) of a non-zero dc value, which facilitates the 1/f noise upconversion into the oscillator's  $1/f^3$  phase noise. We demonstrate that if the  $\omega_0$  tank exhibits an auxiliary resonance at  $2\omega_0$ , thereby forcing this current harmonic to flow into the equivalent resistance of the  $2\omega_0$  resonance, then the oscillation waveform would be symmetric and the flicker noise upconversion would be largely suppressed. The auxiliary resonance is realized at no extra silicon area in both inductor- and transformer-based tanks by exploiting different behavior of inductors and transformers in differential- and common-mode excitations. These tanks are ultimately employed in designing modified class-D and class-F oscillators in 40-nm CMOS technology. They exhibit an average flicker noise corner of less than 100 kHz.

<sup>&</sup>lt;sup>1</sup>Material of this chapter was published in IEEE Journal of Solid-State Circuits [1]

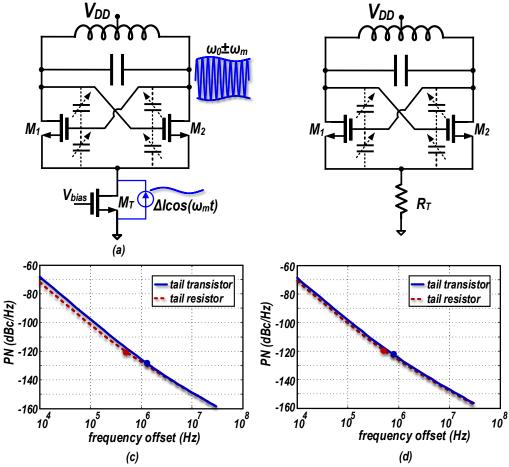

Figure 3.1: Class-B oscillator: (a) with tail transistor  $M_T$ ; (b) with tail resistor  $R_T$ ; and their PN when (c)  $M_T$  is always in saturation; (d)  $M_T$  enters partially into triode.

#### 3.1 Introduction

Close-in spectra of RF oscillators are degraded by a flicker (1/f) noise upconversion. The resulting low-frequency phase noise (PN) fluctuations can be mitigated as long as they fall within a loop bandwidth of an enclosing phase-locked loop (PLL). However, the PLL loop bandwidths in cellular transceivers are less than a few tenths to a few hundreds of kHz [2] [3], which is below the typical  $1/f^3$  PN corner of CMOS oscillators [4]- [6]. Consequently, a considerable amount of the oscillator's low frequency noise cannot be filtered by the loop and will adversely affect the transceiver operation. In a current-biased oscillator, flicker noise of a tail transistor,  $M_T$ , modulates the oscillation voltage amplitude and then upconverts to PN via an AM-PM conversion mechanism through nonlinear parasitic capacitances of active devices, varactors and switchable capacitors [7] [8] (see

3.1 Introduction 29

Fig.  $3.1(a).)^1$  An intuitive solution is to configure the oscillator into a *voltage-biased* regime, which involves removing the  $M_T$  [9], or replacing it with a tail resistor,  $R_T$ , in Fig. 3.1(b). Such expected reduction is highly dependent on the tail transistor's operating region. If  $M_T$  in Fig. 3.1(a) is always in saturation, the amount of 1/f noise is considerable and the tail resistor  $R_T$  in Fig. 3.1(b) could improve the low-frequency PN performance, as shown in Fig. 3.1(c), However, in advanced CMOS process nodes with a reduced supply voltage,  $M_T$  partially enters the triode region, thereby degrading the oscillator's effective noise factor but improving the 1/f noise upconversion, see Fig. 3.1(d). In [4], class-C oscillators were designed with a tail transistor and a tail resistor. Measured  $1/f^3$  corners are almost the same, thus supporting our discussion. However, regardless of the  $M_T$  operating region, removing this source would still not completely eliminate the 1/f noise upconversion.

Another mechanism of the 1/f upconversion is due to Groszkowski effect [10]. In a harmonically rich tank current, the fundamental component,  $I_{H1}$ , flows into the equivalent parallel resistance of the tank,  $R_p$ . Other components, however, mainly take the capacitive path due to their lower impedance, see Fig. 3.2(a). Compared to the case with only the fundamental component, the capacitive reactive energy increases by the higher harmonics flowing into them. This phenomenon makes the tank's reactive energy un-balanced. The oscillation frequency will shift down from the tank's natural resonance frequency,  $\omega_0$ , in order to increase the inductive reactive energy, and restore the energy equilibrium of the tank. This frequency shift is given by [11]

$$\frac{\Delta\omega}{\omega_0} = -\frac{1}{Q^2} \sum_{n=2}^{\infty} \frac{n^2}{n^2 - 1} \cdot \left| \frac{I_{Hn}}{I_{H1}} \right|^2$$

(3.1)

where,  $I_{Hn}$  is the  $n^{th}$  harmonic component of the tank's current. The literature suggests that this shift is static but any fluctuation in  $I_{Hn}/I_{H1}$  due to the 1/f noise modulates  $\Delta\omega$  and exhibits itself as 1/f<sup>3</sup> PN [12], see Fig. 3.2(c). Although this mechanism has been known for quite some time, it is still not well understood how the flicker noise modifies the  $I_{Hn}/I_{H1}$  ratio. Furthermore, (3.1) suggests all harmonics indiscriminately modulate the Groszkowski's frequency shift by roughly the same amount, without regard to their odd/even-mode nature, which could be easily misinterpreted during the study of the flicker noise upconversion in cross-coupled oscillators.

While recognizing the Groszkowski's frequency shift as the dominant physical mechanism in voltage-biased oscillators, we turn our attention to the impulse sensitivity function

<sup>&</sup>lt;sup>1</sup>It is shown in [7] that for certain values of varactor bias voltages this upconversion is almost eliminated.

Figure 3.2: (a) Current harmonics paths; (b) drain current in time and frequency domains; (c) frequency drift due to Groszkowski effect.

(ISF) theory in researching the above questions. Hajimiri and Lee [13] have shown that upconversion of any flicker noise source depends on the dc value of the related effective ISF, which can be significantly reduced if the waveform has certain symmetry properties [13] [14]. Another explanation was offered in [27] [16] suggesting that if the 1/f noise current of a switching MOS transistor is to be modeled by a product of stationary noise and a periodic function w(t) then this noise can upconvert to PN if w(t) is asymmetric.

In this chapter, we elaborate on a method proposed in [22] to effectively trap the second current harmonic into a resistive path of a tank in a *voltage-biased* oscillator topology. Doing so will reduce the core transistors' low frequency noise upconversion by making the oscillation waveform symmetric and reducing the effective ISF dc value. We further investigate the effects of harmonics on the core transistors' flicker noise upconversion by studying their impact on the oscillation waveform and on the effective impulse sensitivity

function,  $\Gamma_{eff,dc}$ .

It should be mentioned that several solutions are proposed in literature to reduce the 1/f noise upconversion due to Groszkowski's frequency shift. The concept of a harmonically rich tank current degrading the close-in oscillator spectrum has been noticed for quite some time; however, the proposed solutions mostly include linearization of the system to reduce the level of current harmonics by limiting the oscillation amplitude by an AGC [17] [18], or linearization of gm-devices [19] [20], at the expense of the oscillator's start-up margin and increased  $1/f^2$  PN. In a completely different strategy, a resistor is added in [21] in series with gm-device drains. An optimum value of the resistor minimizes the flicker noise upconversion; however, the 1/f noise improvement is at the expense of the  $20 \, dB/dec$  degradation in oscillators with low  $V_{DD}$  and high current consumption.

The chapter is organized as follows: Section 3.2 shows how harmonic components of the drain current contribute to the flicker noise upconversion and shows how an auxiliary CM resonance at  $2\omega_0$  mitigates this upconversion. Section 3.3 demonstrates how the auxiliary resonance is realized and proves the effectiveness of the proposed method by implementing two classes of voltage-biased oscillators. Section 3.4 reveals the details of circuit implementations and measurement results.

#### 3.2 Method to Reduce 1/f Noise Up-Conversion

#### 3.2.1 Auxiliary Resonant Frequencies

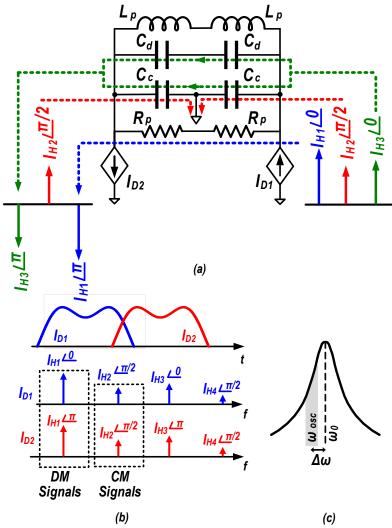

Let us start by focusing on reducing the Groszkowski frequency shift. As shown in Fig. 3.2(a), the oscillation frequency  $\omega_{osc}$  fluctuates around the tank's natural resonant frequency  $\omega_0$  due to the flow of higher harmonics of the current  $I_{D1,2}$  into the capacitive part of the tank. A voltage-biased class-B tank current in time and frequency domains is shown in Fig. 3.2(b). Odd harmonics of the tank current are differential mode (DM) signals, hence, they can flow into both differential- and single-ended capacitors. Even harmonics of the tank current, on the other hand, are common mode (CM) signals, and can only flow into single-ended (SE) capacitors. If the tank possesses further resonances coinciding with these higher harmonics (see Fig. 3.3(a)), these components can find their respective resistive path to flow into, as shown in Fig. 3.3(b). Consequently, the capacitive reactive energy would not be disturbed and the oscillation frequency shift  $\Delta\omega$  would be minimized (see Fig. 3.3(c)). The input impedance  $Z_{in}$  of such a tank is shown in Fig. 3.3(d). The tank has the fundamental natural resonant frequency at  $\omega_0$  and auxiliary CM and DM resonant frequencies at even and odd-order harmonics, respectively.

Figure 3.3: (a) Auxiliary resonances at higher harmonics; (b) current harmonic paths; (c) frequency drift; (d) input impedance of the tank.

Minimizing the frequency shift  $\Delta\omega$  will weaken the underlying mechanism of the 1/f noise upconversion; however realizing auxiliary resonances at higher harmonics has typically been area inefficient and can also degrade the PN performance. Consequently, the auxiliary resonance frequencies have to be chosen wisely. Groszkowski frequency shift formula (3.1) indicates that all the contributing current harmonics  $I_{Hn}$  are weighted by almost the same coefficients. This means that, in practice, stronger current harmonics  $I_{Hn}$  contribute more to the frequency shift. Consequently, we can narrow down the required auxiliary resonances to these harmonics. On the other hand, ultimately, the low frequency noise upconversion depends on the oscillation waveform and the dc value of effective ISF. The various current harmonics contribute unevenly to the flicker noise upconversion since they result in different oscillation waveforms and effective ISF values. Investigating these differences reveals how many and at which frequencies the auxiliary resonances should be realized.

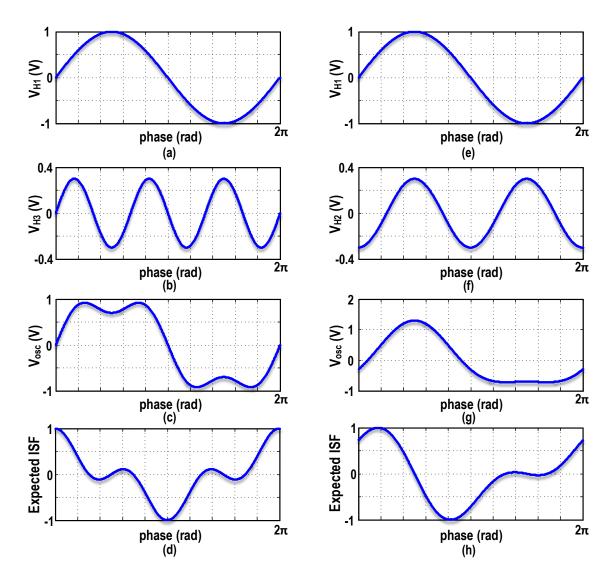

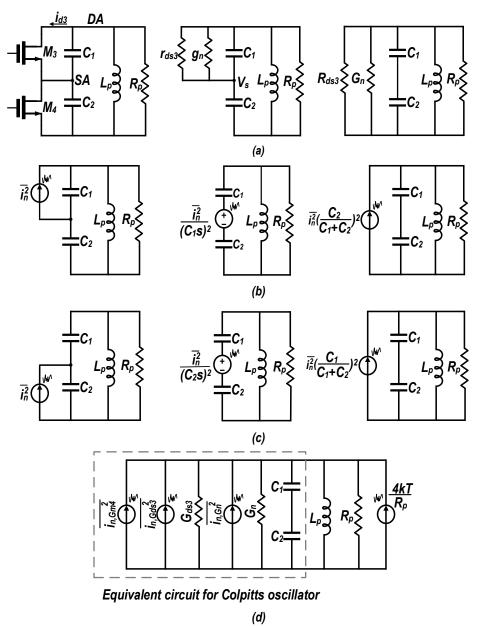

#### 3.2.2 Harmonic Effects on the Effective ISF

A (hypothetical) sinusoidal resonance tank current  $I_{H1}(t) = |I_{H1}|\sin(\omega_0 t)$  would result in a sinusoidal resonance oscillation voltage:  $V_{H1}(t) = R_{p1} \cdot |I_{H1}|\sin(\omega_0 t) = A_1\sin(\omega_0 t)$ .

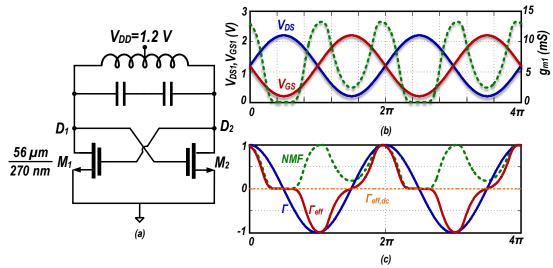

Figure 3.4: Oscillator example: (a) schematic; (b)  $V_{DS}$ ,  $V_{GS}$ , and  $g_m$  of  $M_1$  transistor when oscillation voltage contains only fundamental component; (c) its ISF, NMF, and effective ISF.

Its ISF is also a zero-mean sinusoid but in quadrature with  $V_{H1}(t)$  [23]. The flicker noise of core transistors (e.g.,  $M_{1,2}$  in Fig. 3.4(a)) in a cross-coupled oscillator, is modeled by a current source between the source and drain terminals, and exhibits a power spectral density as

$$\overline{i_n^2(t)} = \frac{K}{WLC_{ox}} \cdot \frac{1}{f} \cdot g_m^2(\omega_0 t)$$

(3.2)

where, K is a process-dependent constant, W and L are core transistors' width and length, respectively, and  $C_{ox}$  is an oxide capacitance per area. Due to the dependency of current noise on  $g_m$ , the flicker noise source is a cyclostationary process and can be expressed as

$$i_n(t) = i_{n0}(\omega_0 t) \cdot \alpha(\omega_0 t), \tag{3.3}$$

in which  $i_{n,0}(\omega_0 t)$  shows the stochastic stationarity.  $\alpha(\omega_0 t)$  is the noise modulating function (NMF), which is normalized, deterministic and periodic with maximum of 1. It describes the noise amplitude modulation; consequently it should be derived from the cyclostationary noise characteristics [13]. In this case, an *effective* impulse sensitivity function is defined as  $\Gamma_{eff}(\omega_0 t) = \alpha(\omega_0 t) \cdot \Gamma(\omega_0 t)$ .  $M_{1,2}$  flicker noise cannot up-convert to PN if effective ISF has a zero dc value.

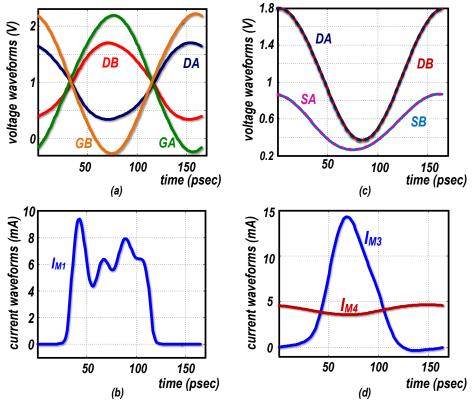

Let us investigate the  $M_{1,2}$  flicker noise upconversion when the oscillation voltage ideally contains only the fundamental component. In Fig. 3.4(a),  $V_{D1} = V_{DD} - A_1 sin(\omega_0 t)$ ,  $V_{G1} = V_{D2} = V_{DD} + A_1 sin(\omega_0 t)$ . Assuming  $V_{DD} = 1.2 \text{ V}$ , and  $A_1 = 1 \text{ V}$ , the  $g_m$  of the  $M_1$  transistor under such  $V_{DS}$  and  $V_{GS}$  is found by simulations and is shown as dotted line in Fig. 3.4(b). Under this condition,  $\alpha(\omega_0 t) = \frac{g_m(\omega_0 t)}{g_{m,max}}$ . ISF, NMF and the effective ISF of

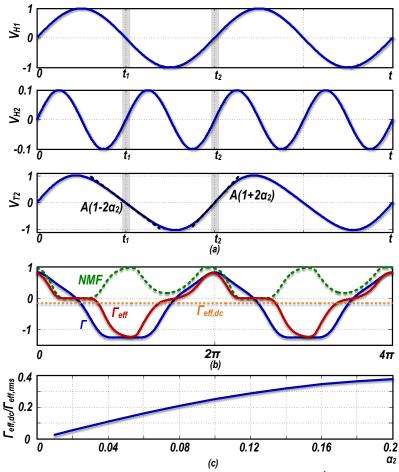

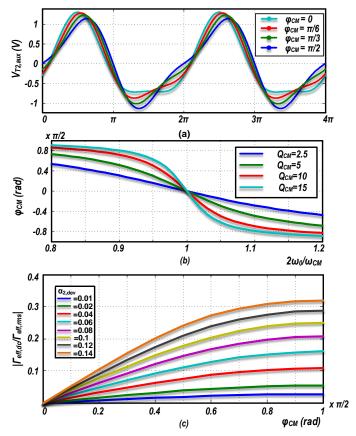

Figure 3.5: Conventional tank waveforms: (a) fundamental,  $V_{H1}$ ,  $2^{\rm nd}$  harmonic,  $V_{H2}$ , voltage components and oscillation waveform,  $V_{T2}$ ; (b) its ISF, NMF and effective ISF; (c)  $\Gamma_{eff,dc}/\Gamma_{eff,rms}$  for different  $\alpha_2$  values.

the  $M_1$  flicker noise source are shown in Fig. 3.4(c). The dc value of such an effective ISF is zero, resulting in no flicker noise up-conversion. This is a well known-conclusion and is referred to as a state where  $M_{1,2}$  transistors' flicker noise cannot upconverted to PN [16].

In reality, the tank current of voltage-biased oscillators is rich in harmonics. Due to physical circuit constraints, the even-order current harmonics lead by  $\pi/2$ , while the odd-order current harmonics are in-phase with the fundamental current  $I_{H1}$ . The  $\pi/2$  phase difference in even and odd-order current harmonics considerably changes the oscillation waveforms characteristics. For simplicity, we focus only on dominant harmonics,  $I_{H2}=|I_{H2}|\sin(2\omega_0t+\pi/2)$  and  $I_{H3}=|I_{H3}|\sin(3\omega_0t)$ , as representatives of even and odd-order current harmonics, respectively; however, the following discussion can be easily generalized for all harmonics. We also assume for now that the tank only contains SE capacitors.

The differential current  $I_{H2}$  flows into the SE capacitors and creates a  $2^{\rm nd}$ -order voltage harmonic:

$$V_{H2}(t) = \frac{1}{C \cdot 2\omega_0} \cdot |I_{H2}| \sin(2\omega_0 t + \pi/2 - \pi/2) = \alpha_2 A_1 \sin(2\omega_0 t)$$

(3.4)

where, the  $-\pi/2$  phase shift is due to the capacitive load. The oscillation voltage will then be

$$V_{T2}(t) = V_{H1}(t) + V_{H2}(t) = A_1 \left[ \sin \left( \omega_0 t \right) + \alpha_2 \sin \left( 2\omega_0 t \right) \right]$$

(3.5)

$V_{H1}(t)$ ,  $V_{H2}(t)$  and  $V_{T2}(t)$  are plotted in Fig. 3.5 (a) for  $\alpha_2$ =0.1 and  $A_1$ =1 V.  $V_{H1}(t)$  has two zero-crossings within its period: at  $t_1$  and  $t_2$ , and their rise and fall times are symmetric with derivatives:  $V'_{H1}(t_1) = -V'_{H1}(t_2)$ .  $V_{H2}$ 's zero-crossings are also at  $t_1$  and  $t_2$ ; however  $V'_{H2}(t_1) = V'_{H2}(t_2)$ . Consequently, the opposite slope polarities of  $V_{H1}$  and  $V_{H2}$  at  $t_1$  slow the fall time of  $V_{T2}$  while the same slope polarities at  $t_2$  sharpen its rise time. Consequently, as can be gathered from 3.5 (a),  $V_{T2}$  features asymmetric rise and fall slopes.

The resulting ISF of the gm transistor is calculated based on (36) in Ref. [13] and is shown in Fig. 3.5 (b), with its mean dependent on  $\alpha_2$ . Larger  $\alpha_2$  leads to more asymmetry between  $V_{T2}(t)$  rise and fall slopes, hence  $\Gamma_{eff,dc}$  will increase. Furthermore, repeating the same simulations to obtain  $g_{m1}$  with drain and gate voltages that contain  $2^{nd}$  harmonic components results in asymmetric  $g_{m1}$  and consequently NMF. The slower rise/fall times increase the duration when  $M_1$  is turned on, thus widening  $g_{m1}$ . A sharper rise/fall time decrease the amount of time when  $M_1$  is turned on, resulting in a narrower  $g_{m1}$ . The NMF and effective ISF of such waveforms are shown in Fig. 3.5 (b). The effective ISF has a dc value which results in  $M_{1,2}$ 's flicker to PN up-conversion. Dependency of the dc value of the effective ISF on  $\alpha_2$  is shown in Fig. 3.5 (c).

This argument is valid for all even-order current harmonics, and we can conclude that the fluctuations in the even harmonics of the tank's current convert to the  $1/f^3$  PN noise through the modulation of the oscillating waveform.

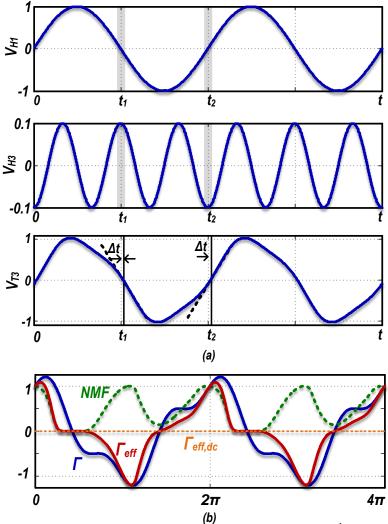

Let us now investigate a case of the tank current containing only odd-harmonic components, with  $I_{H3} = |I_{H3}|\sin(3\omega_0 t)$  as a representative.  $I_{H3}$  flows mainly into the tank capacitors and creates a 3<sup>rd</sup> harmonic voltage as

$$V_{H3}(t) = \frac{1}{C \cdot 3\omega_0} \cdot |I_{H3}| \sin(3\omega_0 t - \pi/2) = \alpha_3 A_1 \sin(3\omega_0 t - \pi/2)$$

(3.6)

where, again, the  $-\pi/2$  phase shift is due to the capacitive load. The oscillation voltage will then be

$$V_{T3}(t) = V_{H1}(t) + V_{H3}(t) = A_1 \left[ \sin(\omega_0 t) + \alpha_3 \sin(3\omega_0 t - \pi/2) \right]$$

(3.7)

$V_{H1}(t)$ ,  $V_{H3}(t)$  and  $V_{T3}(t)$  are plotted in Fig. 3.6 (d) for  $\alpha_3$ =0.1 and  $A_1$ =1 V. It is obvious that the oscillation waveform falling and rising slopes are symmetric, and  $\Gamma_{dc} = 0$ , as

Figure 3.6: Conventional tank waveforms: (a) fundamental,  $V_{H1}$ ,  $3^{\rm rd}$  harmonic,  $V_{H3}$ , voltage component and oscillation waveform,  $V_{T3}$ ; (b) its ISF, NMF and effective ISF.

easily gathered from Fig. 3.6 (e). The simulations show that  $g_{m1}$  is slightly asymmetric due to amplitude distortion of the oscillation voltage. However this asymmetry is canceled out when multiplied by ISF (see Fig. 3.6 (e)), resulting in an effective ISF with almost zero dc value and thus preventing low-frequency noise up-conversion. These arguments can be generalized for all odd-order harmonics. Consequently, the low-frequency noise of gm transistors does not upconvert to PN if the tank current only contains odd harmonics.

To further support that 1/f noise upconverts more to PN if  $\alpha_2$  is increased we tried to run some simulations on the voltage biased class-B oscillator of Fig. 3.7(a). Controlling the second-harmonic current is not very straightforward. It can be modified by changing the core transistors' width, W, or by changing tank's quality factor, Q. In both of these methods, the oscillation waveform amplitude would get affected. If we fix the oscillation amplitude when W or Q are swept, the second harmonic power modification

Figure 3.7: (a) Voltage biased class-B oscillator schematics (b)  $1/f^3$  corner vs. $I_{H2}/I_{Hn}$ .

range becomes very limited. On the other hand, by changing the transistors' width, the flicker noise of the device also changes and adds another parameter. Consequently, in the following simulations we swept the tank quality factor and all the other parameters, such as transistor sizes, supply voltage, etc., are kept the same. With higher Q, the oscillation voltage increases, the device spends more time in triode region and becomes more non-linear, consequently generating more current harmonics.  $M_1$  and  $M_2$  in the class-B oscillator are thick-oxide  $56\mu/270$ n devices,  $V_{DD}=1.2V$ ,  $R_T=9$  Ohm. The capacitors are ideal and not tunable. The simulation results are shown in Fig. Fig. 3.7(b). As we have discussed it, the flicker noise up-conversion depends on the  $\alpha_2$  value, which is proportional to the  $I_{H2}/I_{Hn}$  ratio. Therefore, we reported the  $1/f^3$  corner vs.  $I_{H2}/I_{Hn}$  , and it is obvious from Fig. 3.7(b) that the corner increases for larger  $I_{H2}/I_{Hn}$  ratios in this class-B oscillator.

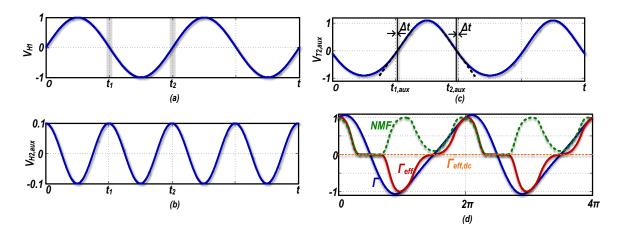

#### 3.2.3 Resonant Frequency at $2\omega_0$

Thus far, we have shown that the even components of the tank's current are chiefly accountable for the asymmetric oscillation waveform and the 1/f noise upconversion to PN. Let us investigate what happens to the oscillation waveform and effective ISF if the tank has an auxiliary CM resonance at  $2\omega_0$ . Such resonance provides a resistive (i.e., via  $R_{p2}$ ) path for  $I_{H2}$  to flow into it and hence the voltage  $2^{\text{nd}}$  harmonic component is

$$V_{H2,aux}(t) = R_{p2}|I_{H2}|\sin(2\omega_0 t + \pi/2) = A_1 \alpha_{2,aux}\sin(2\omega_0 t + \pi/2)$$

(3.8)

The composite oscillation voltage will become

$$V_{T2,aux}(t) = V_{H1}(t) + V_{H2,aux}(t) = A_1 \left[ \sin(\omega_0 t) + \alpha_{2,aux} \sin(2\omega_0 t + \pi/2) \right]$$

(3.9)

Figure 3.8: Proposed tank waveforms: (a) fundamental voltage component,  $V_{H1}$ ; (b) voltage 2<sup>nd</sup> harmonic in presence of auxiliary resonance,  $V_{H2,aux}$ ; (c) oscillation waveform,  $V_{T2,aux}$ ; (d) its ISF, NMF and effective ISF.

$V_{H1}(t)$ ,  $V_{H2,aux}(t)$  and  $V_{T2,aux}(t)$  are plotted in Fig. 3.8(a),(b),(c) for  $\alpha_{2,aux}=0.1$  and  $A_1=1$ . The rise and fall times of the oscillation voltage are now symmetric (see Fig. 3.8(c)) and so the ISF is zero mean, as shown in Fig. 3.8(d).  $g_{m1}$ , and thus NMF, are also completely symmetrical; consequently the effective ISF has a zero dc value, preventing low-frequency noise from being up-converted. The oscillation waveform is still dependent on  $\alpha_{2,aux}$ , but the rise and fall times are always symmetric, thus keeping  $\Gamma_{eff,dc}$  zero.

The second and third current harmonics are the most dominant in all classes of oscillators, so  $\alpha_2$  and  $\alpha_3$  are significantly larger than other  $\alpha_n$  for  $n=4,5,\ldots$  Meanwhile,  $\Gamma_{dc}$  is a growing function of  $\alpha_n$  for n=2k, where  $k=1,2,\ldots$  We can, therefore, conclude that  $I_{H2}$  is the main contributor to the 1/f noise upconversion. Consequently, attention to only one auxiliary resonant frequency at  $2\omega_0$  appears sufficient [22] [24].

#### 3.2.4 $\omega_{CM}$ Deviation from $2\omega_0$

The balance in the rise and fall zero-crossing slopes in Fig. 3.8(c) is rooted in the  $\pi/2$  phase shift between  $V_{H1}(t)$  and  $V_{H2}(t)$ . This is a combination of the  $\pi/2$  phase difference between  $I_{H1}(t)$  and  $I_{H2}(t)$ , and zero phase of the resistive tank impedance at  $2\omega_0$ . When  $\omega_{CM}$  deviates from  $2\omega_0$

$$V_{T2,aux}(t) = V_{H1}(t) + V_{H2,aux}(t) = R_{p1}|I_{H1}|\sin(\omega_0 t) + |Z_{CM}| \cdot |I_{H2}|\sin(2\omega_0 t + \pi/2 + \phi_{CM})$$

$$= A_1 \left[\sin(\omega_0 t) + \alpha_{2,aux}\sin(2\omega_0 t + \pi/2 + \phi_{CM})\right]$$

(3.10)

where,  $|Z_{CM}|$  and  $\phi_{CM}$  are the CM input impedance magnitude and phase, respectively, derived as,

Figure 3.9: (a)  $V_{T2,aux}$  for different  $\phi_{CM}$ ; (b)  $\phi_{CM}$  for different  $Q_{CM}$  when  $\omega_{CM}$  deviates from  $2\omega_0$ ; (c)  $\Gamma_{eff,dc}/\Gamma_{eff,rms}$  for different  $\alpha_{2,aux}$  and  $\phi_{CM}$ .

$$\phi_{CM} = \arctan\left(\frac{1-\zeta^2}{\frac{\zeta}{Q_{CM}}}\right) \tag{3.11}$$

$$|Z_{CM}| = R_{p2} \cdot \frac{\frac{\zeta}{Q_{CM}}}{\sqrt{(1-\zeta^2)^2 + (\frac{\zeta}{Q_{CM}})^2}}$$

(3.12)

where  $\zeta = \frac{2\omega_0}{\omega_{CM}}$ . The  $\omega_{CM}$  vs.  $2\omega_0$  misalignment has two effects. The first directly translates  $\phi_{CM}$  into the waveform asymmetry. Figure 3.9(a) shows  $V_{T2,aux}(t)$  for different  $\phi_{CM}$ ;  $\alpha_{2,aux}$  was chosen 0.3 to better illustrate the asymmetry. When grossly mistuned from  $2\omega_0$ ,  $\phi_{CM}$  could approach  $\pm \pi/2$ , thus making the auxiliary resonance completely ineffective. A larger Q-factor of the common-mode resonance,  $Q_{CM}$ , results in  $\phi_{CM}$  closer to  $\pm \pi/2$  for the same  $2\omega_0/\omega_{CM}$  ratios, as illustrated in Fig. 3.9(b).

The second effect is due to  $\alpha_{2,aux}$ , which determines the amount of second harmonic in the voltage waveform. When  $\phi_{CM}$  is not zero,  $\Gamma_{eff,dc}$  becomes dependent on  $\alpha_{2,aux}$ : The larger  $\alpha_{2,aux}$ , the more asymmetric waveform and more 1/f noise upconversion. The  $\alpha_{2,aux}$  value can be found from the following equation

Figure 3.10: (a) A tank with DM and CM resonances; (b)  $1/f^3$  corner of the oscillator employing this tank; (c)  $\phi_{CM}$ ; and (d)  $\alpha_{2,aux}$  of the tank vs.  $\omega_{CM}/\omega_{DM}$ .

$$\alpha_{2,aux} = \left| \frac{I_{H2}}{I_{H1}} \right| \cdot \frac{|Z_{CM}|}{R_{p1}}$$

(3.13)

$I_{H2}/I_{H1}$  is dependent on the oscillator's topology. Furthermore, the larger  $Q_{CM}$ , the larger  $R_{p2}$  and hence the larger  $\alpha_{2,aux}$ . Figure 3.9(c) shows the expected  $\Gamma_{eff,dc}/\Gamma_{eff,rms}$  vs.  $\phi_{CM}$  for different  $\alpha_{2,aux}$ . Both of these effects point out that  $Q_{CM}$  should be low to reduce the sensitivity of this method to the  $\omega_{CM}$  deviation from  $2\omega_0$ .

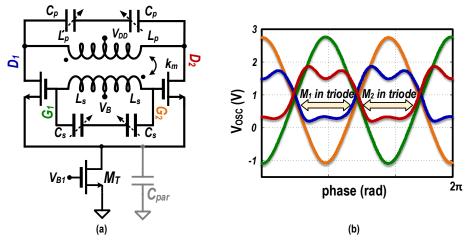

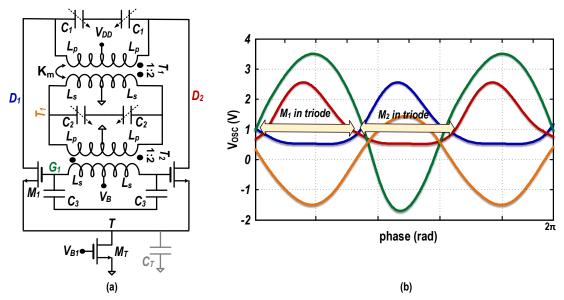

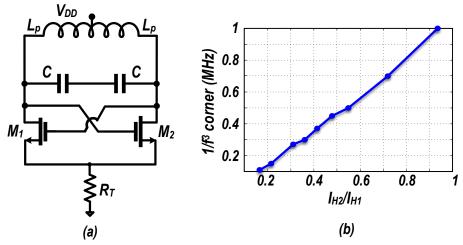

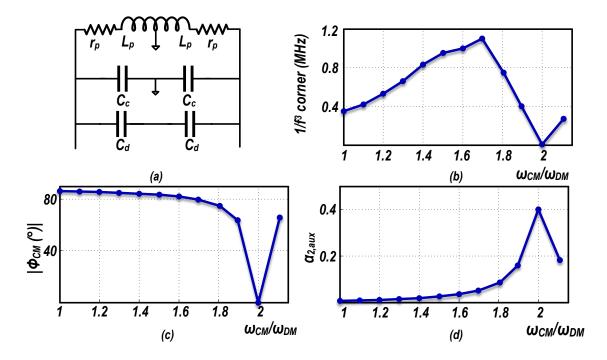

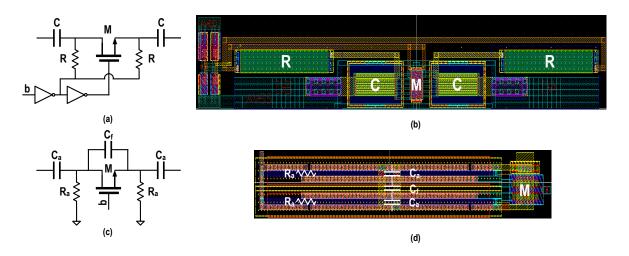

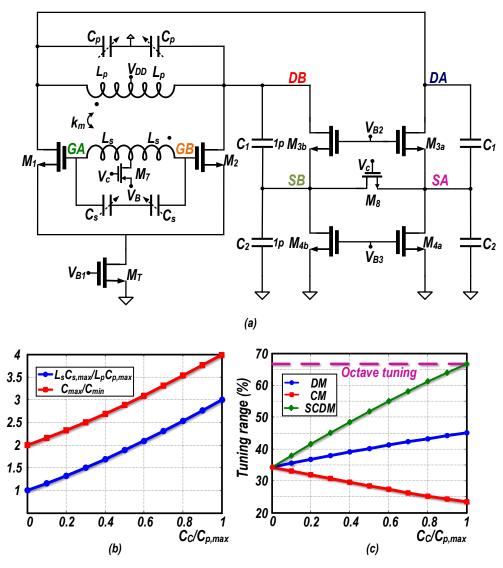

#### 3.3 Circuit Implementation

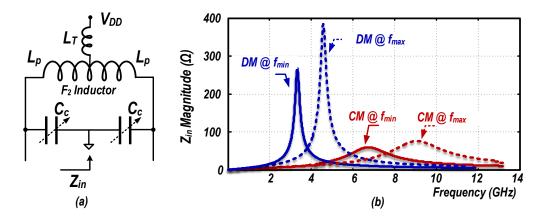

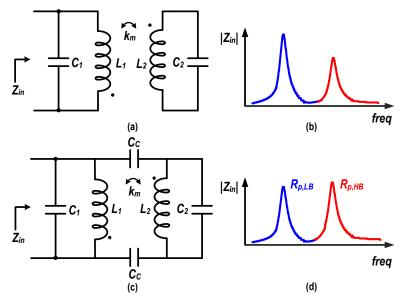

We have shown that if the tank demonstrates an auxiliary CM resonance at the 2<sup>nd</sup> harmonic of its fundamental  $\omega_0$  resonance, the oscillation waveform would be symmetric and, hence, the flicker noise upconversion would be suppressed. Since the differential capacitors are not seen by the CM signals (i.e.,  $I_{H2}$ ), a straightforward solution for realizing a CM peak is to design a tank as demonstrated in Fig. 3.10(a)) with a set of differential  $C_d$  and single-ended (SE)  $C_c$  capacitors [24].  $r_p$  is the equivalent series resistance of the inductor and it is assumed all capacitors are nearly ideal. This tank shows a fundamental DM resonant frequency,  $\omega_{DM} = \frac{1}{\sqrt{L_p(C_c + C_d)}}$  and a CM resonant

frequency  $\omega_{CM} = \frac{1}{\sqrt{L_p C_c}}$ . From (3.11)–(3.13):

$$\phi_{CM} = \arctan\left(\frac{1 - \frac{4C_c}{C_c + C_d}}{\frac{1}{Q_{DM}} \cdot \frac{2C_c}{C_c + C_d}}\right)$$

(3.14)

$$\alpha_{2,aux} = \frac{R_{p2}}{R_{p1}} \cdot \frac{\frac{2}{Q_{DM}} \cdot \left(\frac{C_c}{C_c + C_d}\right)}{\sqrt{\left(1 - \frac{4C_c}{C_c + C_d}\right)^2 + \left(\frac{2}{Q_{DM}} \cdot \frac{C_c}{C_c + C_d}\right)^2}} \cdot \frac{I_{H2}}{I_{H1}}$$

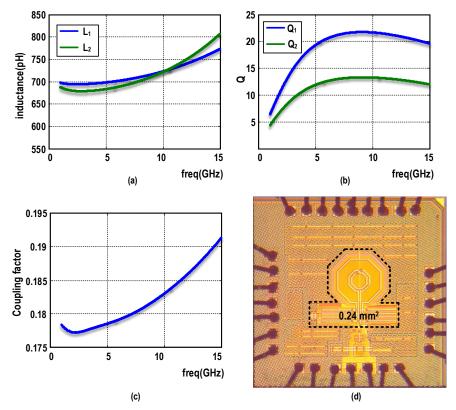

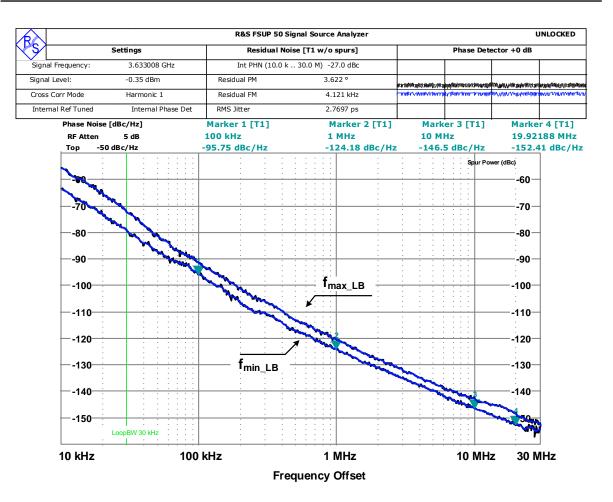

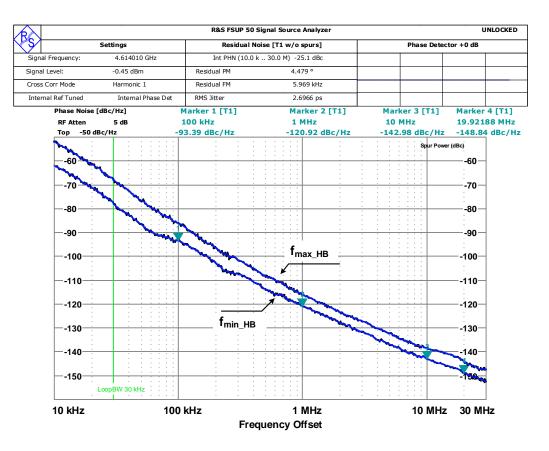

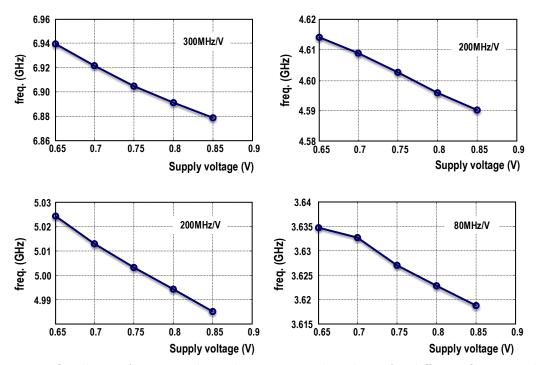

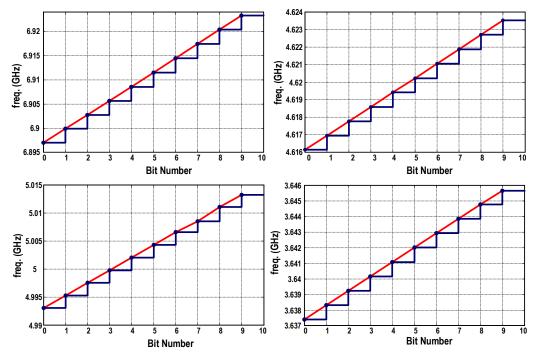

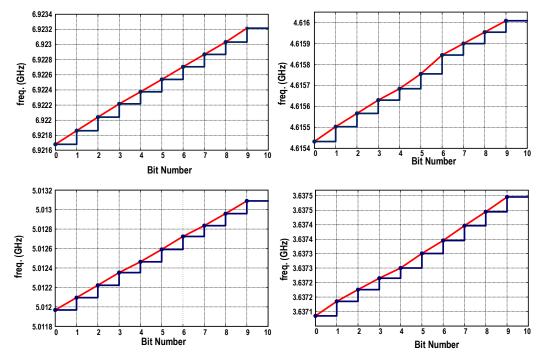

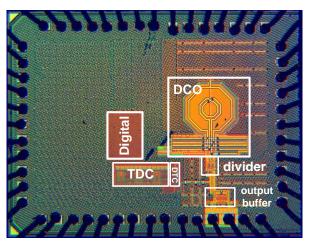

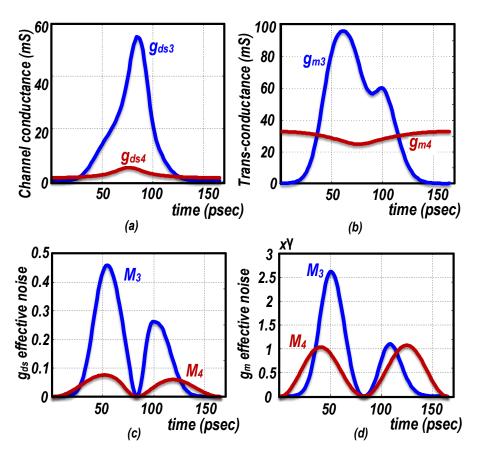

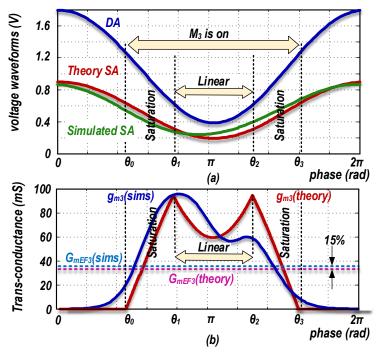

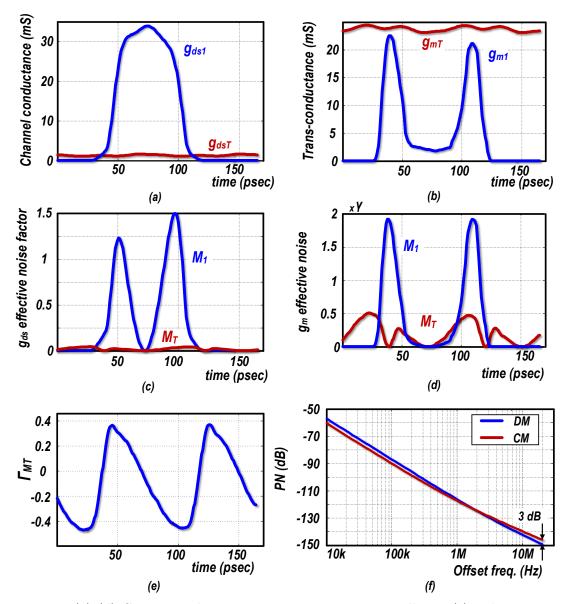

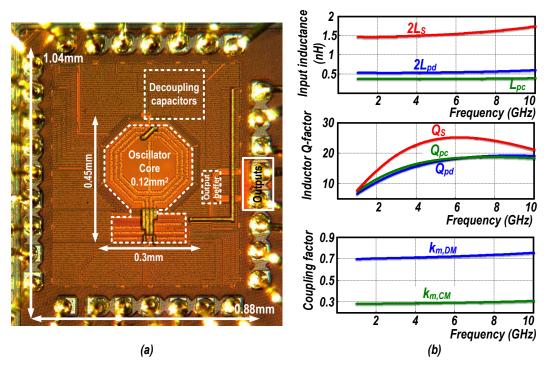

(3.15) where,  $Q_{DM}$ ,  $R_{p2}$  and  $R_{p1}$  are, respectively, the quality factor at DM resonance, and